标题:Analysis of 1.2 kV SiC SWITCH-MOS after Short-circuit Stress

摘要

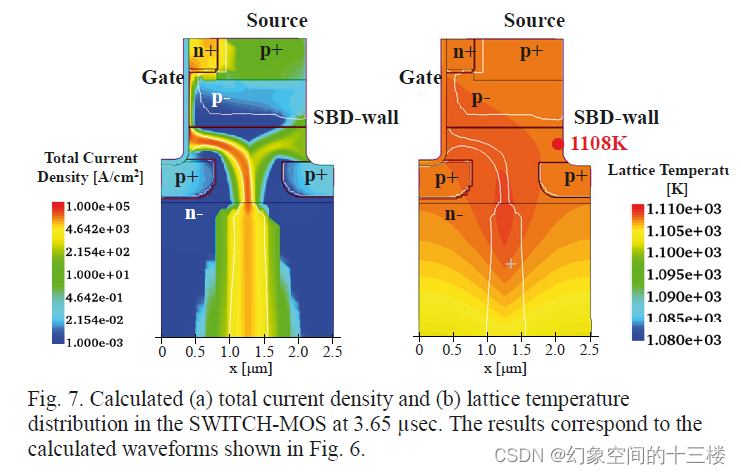

本研究调查了在短路应力后1.2 kV SWITCH-MOS的残余损伤。在应力施加后,相当于SWITCH-MOS耐受时间的约80%,正向阻断状态下的漏电流急剧增加。发现SWITCH-MOS中的SBD区域在短路应力期间受到高温晶格的影响,超过肖特基金属层的制造温度,这意味着SBD区域可能会受到物理损坏。

关键词:碳化硅;SWITCH-MOS;短路应力;SBD区域的残余损伤;漏极-源极漏电流

文章研究了什么

- 短路应力后1.2 kV SiC SWITCH-MOS的残余损伤。

- 短路应力对SWITCH-MOS正向阻断状态下的漏电流和ID-VGS特性的影响。

- 短路应力对SWITCH-MOS中的SBD(肖特基势垒二极管)区域的影响,由于高温晶格温度超过肖特基金属层的制造温度,SBD区域可能会受到物理损坏。

- 需要检测短路状态并在极短的时间内安全关闭设备,以防止损坏。

- 短路应力前后SWITCH-MOS的ID-VGS特性和正向阻断特性的比较。

- 由于短路应力期间的高温和高电场,SiC沟槽型MOSFET中栅极氧化层失效的可能性。

- 由于短路应力期间的高温,肖特基界面特性的变化和肖特基势垒高度(PhB)的降低。

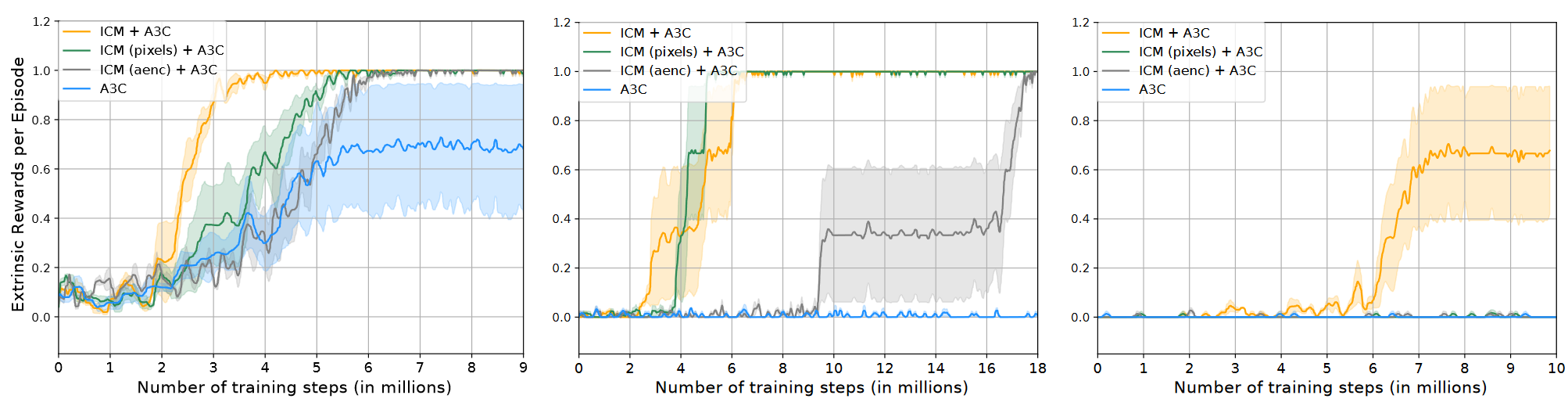

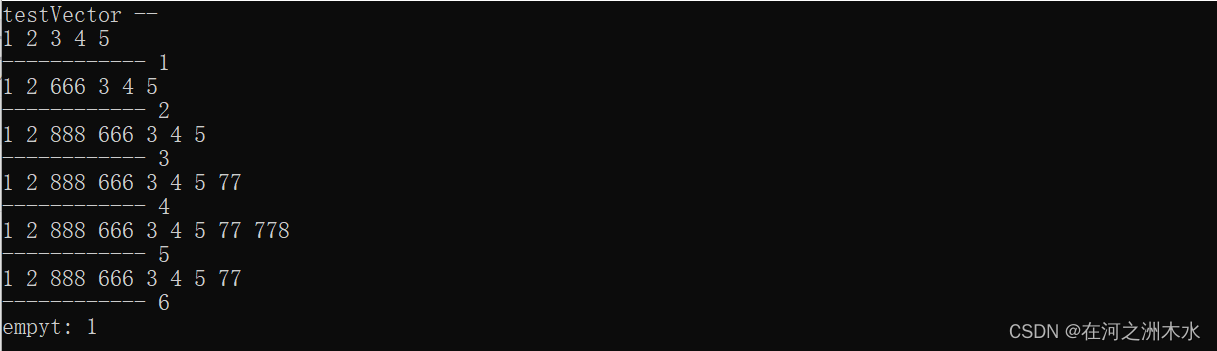

TCAD仿真结果表明,在短路应力期间,SBD区域的漏电流较大,晶格温度较高。

文章的创新点

- 调查了短路应力后1.2 kV SiC SWITCH-MOS的残余损伤。

- 确定了短路应力对SWITCH-MOS正向阻断状态下的漏电流和ID-VGS特性的影响。

- 认识到由于高温晶格温度超过肖特基金属层的制造温度,SWITCH-MOS中的SBD区域可能会受到物理损坏。

- 强调了在极短的时间内检测短路状态并安全关闭设备以防止损坏的必要性。

- 比较了带有和不带有嵌入式沟槽SBD的SWITCH-MOS的测量特性,为SBD区域在观察到的变化中的作用提供了见解。

- 估计了短路应力后的肖特基势垒高度(PhB),表明由于高温导致势垒高度降低。

- TCAD仿真结果表明,在短路应力期间,SBD区域的漏电流较大,晶格温度较高。

文章的研究方法

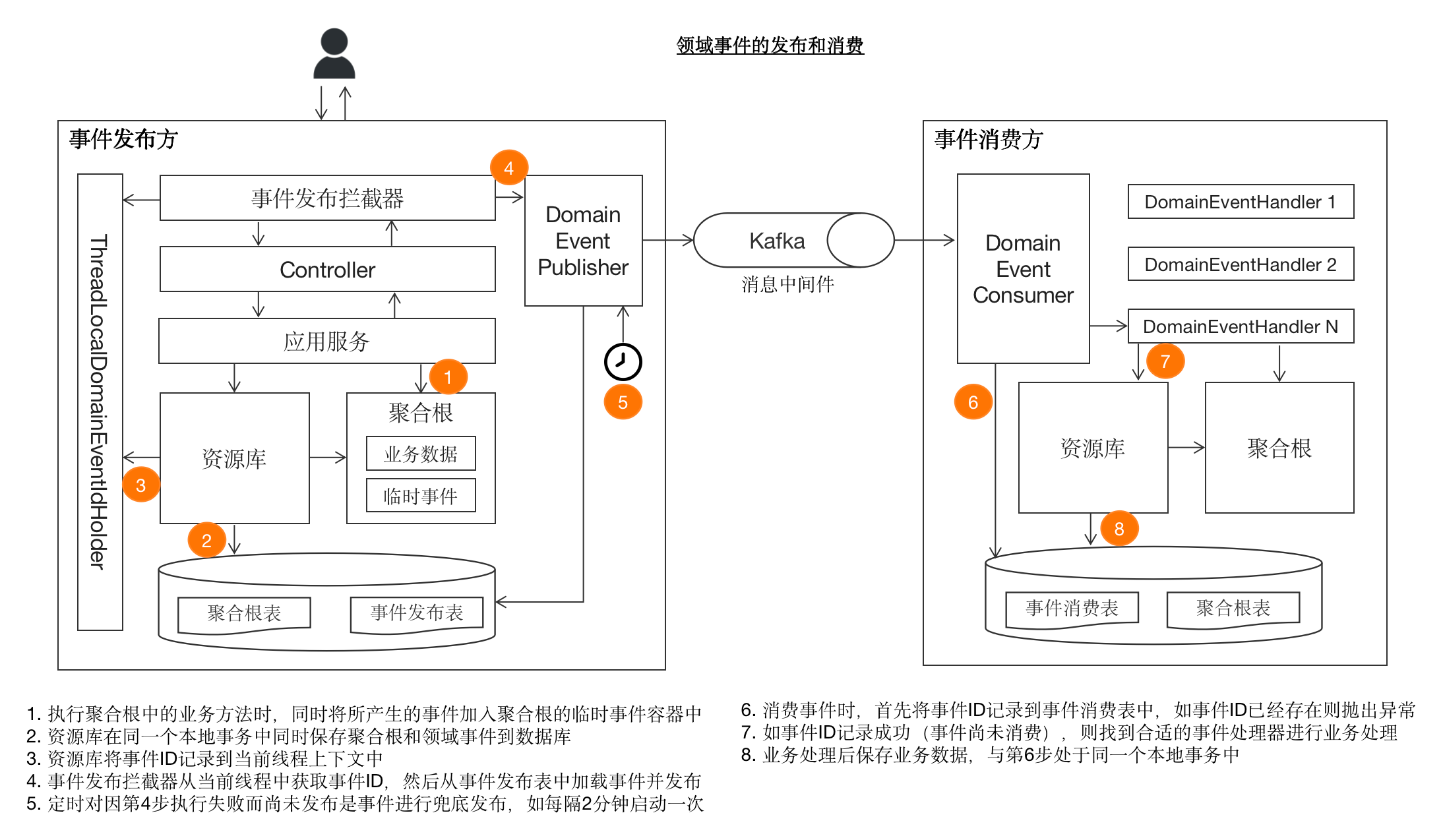

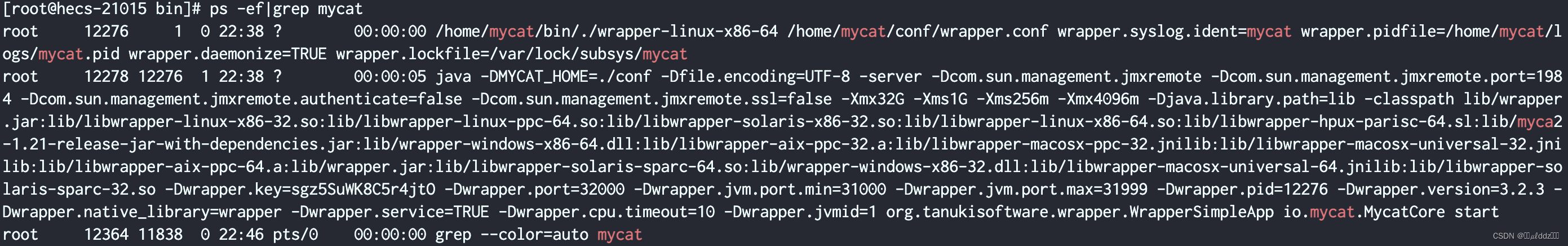

- 本文采用测量和 TCAD(技术计算机辅助设计)仿真相结合的方法来研究和分析短路应力后 1.2 kV SiC SWITCH-MOS 的残余损伤。

- 进行测量以检查短路应力前后 SWITCH-MOS 正向阻断状态下的漏电流和 ID-VGS 特性的变化。

- 进行 TCAD 仿真以研究短路应力期间漏极电流波形、总电流密度和晶格温度分布。

- 文章还比较了带有和不带有嵌入式沟槽 SBD(肖特基势垒二极管)的 SWITCH-MOS 的测量特性,以了解 SBD 区域在观察到的变化中的作用。

- 测量和仿真的结合可以对短路应力对 SWITCH-MOS 的影响进行全面分析,并提供对 SBD 区域物理变化和潜在损坏的见解。

文章的结论

- 文章的结论是,对 1.2 kV SiC SWITCH-MOS 施加短路应力会导致残余损伤和特性变化。

- 正向阻断状态下的漏电流和 SWITCH-MOS 的 ID-VGS 特性会受到短路应力的显着影响,尤其是在漏极电压低于 1200 V 的区域,漏电流会大幅增加。

- 由于高温晶格温度超过肖特基金属层的制造温度,SWITCH-MOS 中的 SBD 区域在短路应力期间容易受到物理损坏。

- 必须在几微秒内检测到短路状态并迅速关闭设备,以防止损坏。

- 文章还通过比较带有和不带有嵌入式沟槽 SBD 的 SWITCH-MOS 的特性,突出了 SBD 区域的作用。

- TCAD 仿真进一步支持了这一发现,表明在短路应力期间 SBD 区域的漏电流较大,晶格温度较高。