文章目录

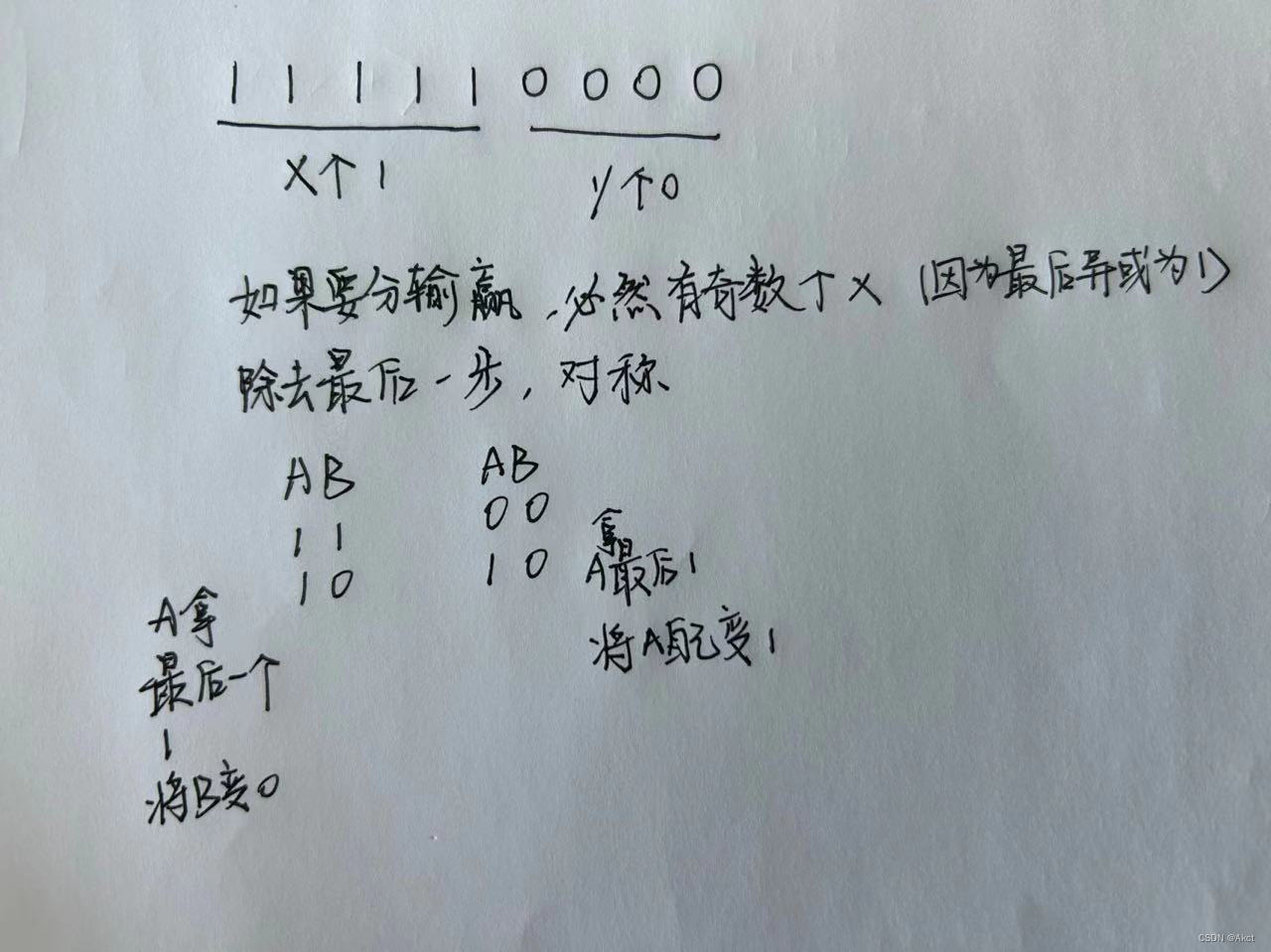

- SoC(System on Chip)片上系统

- SoC的概念

- SoC总线架构存在的问题

- 互联网络基础

- ①什么是互联网络?

- ②哪里有互联网络?

- ③互联网络的意义?

- ④互联网络的参数有哪些

- NoC(Network on Chip)片上互联网络

- 什么是NoC?

- NoC的引入

- NoC相比于总线架构的优势

- NoC常见的拓扑结构

- 2D Mesh

- 2D Torus

- 3D Mesh

- Octagon/Spidergon结构

- Cluster Mesh结构

- 树状结构

- 蝶状结构

- 各种结构之间的比较

SoC(System on Chip)片上系统

SoC的概念

SOC(System on Chip,片上系统)指在单一芯片上实现的数字计算机系统,总线架构是该系统的主要特征。

在 ASIC 设计的早期,由于制造工艺和性能等的约束,大部分芯片都单纯地实现某个特定功能,如处理器内核、总线、内存控制器、蓝牙等都由各自独立的芯片分别实现。

随着制造工艺的提升,以及设计能力的增强,单颗 ASIC 的功能越来越全面和强大,在一颗芯片内完全可以实现诸如处理器内核、总线、内存控制器、蓝牙等所有的功能。同时,ASIC 规模增大导致设计愈来愈复杂,因此,以 IP 核互连为核心的设计方法学应运而生。

这样,就出现了在一颗芯片里集成了大量的处理器内核、总线、控制器等 IP,而处理器内核数量也由曾经的单核增大到多核、众核。在这种情况下,设计方法学完全不同于以往 ASIC 的设计方法学。因此,诞生了 SoC 的概念,以和 ASIC 进行区别。不严格地说,一颗 SoC 可以实现以前多颗 ASIC 构成的系统。

SoC总线架构存在的问题

目前,SoC通讯架构的设计相对比较成熟。大部分芯片公司芯片制造都采用SoC架构。

然而,随着商业应用开始不断追求指令运行并存性和预测性,芯片中集成的核数目不断增多,基于总线架构的SoC将逐渐难以应对不断增长的计算需求。其主要表现为:

1.可扩展性差

基于总线架构的SoC,由于总线架构固有的仲裁通信机制,即同一时刻只能有一对处理器核心进行通信,限制了可以在其上扩展的处理器核心的数量。在众核体系结构下网络互联也就成为了重要的问题。

2.平均通信效率低

SoC中采用基于独占机制的总线架构,其各个功能模块只有在获得总线控制权后才能和系统中其他模块进行通信。从整体来看,一个模块取得总线仲裁权进行通信时,系统中的其他模块必须等待,直到总线空闲。

因此通信效率低。

3.单一时钟同步问题。

总线结构要求全局同步,然而随着工艺特征尺寸越来越小,工作频率迅速上升,达到10GHz以后,连线延时造成的影响将严重到无法设计全局时钟树的程度,而且由于时钟网络庞大,其功耗将占据芯片总功耗的大部分。

互联网络基础

①什么是互联网络?

互联网络是终端之间传输数据的可编程系统。

②哪里有互联网络?

从小尺度到大尺度,网络无处不在:

根据互联网络的定义,我们发现,它不仅仅出现在台式电脑/笔记本等终端之间的通信上,放在更小的尺度,在芯片上网络也遵循该定义。

- 在处理器内的存储器、寄存器、算术单元之间的通信;

- 处理器和内存等IP的通信;

- 局域网和广域网级别的系统级的通信;

③互联网络的意义?

情况①:

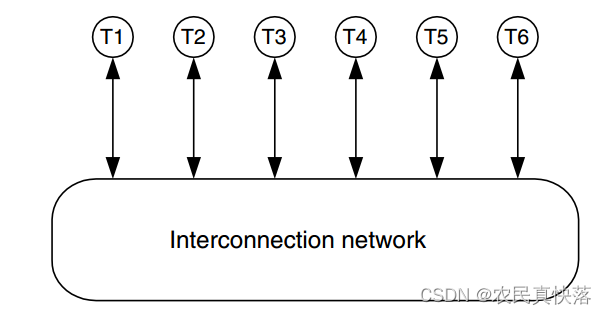

图中6个终端如果建立一对一独占信道,且信道是有方向的,那么需要多少条信道?

该问题等价于6个顶点的有向图最多有多少边,6*5=30条边。

然而,可能其中T1-T5的通信较为频繁,而T6几乎不与其他终端通信,因此为T6建立那么多独享信道是浪费的!

情况②:

如果我们将6个终端连成一个环,那么可能损失一点性能,但换来的是节省了大量资源。

从情况①和情况②的对比可以发现,互联网络的意义在于可以平衡建立信道的资源消耗和通信性能。

④互联网络的参数有哪些

- 终端数量

- 每个终端的峰值带宽

- 每个终端的平均带宽

- 所需的延时

- 消息大小或消息大小的分布

- 交互模式(traffic pattern)

- 所需的服务质量(Quality of Service)

- 所需的可靠性和可用性

解释:

在不特殊说明下,输入和输出带宽相等,单位是bits/秒。

传递单个消息所需的时间称为消息延时,消息延时和带宽是一对矛盾。

如果消息很小,网络所产生的开销就相对比较大。

每个终端以相同的概率向所有其他终端发送消息,这是random traffic pattern。

QoS和服务策略相关,

例如:

- 先来先服务(FCFS)

- 短作业优先(Shortest Job First,SJF)

- 最高响应比优先(Hight Response Ratio Next,HRRN)

可靠性指的是要无损传输,这涉及到检错纠错。

可用性指的是网络可用且正常运行的时间,该挑战在于快速检测故障,从故障中恢复。

NoC(Network on Chip)片上互联网络

什么是NoC?

在SoC上的互联网络我们称NoC(Networks on Chip)。

NoC的引入

随着 SoC 技术的发展,芯片内部的 IP 核越来越多,有可能在一颗芯片中集成了数以百记的处理器内核(包括同构处理器内核和异构处理器内核)、数以千计控制器 IP 核等等,那么这种情况下,为了实现IP核间的通信能够高效、高吞吐量、低功耗, IP 核之间的互联就成为 需要考虑的重要问题。

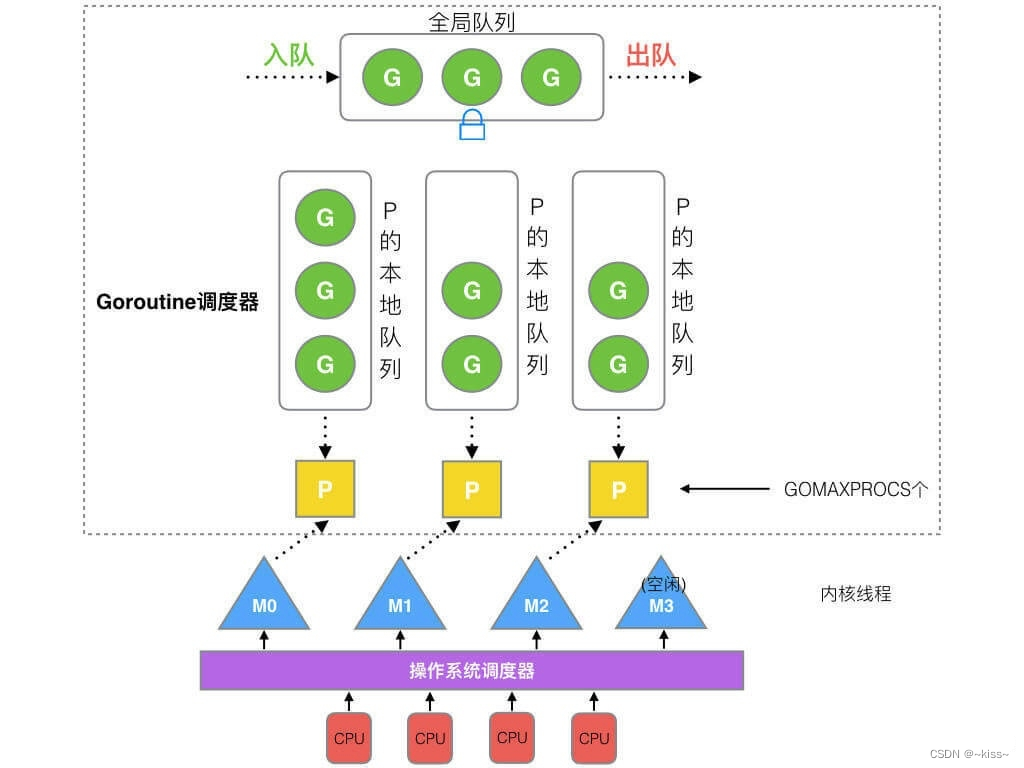

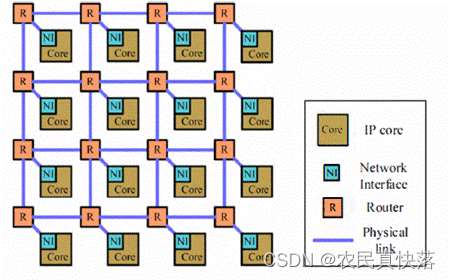

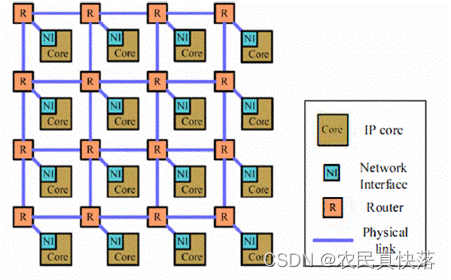

借鉴于计算机网络中的OSI(Open System Interconnection)分层模型和并行计算机的互联网络,NoC将宏观网络的通讯理念应用于芯片上,将每个核当做一个独立的单元,IP核经过网络接口与特定的路由器相连。将IP核之间的通信转换为路由器与路由器的通信。

举例:

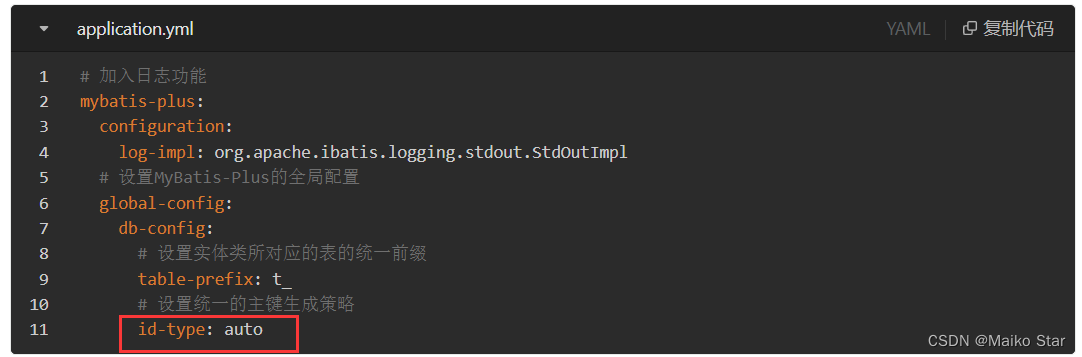

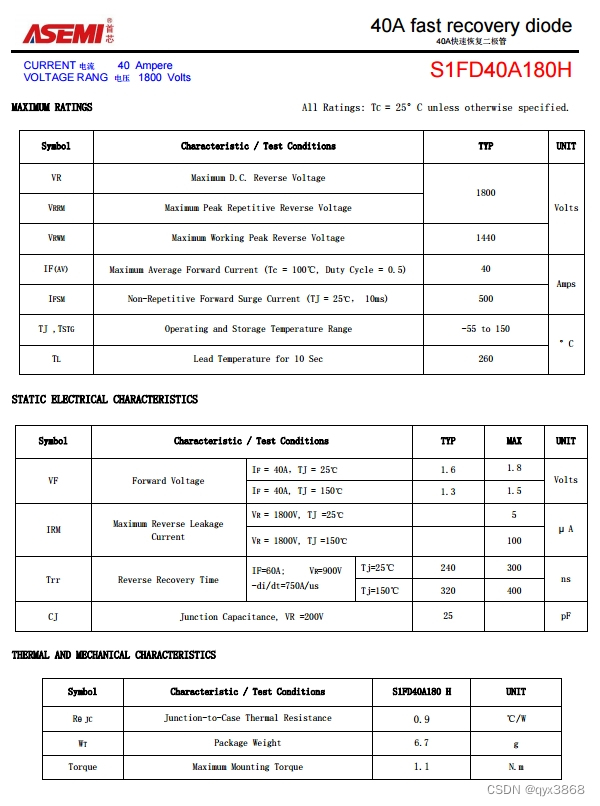

一个典型的NoC拓扑结构(2D-Mesh)如图所示,图中R是路由器,NI是网络接口,NoC拓扑将IP核之间的通信转换为路由器之间的通信。

NoC相比于总线架构的优势

NoC(Network on Chip,片上网络)网络的出现,相比于总线架构优势如下:

- 采用异步时钟,多个IP之间的时钟网络解耦,布局布线容易;

- 可扩展性好,增加互联IP数量时,代码改动工作量小;

- 支持多个IP并行交互,通信效率高;

NoC常见的拓扑结构

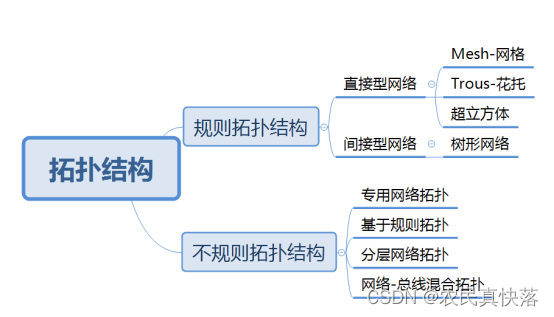

NoC常见的拓扑结构可以分为规则拓扑和不规则拓扑两种。

规则拓扑主要包括:

- 2D Mesh

- 2D Torus

- 3D Mesh

- Octagon

- Cluster Mesh

- Spidergon

- 超立方

- 蜂窝式

- 树形

- 蝶形

不规则拓扑包括:专用网络、分层网络、网络-总线混合拓扑、基于规则拓扑组合而成的拓扑结构。

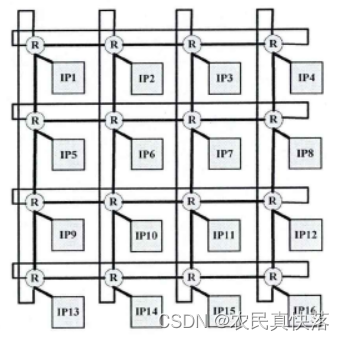

2D Mesh

2D Mesh结构为二维网格架构,路由器节点按二维网格的方式排列,每个节点上再连接网络适配器和IP核。下图所示为一个4×4的2D Mesh结构。

在 N×N 的2D Mesh中,每个节点与相邻的节点连接(边界节点除外)。该结构具有结构简单,易于实现,可扩展性好等优点,较为广泛使用。

2D Torus

将2D Mesh结构的每行首尾节点连接起来,每列的首位节点也连接起来,便是2D Torus结构,该结构每个节点在几何上都是等价的,缩短了节点间的平均距离,减小了网络直径,同时该结构可能因为过长的环形链路而产生额外的延迟。

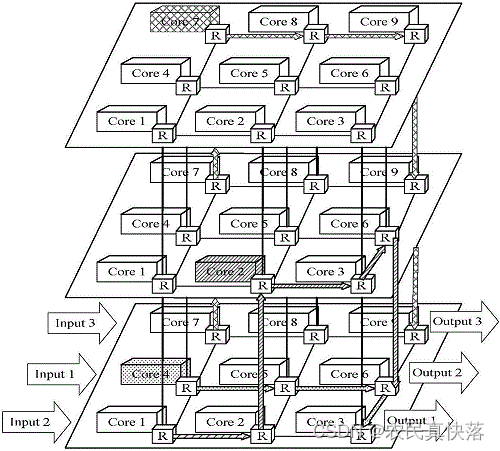

3D Mesh

3D Mesh为三维的网格结构,将多个2D Mesh叠加并对应节点连接起来,这样做进一步降低了网络直径和平均距离,但物理实现难度比较大。

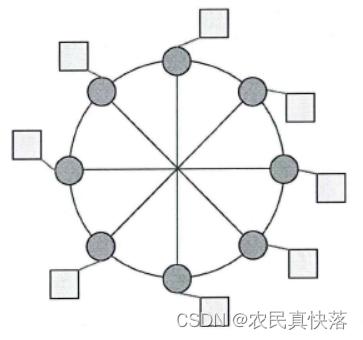

Octagon/Spidergon结构

Octagon为八边形结构,共包含8个IP核,每个节点与三个节点相连,分别是序号相邻的节点和最远的节点。该结构也可以扩展为8个以上节点,变为Spidergon结构。

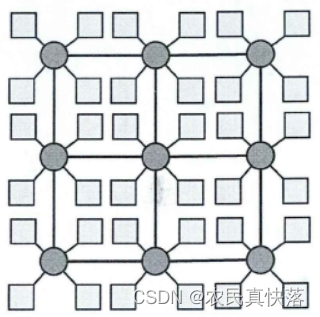

Cluster Mesh结构

Cluster Mesh 结构改变了传统的一个IP核连接一个路由器,将4个IP核连接1个路由器。这样做减少了路由器数量,简化了拓扑结构,但更容易造成数据拥塞。

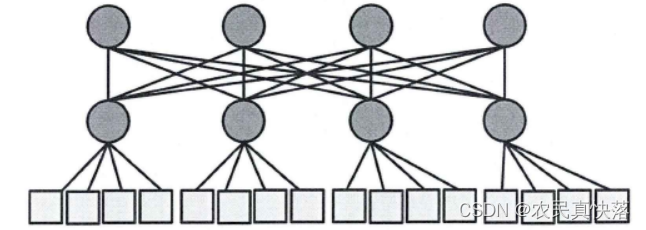

树状结构

该结构类似于数据结构中的树结构,IP为叶子节点,路由器节点作为父节点,在父节点之上可以在增加父节点,层层相扣。降低了设计难度,也降低了物理设计的复杂度。

SPIN结构是一种树状结构,具有16个叶子节点以及8个路由器节点。每个节点拥有4个父节点,通过增加路由节点冗余度的方式,增加多路径选择性,提高系统性能。但是该结构的路由节点复杂,芯片实现难度大。

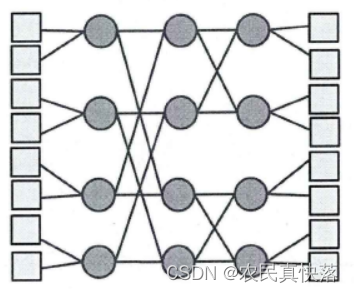

蝶状结构

该结构有些类似于FFT中的结构,是一种对数结构。一个n维的蝶形拓扑结构由2n个IP核和n×(2n-1)个路由器的节点组成,路由器分为n层,每层有N/2个路由器。

各种结构之间的比较

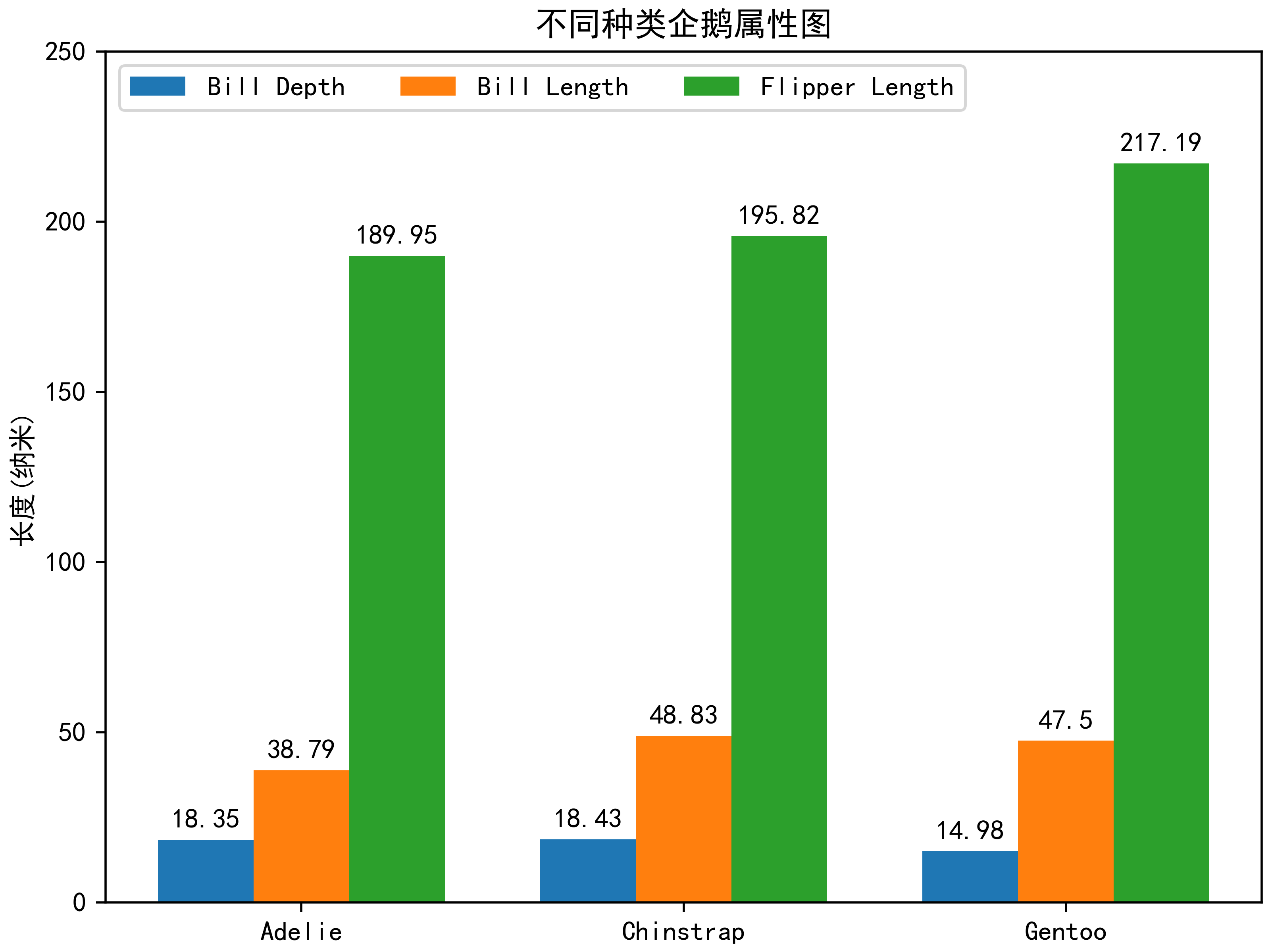

| 拓扑结构 | 节点数 | 节点度 | 网络直径 | 链路数 |

|---|---|---|---|---|

| 2D Mesh | N=n^2 | 4 | 2n-2 | 2(N-n) |

| 2D Torus | N=n^2 | 4 | n | 2N |

| 3D Mesh | N=3n | 4 | n | 2(N-n) |

| Octagon | N=n^2 | 3 | [N/4] | [(N mod 8) +1]×12 |

| Spidergon | N=n^2 | 3 | [N/4] | 3N/2 |

| Cluster Mesh | N=n^2 | 4 | 2n-2 | 5N-2n |

| Spin | N=2n | 4 | N/8 | 5N/2 |

| 蝶形结构 | N=2n | 2 | n+1 | (n-1)×N |