文章目录

- 1.Verilog语言的设计思想和可综合特性

- 2. 组合电路的设计

- 2.1 数字加法器

- 2.2 数据比较器

- 2.3 数据选择器

- 2.4 数字编码器

- 2.4.1 3位二进制8线-3线编码器

- 2.4.2 8线-3线优先编码器

- 2.4.3 二进制转化十进制8421BCD编码器(重要)

- 2.4.4 8421BCD十进制余3编码器

- 2.5 数字译码器

- 2.6 奇偶校验器

- 非常重要

1.Verilog语言的设计思想和可综合特性

-

HDL是对硬件电路的一种描述性设计语言,它的过程和传统C语言不一样

-

C语言是一种高级程序语言,然后把它编译成机器代码,然后对cpu,dsp,mcu这些处理器操作的过程,所以它只有代码到编译这个过程生成机器执行代码

-

而电路描述语言是在计算机上对硬件进行设计,目标是一个电路,最后是通过综合工具生成一个简单的元器件的生成关系,我们称之为网表

-

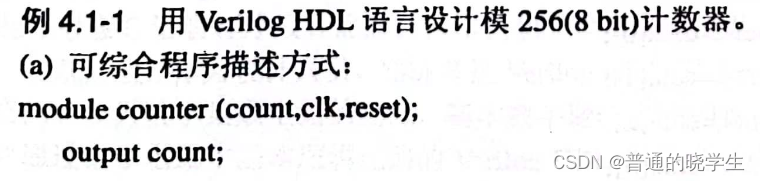

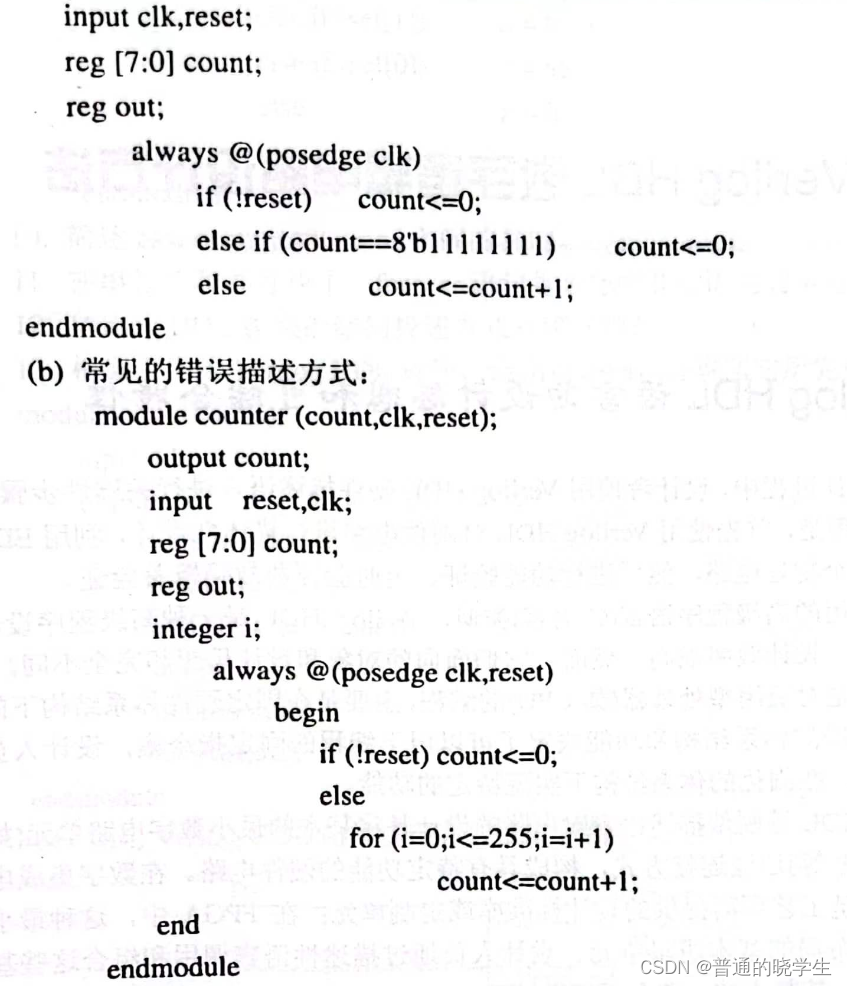

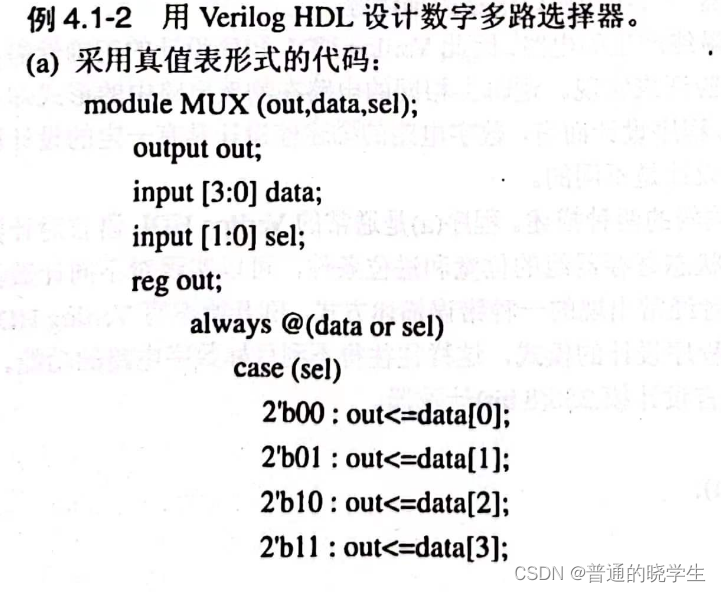

可能产生的错误设计:

-

Verilog HDL的电路描述方式具有多样性,这也决定了电路设计的多样性。例4.1-2是对一个多路选择器的设计,程序(a)采用的是真值表的形式,程序(b)采用的是逻辑表达式的形式,程序©采用的是基本逻辑单元的结构性描述形式。

2. 组合电路的设计

-

组合电路的特点是,电路中任意时刻的稳态输出仅仅取决于该时刻的输入,而与电路原来的状态无关

-

需要考虑以下方面:

(1)所用的逻辑器件数目最少,器件的种类最少,且器件之间的连线最简单,这样的电路称为“最小化”电路

(2)为了满足速度要求,应使级数尽量少,以减少门电路的延迟

(3)电路的功耗应尽可能地小,工作时稳定可靠

(4)1是功能要求,2和3是性能要求 -

讲组合电路的时候:用真值表描述,用卡诺图化简得到最简代数表达式,再写出结构体描述。

-

!!!!但是我们发现卡诺图在HDL好像没有生存的余地,包括后面的有限状态机。这是因为它们这种优化的方法已经被数学完全的取代了,都交给综合工具去做了,和硬件描述语言的设计已经没有太大关系了

-

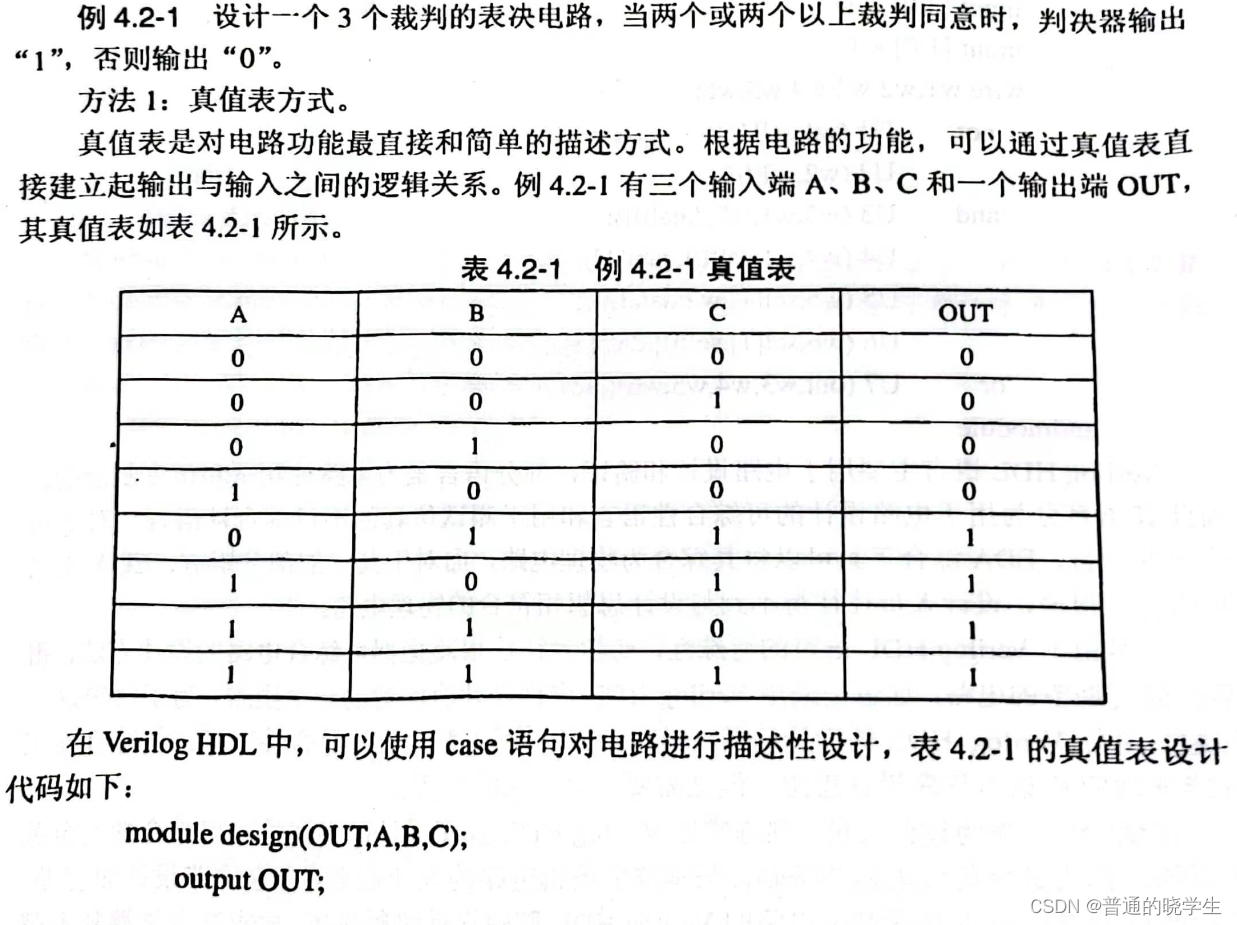

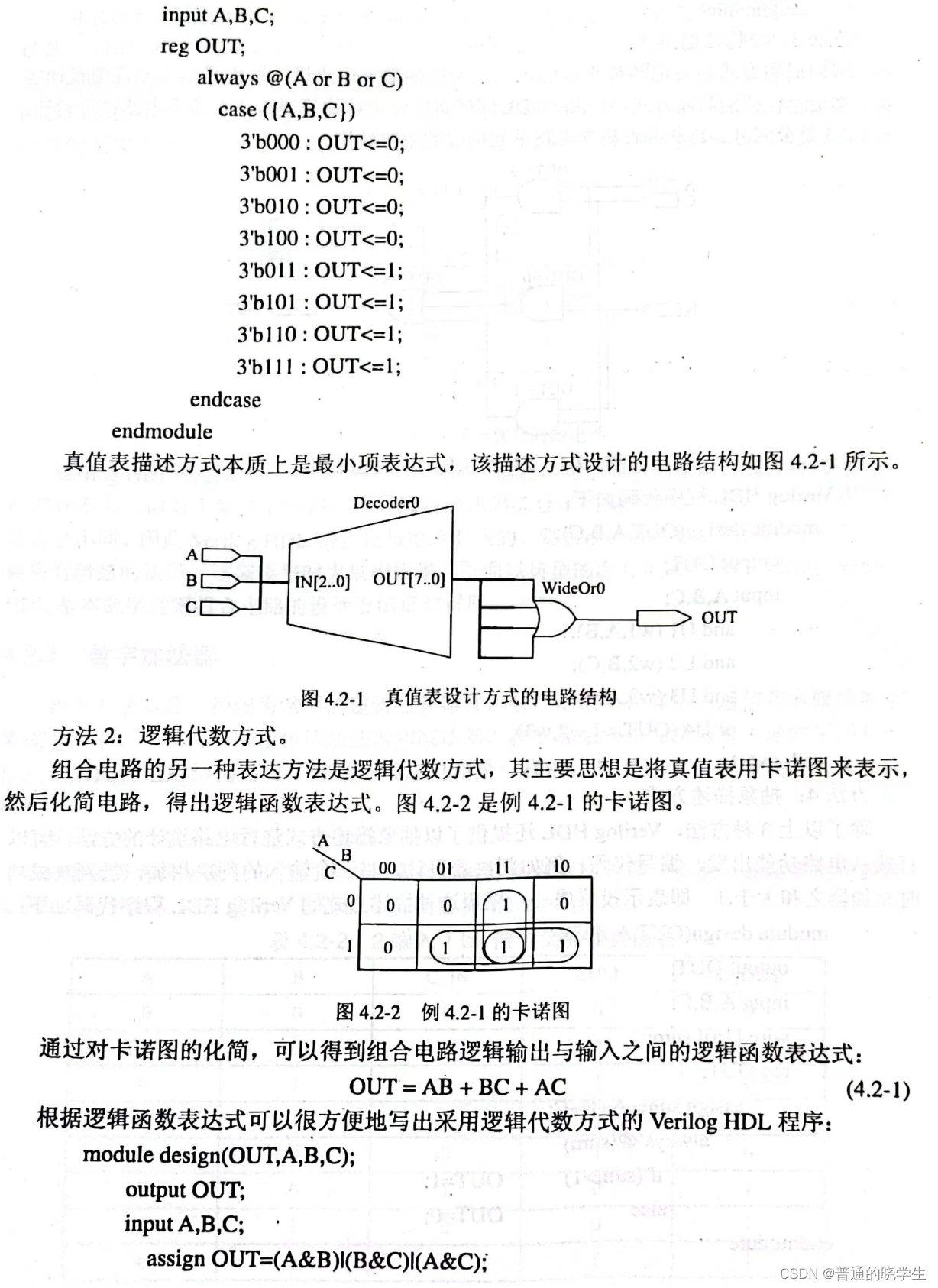

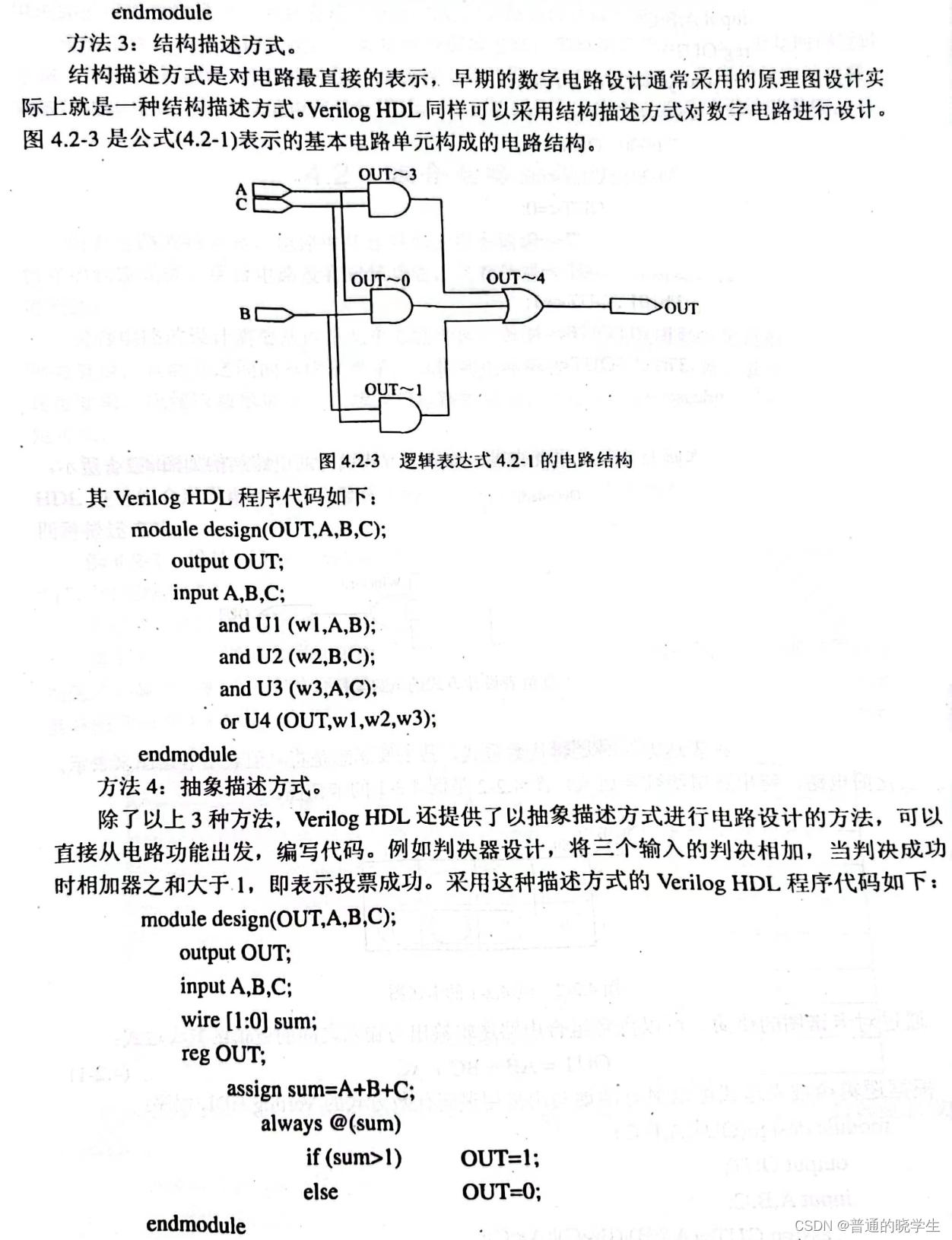

组合逻辑电路的描述方式有四种: 真值表、逻辑代数、结构描述、抽象描述。采用 VerilogHDL 进行组合逻辑电路设计主要采用的就是这几种方式

-

对于前三种设计方式,结构体描述读起来是最困难的,case语句加真值表是最直接的一种方式,数据流描述是一种最简化的描述

-

!!当你对数字电路的认知程度不同的时候选择的电路是不一样的,很多初学者都会选择真值表,然后发现有问题解决不了了,就会改成结构型描述。当水平达到一定程度时,直接数据流描述

-

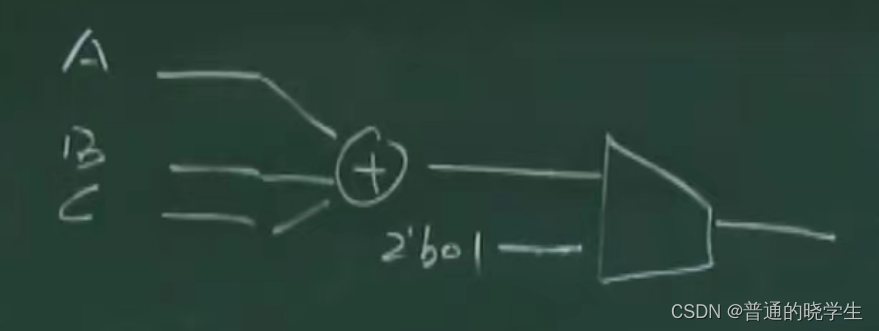

第四个抽象描述方式

-

抽象描述方式的优点是当裁判数量特别多的时候用这种方式很快,这种方式实际上就是硬件描述语言的RTL的抽象描述方式

-

!!不能随便写,在这个例子中,我们要脑子里有一个加法器,一个数据比较器,然后去写这个加法器和数据比较器,而不是写完了让综合工具去解决

-

最后一步是综合,EDA 综合工具可以将 Verilog HDL程序综合成物理电路形式,通过电路优化,从而得到符合设计要求的最简化电路

-

!!综合工具一方面把电路从代码的方式变成简单元器件的连接关系,同时进行了优化,把它变成了一个最简单的元器件的连接关系

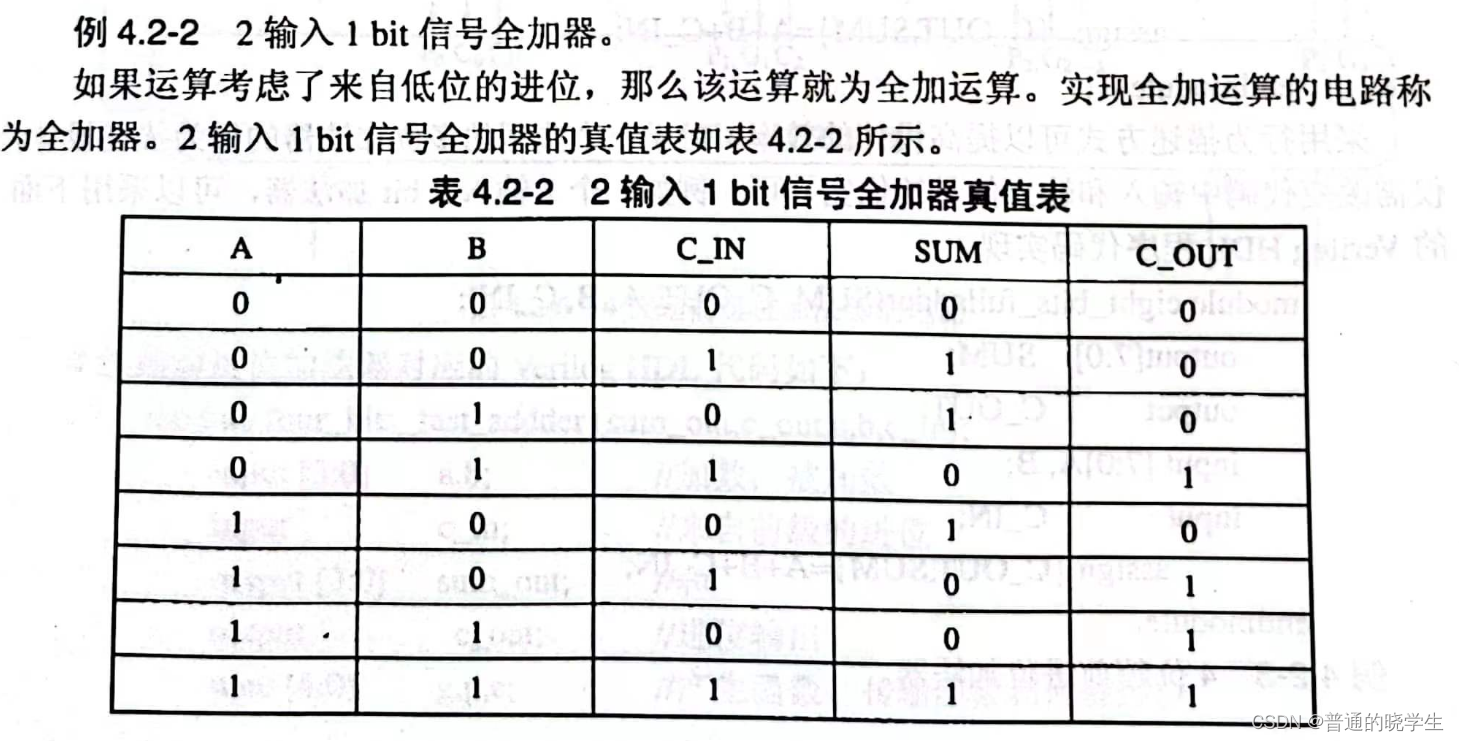

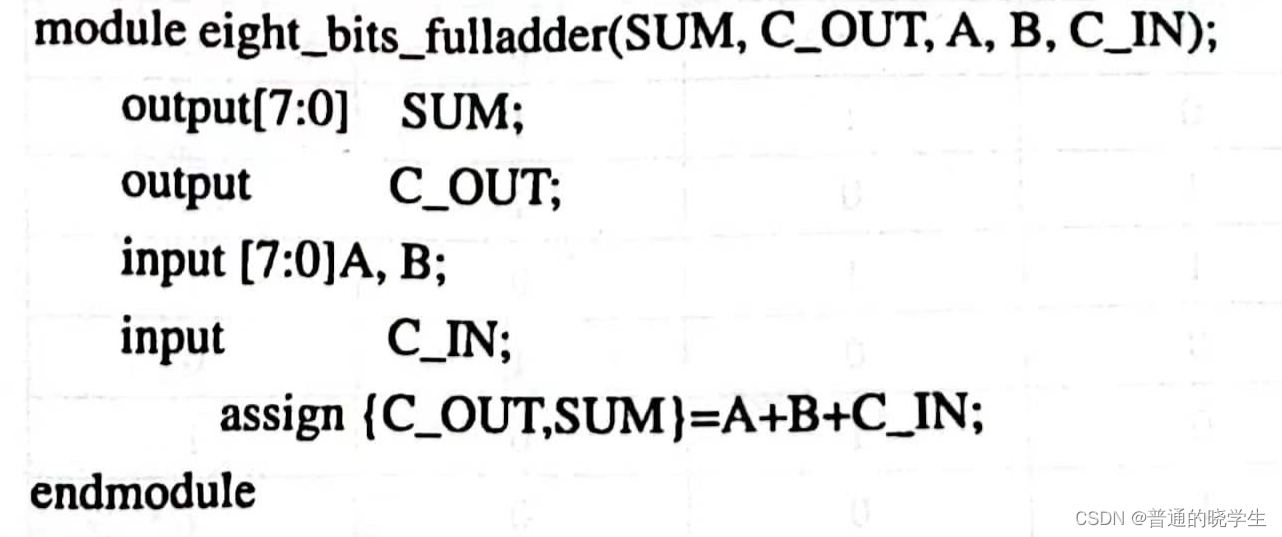

2.1 数字加法器

-

数字加法器是一种较为常用的逻辑运算器件,被广泛用于计算机、通信和多媒体数字集成电路中

-

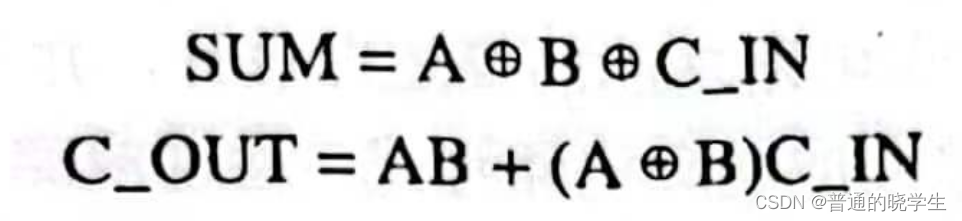

代数逻辑表示为

-

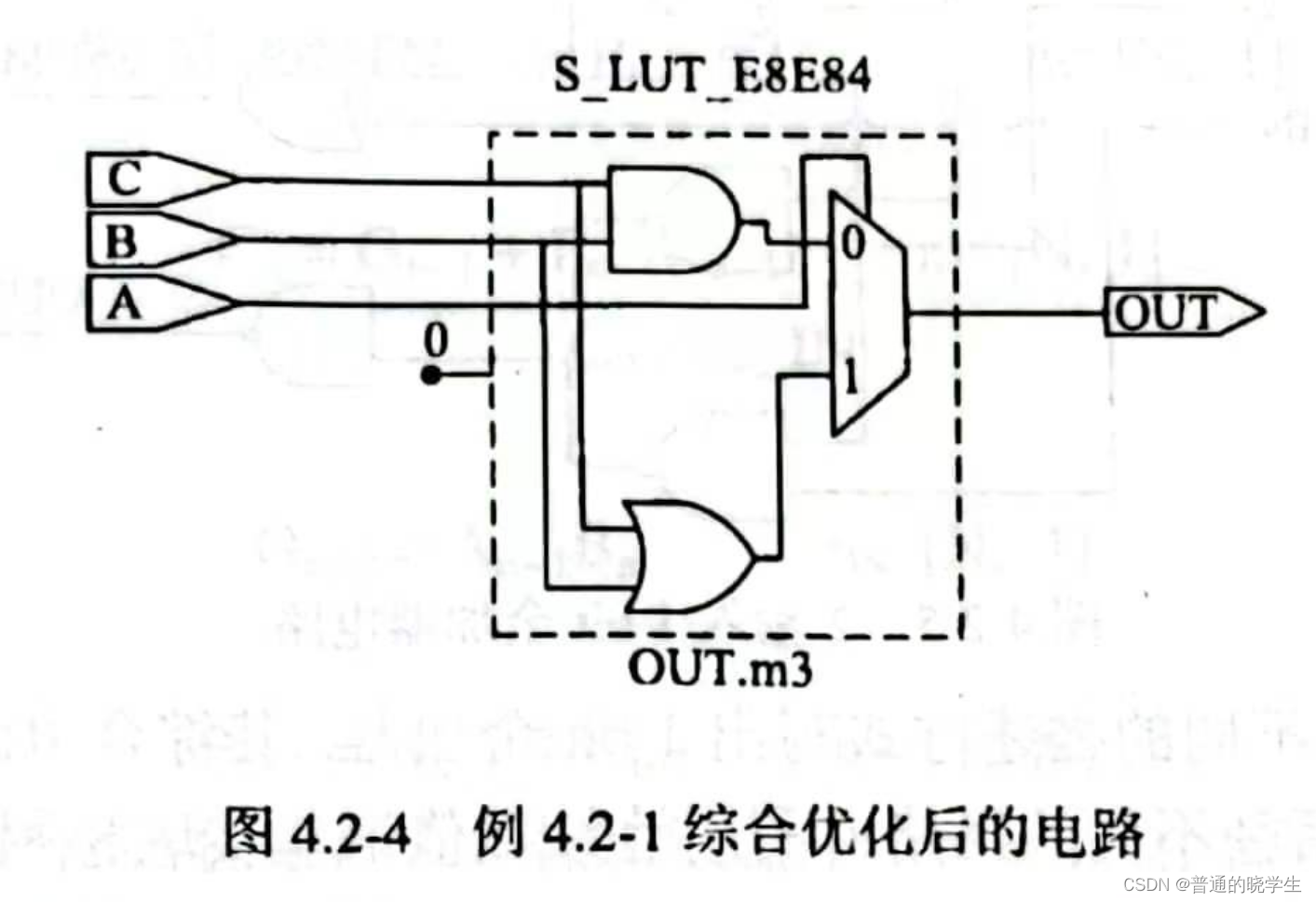

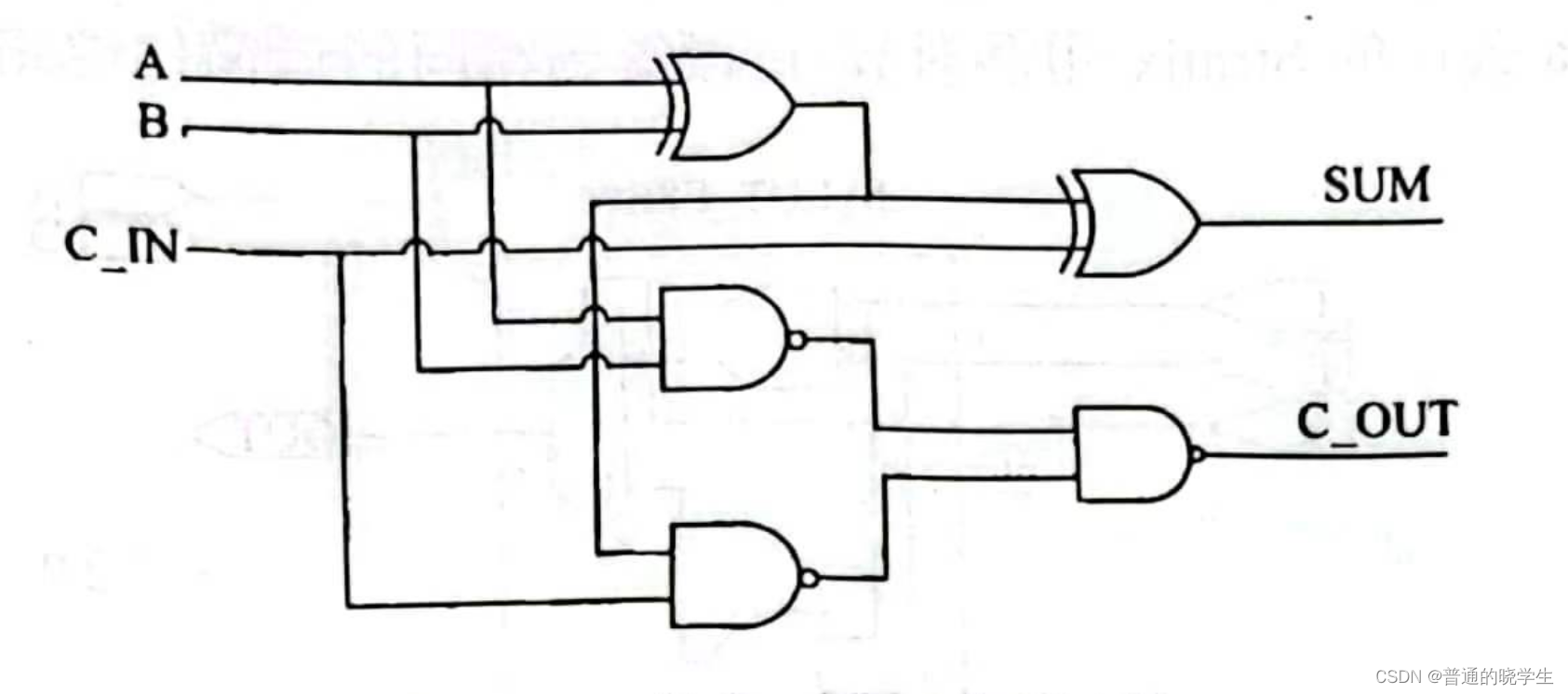

对应的电路如图

-

利用连续赋值语句实现和利用行为描述方式实现

-

采用行为描述方式可以提高设计的效率,对于一个典型的多位加法器的行为描述设计仅需改变代码中输入和输出信号的位宽即可。例如一个 2输入8 bit 加法器,可以采用下面的 VerilogHDL程序代码实现。

-

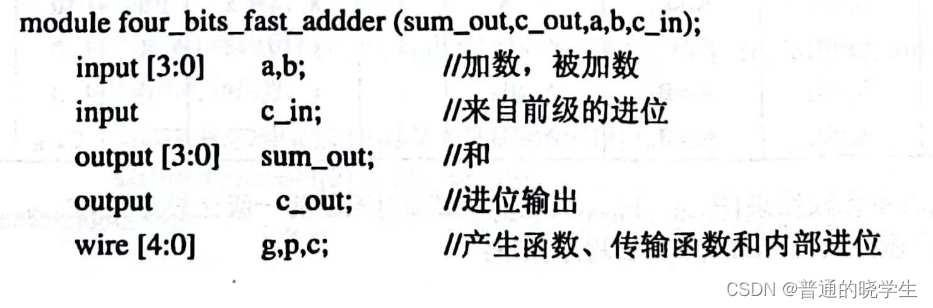

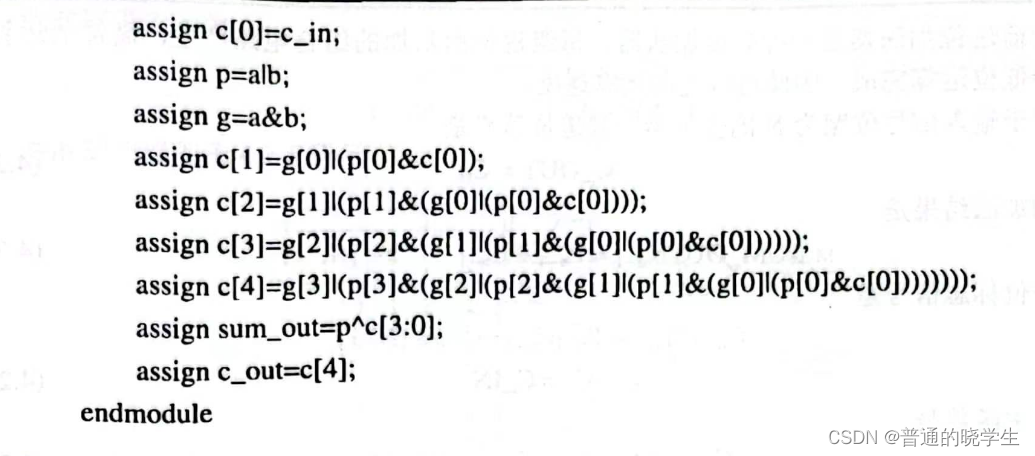

!!要注意加法器串联多了会导致电路延迟增大,影响性能(具体见我数电的博客 https://blog.csdn.net/y_u_yu_yu_/article/details/127435416)

-

可以用四位超前进位加法器来提高性能(数学分析省略,原理可以去看上面的博客)

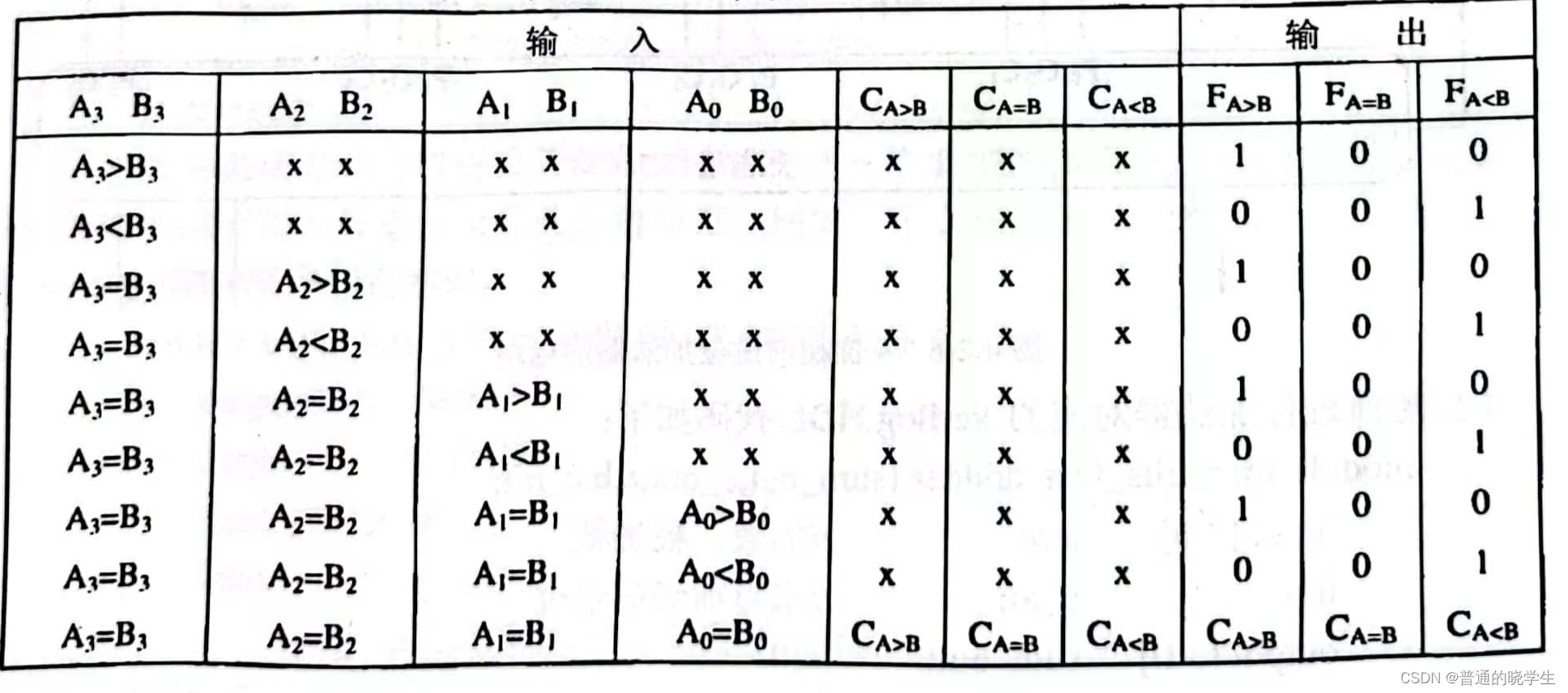

2.2 数据比较器

- 数据比较器用来对两个二进制数的大小进行比较,或检测逻辑电路是否相等。数据比较器包含两部分功能:一是比较两个数的大小;二是检测两个数是否一致。

- 4位数据比较器的真值表:

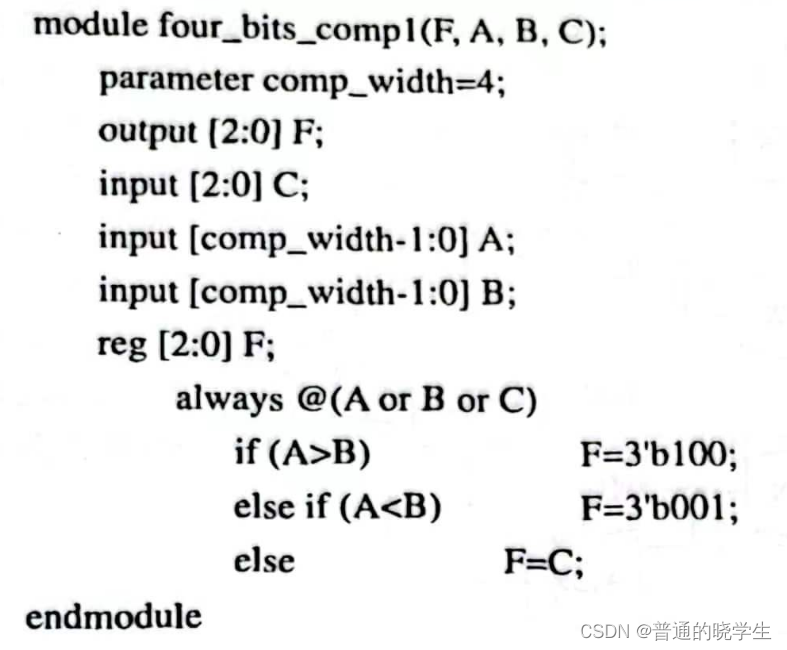

- 代码如下:

- 数据比较器在Verilog就是通过关系运算符来得到

2.3 数据选择器

-

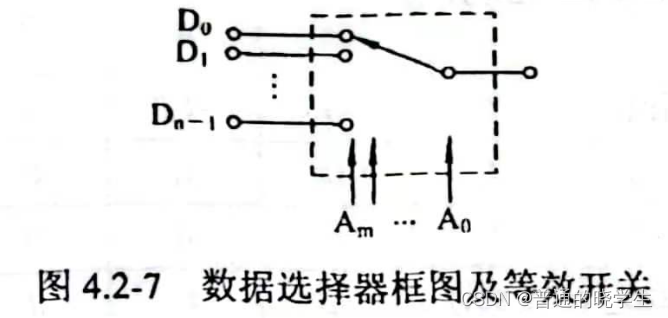

每次在输入地址的控制下,从多路输入数据中选择一路输出,其功能类似于一个单刀多掷开关

-

数字比较器,数字选择器,数字编译器等在电路中都有规定的对应的电路

-

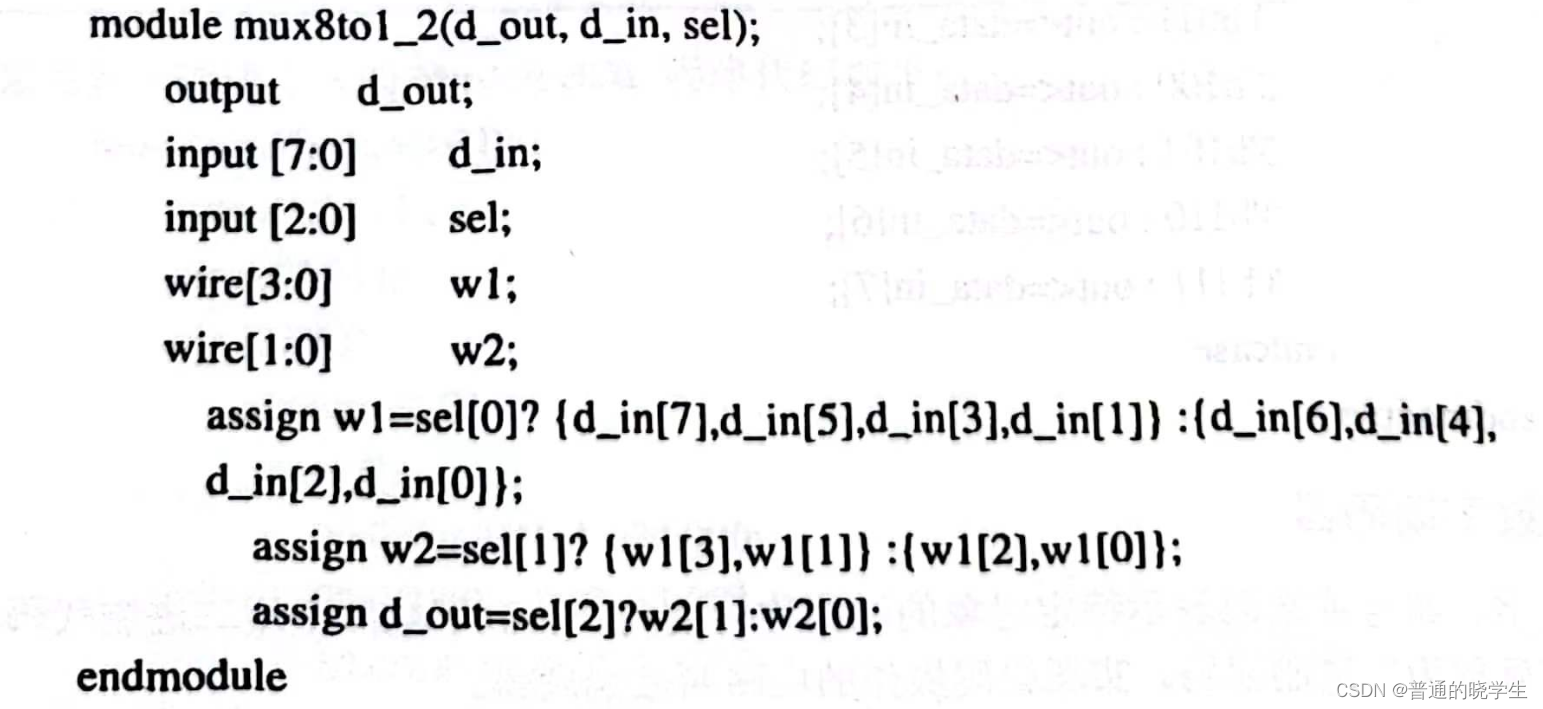

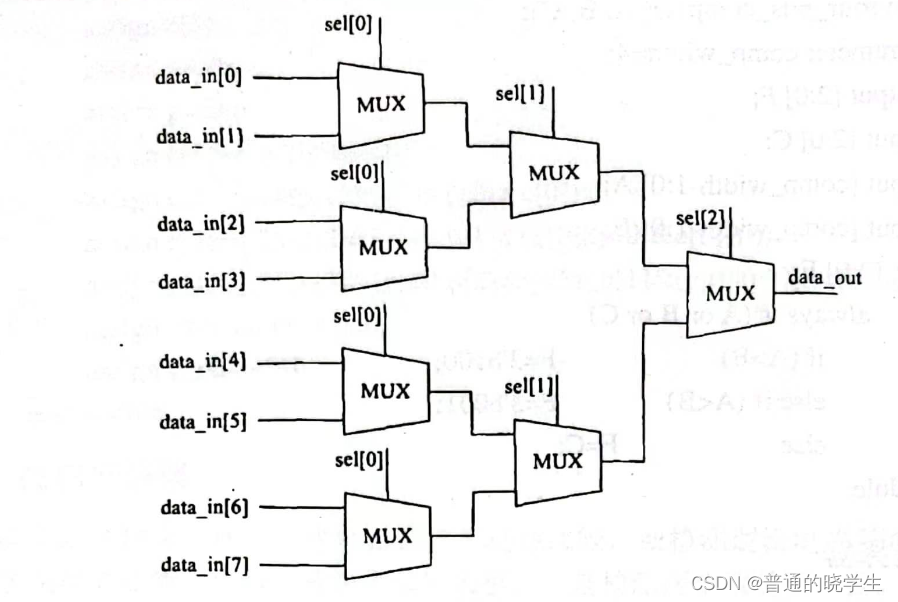

构成8选1数据选择器

(1)多个2选1数据选择器的结构级描述

结构如下

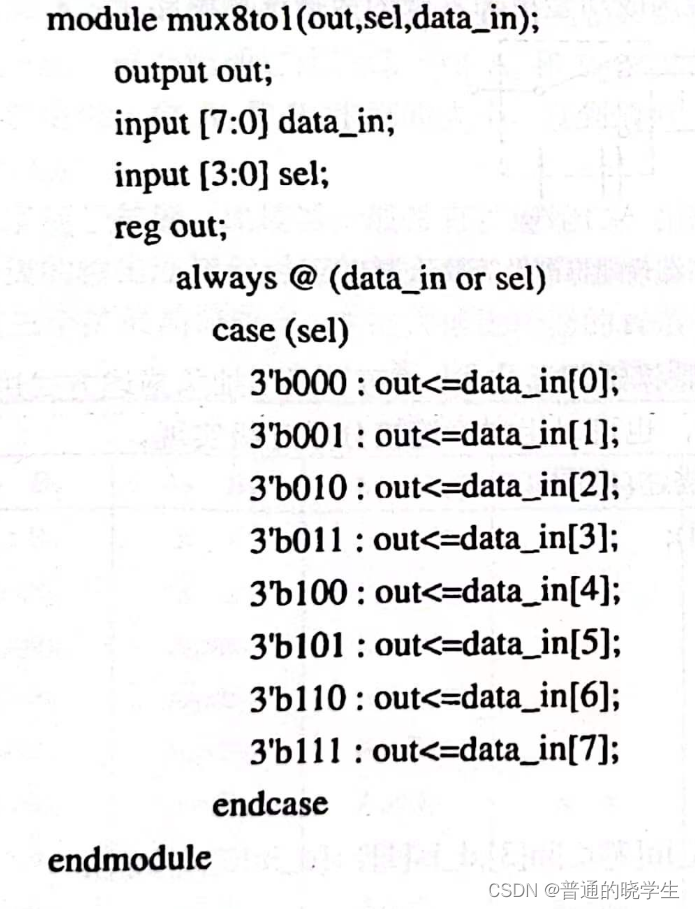

(2)抽象描述方式。多路选择器的设计可以采用 case 语句直接进行设计。在这种设计方式中,只需考虑选择信号列表就可以实现功能更为复杂的数据选择器

2.4 数字编码器

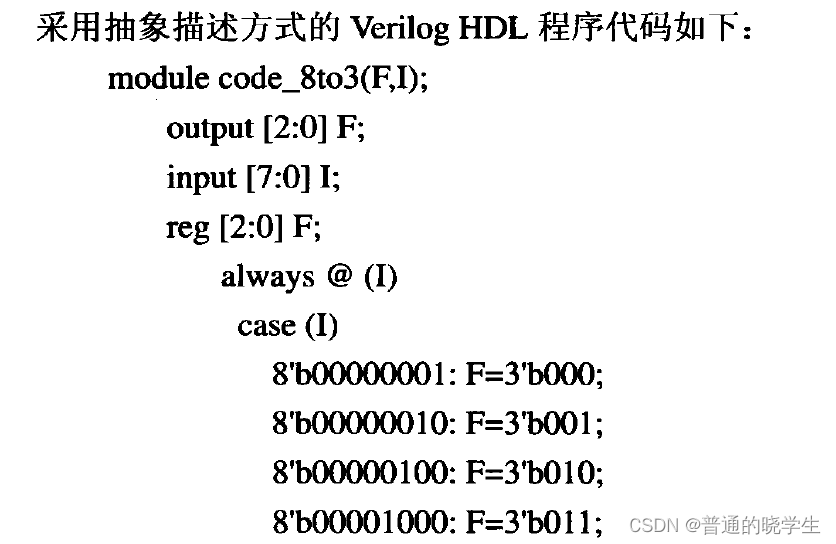

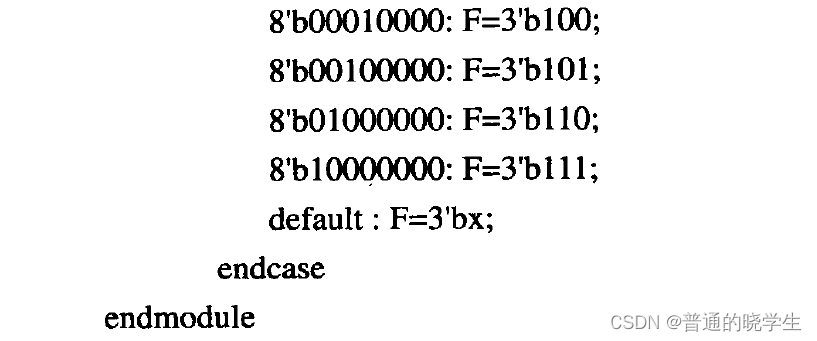

2.4.1 3位二进制8线-3线编码器

- 输入电平发生变化的时候,输出结果会标定它的位置

- 数字电路有很多的编码过程,为什么要用编码器:来自于不同位置的信号会非常多,如果每根信号都会产生一个有效位的话,对处理器压力很大。一方面来讲,它要相应这么多信号的位置;另一方面,它的管脚数量会增加

- 真值表:

- HDL代码实现:

(1)case语句的输入信号要作为敏感事件表放在always@里面

(2)虽然描述的组合电路,但是左边表达式的量要重新定义为reg类型

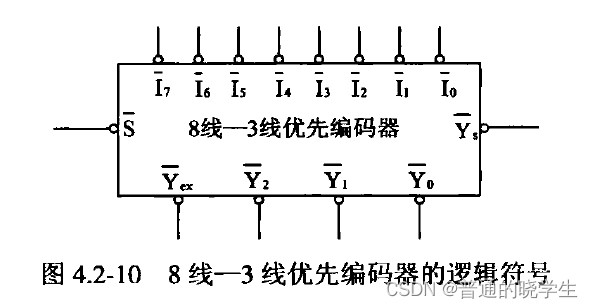

2.4.2 8线-3线优先编码器

- 二进制编码器电路要求任何时刻只有一个输入有效,若同时有两个或更多个输入信号有效,将造成输出混乱,因此在使用过程中有一定局限性。克服这种局限性的一种方法是采用优先编码器。

- 优先编码器允许多个输入信号同时有效,但它只对其中优先级别最高的有效输入信号编码,对级别低的输入信号不予理睬。优先编码器常用于优先中断系统和键盘编码

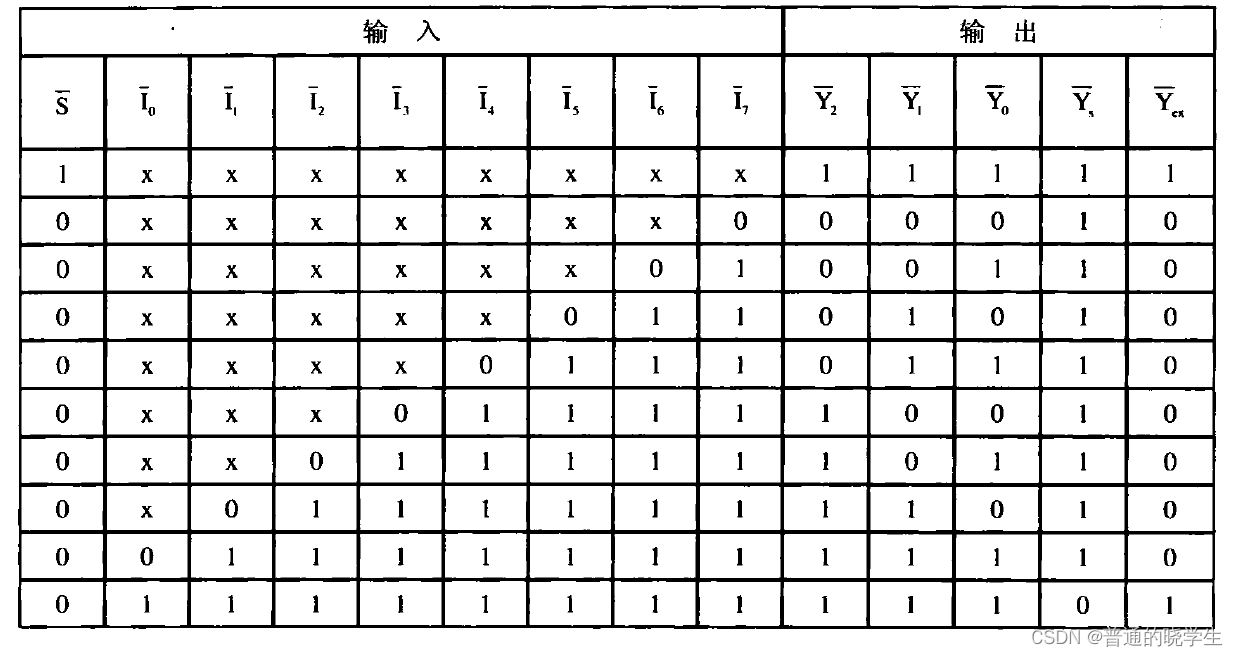

- 真值表:

(1)增加了一个选通信号,为0才工作

(2)在 8个输入端中,i的优先权最高,的优先权最低。当I7反=0 时,无论其它输入端有否有效输入信号(功能表中以x表示),输出端只输出的编码,即YY=000;

(3)

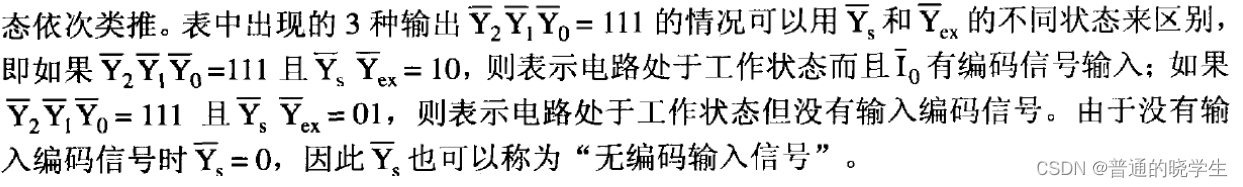

- 由于可以得到真值表,所以依然可以采用case语句:

- 采用了问号操作符,所以这八句是完整表述,不需要加default

- 需要对三个信号进行赋值,可以用begin-end,也可以用连接操作符,直接一条语句赋值

- !!要充分利用语法给我们的宽度

2.4.3 二进制转化十进制8421BCD编码器(重要)

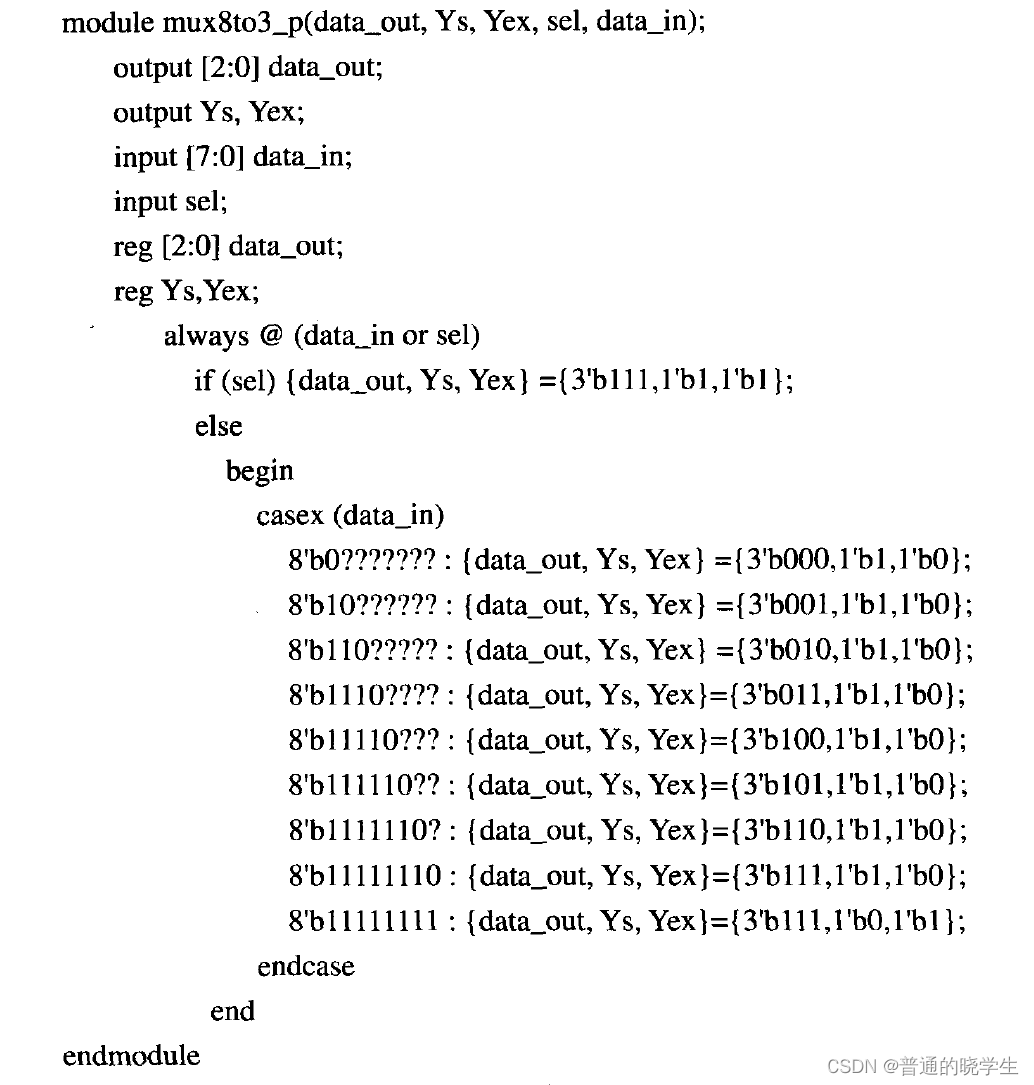

- 将十进制数 0、1、2、3、4、5、6、7、8、9这10个信号编成二进制代码的电路叫做制转化十进制编码器

- 0-9是是个数,4位二进制能表示16个数,所以在数字电路中,如果想描述一个十进制数的时候一般用4bit的数

- 编码表

- 用HDL进行表述

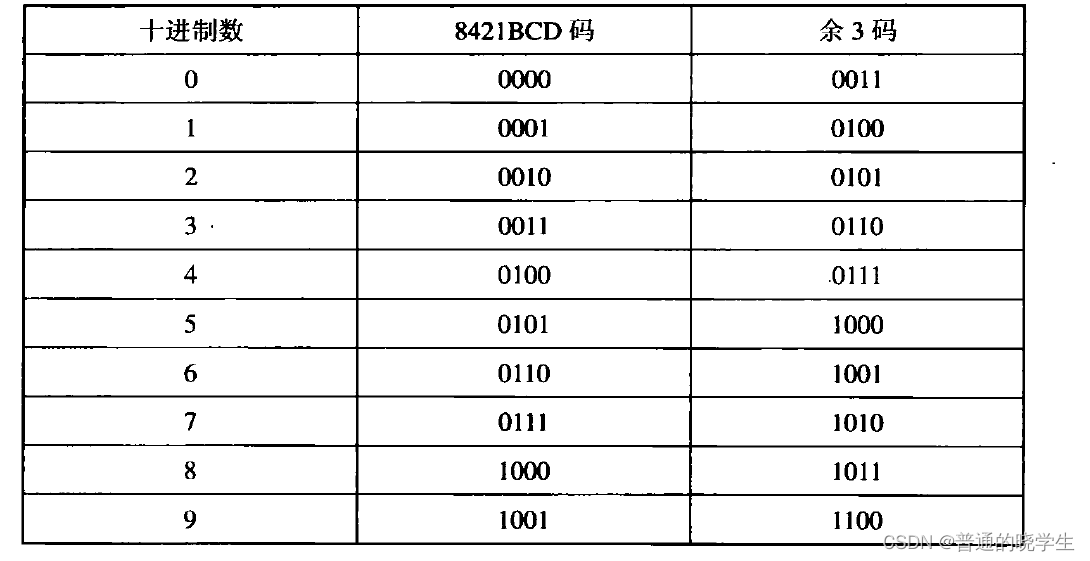

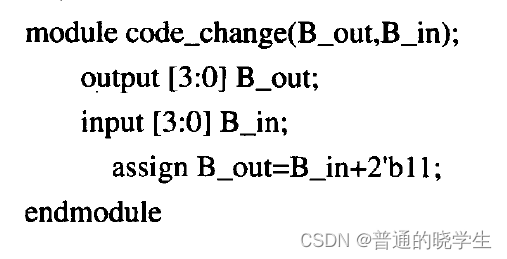

2.4.4 8421BCD十进制余3编码器

- 余3码也是一种 BCD编码,这种编码的特点是:用余3码作十进制加法运算时,若两数之和是 10,正好等于二进制数的 16,则从高位自动产生进位信号。

- 因此可以使用余3码简化计算。在 8421BCD 码上加3就得到了余3码

- 真值表

- 功能图

- 输入就是8421BCD编码器,直接加三就可以了

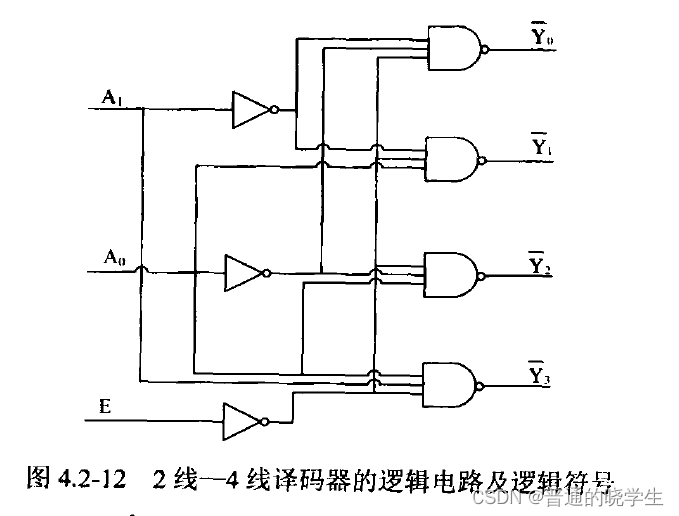

2.5 数字译码器

- 3-8译码器被广泛使用原因:3-8译码器最早是配和单片机系统出现的,而单片机的引脚最初非常少,为了对外面的电路进行控制,通常会在外面接一个3-8译码器

- !!随着电路规模增大,译码电路就会变得复杂得多,包括有时序的概念在上面

- 逻辑电路:

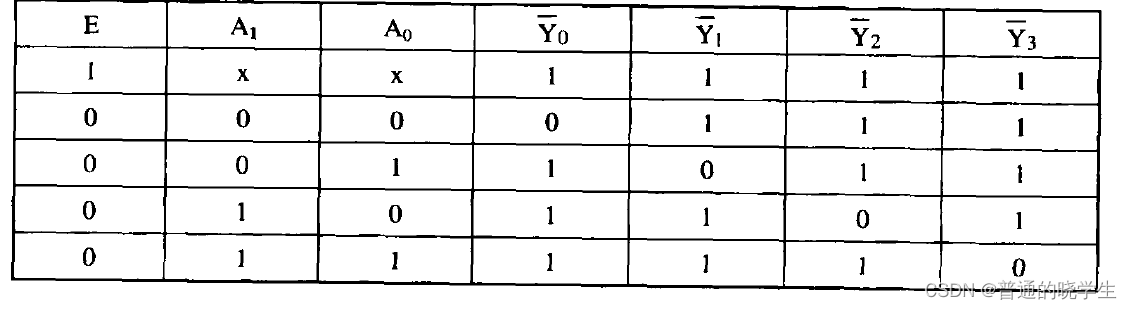

- 真值表:

- !!问题:数字电路为什么有的时候有效信号是高电平有的时候有效信号是低电平?

- 在数字电路里面,我们认为高电平是不稳定的,因为处在高电平的时候,电源会产生一些波动,所以很少在电路中采用高电平有效。因此,大多数电路都是低电平有效,直接拉到地

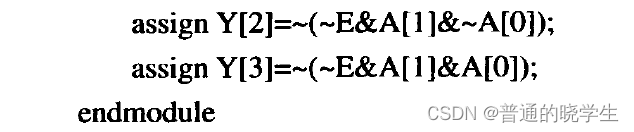

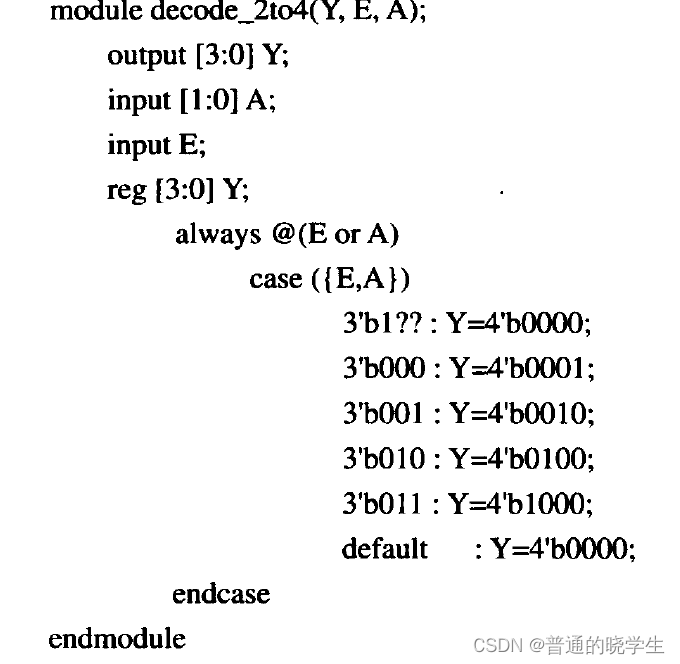

- 译码器的实现有很多种方法,下面举两种方法

- 方法1:

- 方法2(抽象):

- 采用抽象描述方式的优势是不需要对电路化简,根据相对固定的设计模式,可以直接得到所需要的电路

2.6 奇偶校验器

- 判断输入信号和发出来的数是否可能会有差距

- !!在芯片设计过程中,信号是在硅的介质上进行设计的,由于电源和外界扰动可能会对信号造成影响,所以现在对高速信号集成电路,一般不会按照8位,16位这种去排总线,一般是9位,18位,也就是每8个信号增加1bit的校验位,这样就能确保信号有更大的可能是正确的

- 在可编程逻辑器件中,所有的乘法器。RAM等全部都是奇偶校验的

- 奇偶校验一般用在能够重新操作的计算机硬件中,例如:SCSI 总线和微处理器中的高速缓存,在发生错误时,这些部件可以丢掉数据,获取重发数据。

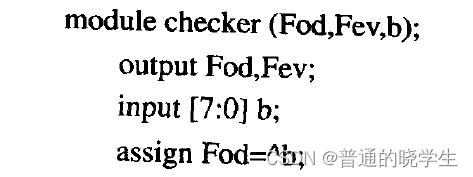

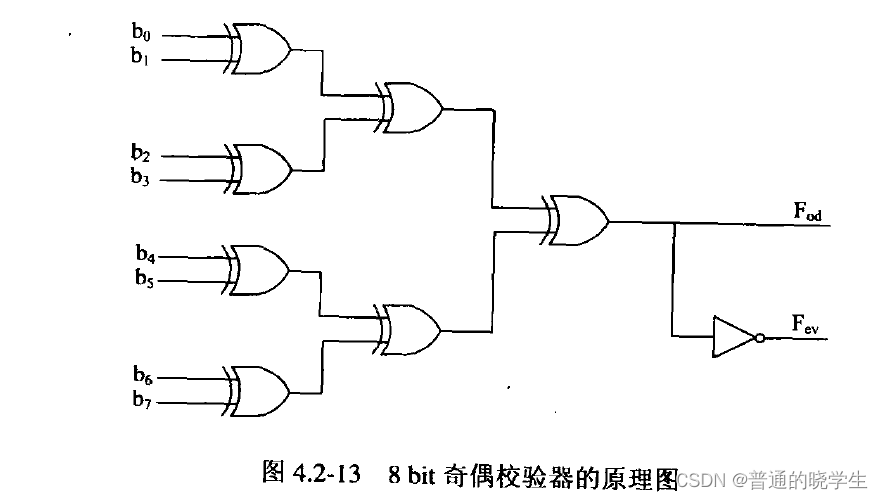

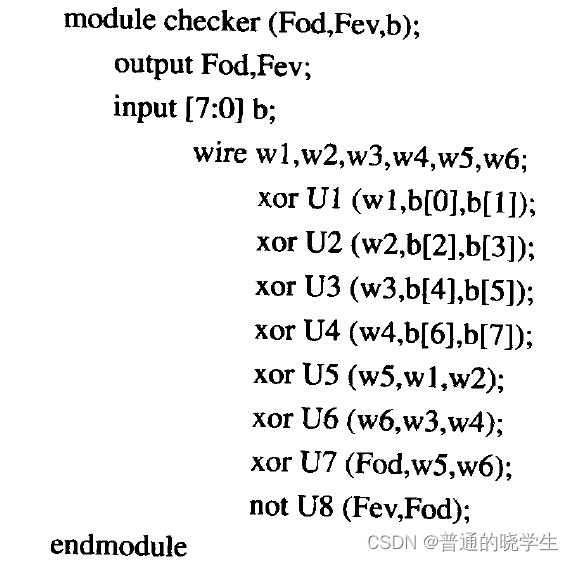

- 例:8bit奇偶校验器

- 对于一个奇校验器,就是判断1的个数,偶校验就是判断0的个数,所以就用异或电路,奇校验和偶校验就差了一个非

(1)结构描述方式

(2)抽象描述方式