为了帮助大家更好学习FPGA硬件语言,创立此资源

包含文件有:实验报告、仿真文件,资料很全,有问题可以私信

一、实验内容

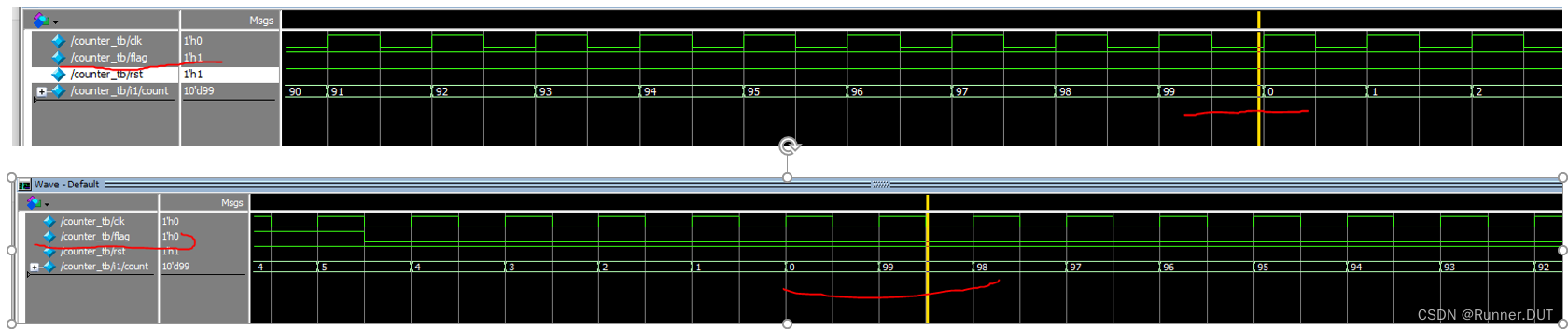

1、利用QuartusII和Modelsim实现100进制可逆计数器编码显示实验。

二、实验步骤

(1)安装软件

事先安装好QuartusII和Modelsim两个软件。

(2)创建工程

(3)编写代码

编写的.v顶层文件:

module counter_1(

input clk,

input rst,

input flag,

output out_c

);

reg [9:0] count;

always@(posedge clk or negedge rst)begin

if(!rst)begin

count <= 0; //复位

end

else if(flag==1)begin

if(count<99)

count <= count + 1; //flag为1,是加法计数器

else

count <= 0; //计到99复位

end

else begin

if(count==0)

count <= 99; //计到0复位

else

count <= count - 1; //flag为0,是减法计数器

end

end

endmodule

编写的textbench文件:

`timescale 1 ns/ 1 ps

module counter_tb();

// constants

// general purpose registers

// test vector input registers

reg clk;

reg flag;

reg rst;

// wires

wire out_c;

// assign statements (if any)

counter_1 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.flag(flag),

.out_c(out_c),

.rst(rst)

);

initial

begin

// code that executes only once

// insert code here --> begin

clk = 0;

rst = 0;

#100 rst = 1;

flag = 1;

#1000 flag =0; //初始化

// --> end

end

always #5000 flag = ~flag; //每5000ns之后flag翻转

always #10 clk = ~clk; //时钟周期20ns

endmodule三、实验结果