SDRAM的特性(容量大、价格低、掉电易失性、随机读写、总线式访问)

SDRAM/DDR都属于动态内存(相对于静态内存SRAM),都需要先运行一段初始化代码来初始化才能使用,不像SRAM开机上电后就可以直接运行。类似于SDRAM和SRAM的区别的,还有NorFlash和NandFlash(硬盘)这两个。

正是因为硬件本身特性有限制,所以才导致启动代码比较怪异、比较复杂。而我们研究裸机是为了研究uboot,在uboot中就充分利用了硬件的各种特性,处理了硬件复杂性。

SDRAM数据手册K4T1G164QQ

SDRAM在系统中属于SoC外接设备(外部外设。以前说过随着半导体技术发展,很多东西都逐渐集成到SoC内部去了。现在还长期在外部的一般有:Flash、SDRAM/DDR、网卡芯片如DM9000、音频Codec。现在有一些高集成度的芯片也试图把这几个集成进去,做成真正的单芯片解决方案。)

SDRAM通过地址总线和数据总线接口(总线接口)与SoC通信。

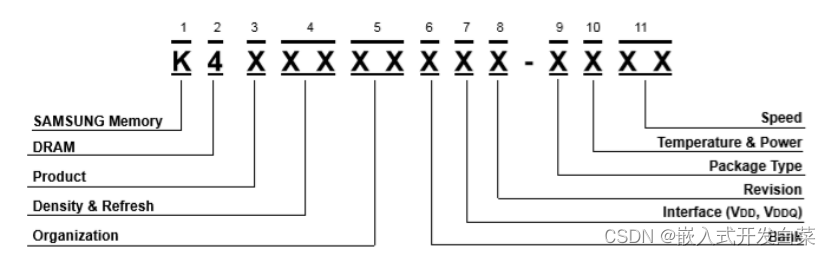

K4T1G164QE:

K表示三星产品,4表示是DRAM,T表示产品号码,1G表示容量(1Gb,等于128MB,我们开发板X210上一共用了4片相同的内存,所以总容量是128×4=512MB)16表示单芯片是16位宽的,4表示是8bank

三星官方的数据手册上其实没有芯片相关的参数设置信心,都是芯片选型与外观封装方面的信息,选型是给产品经理来看的,封装和电压等信息是给硬件工程师看的。软件工程师最关注的是工作参数信息,但是数据手册没有。

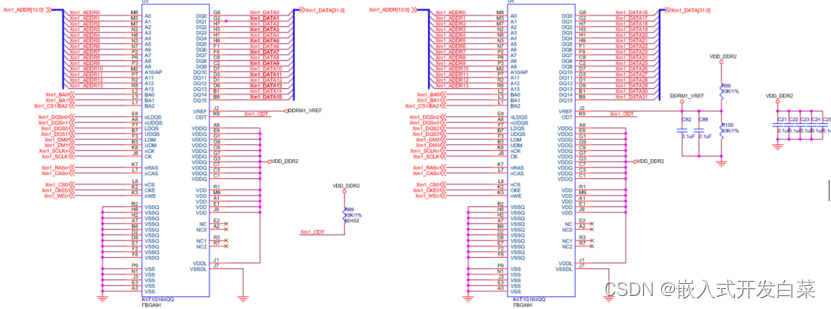

SDRAM原理图

S5PV210共有2个内存端口(就好像有2个内存插槽)。再结合查阅数据手册中内存映射部分,可知:两个内存端口分别叫DRAM0和DRAM1:

DRAM1:内存寻址范围:0x40000000~0x7fffffff(1024MB) ,对应引脚是Xm2xxxx

结论:

(1)整个210最多支持内存为1.5GB,如果给210更多的内存CPU就无法识别。

(2)我们所使用的X210开发板只有512MB内存,连接方法是在DRAM0端口分布256MB,在DRAM1端口分布了256MB。

(3)由(2)可知,X210开发板上合法地址是:0x20000000~0x2fffffff(256MB)+0x40000000~0x4fffffff(256MB)。当板子上DDR初始化完成之后,这些地址都是可以使用的;如果使用了其他地址譬如0x30004000就是死路一条。

原理图中每个DDR端口都是由3类总线构成地址总线(Xmn_ADDR0~XMnADDR13共14根地址总线) + 控制总线(中间部分,自己看原理图) + 数据总线(Xmn_DATA0~XMnDATA31共32根数据线)

分析:从数据总线的位数可以看出,我们用的是32位的(物理)内存。

原理图中画出4片内存芯片的一页,可以看出:X210开发板共使用了4片内存(每片1Gb=128MB,共512MB),每片内存的数据总线都是16位的(单芯片是16位内存)。如何由16位内存得到32位内存呢?可以使用并联方法。在原理图上横向的2颗内存芯片就是并联连接的。并联时地址总线接法一样,但是数据总线要加起来。这样连接相当于在逻辑上可以把这2颗内存芯片看成是一个(这一个芯片是32位的,接在Xm1端口上)。

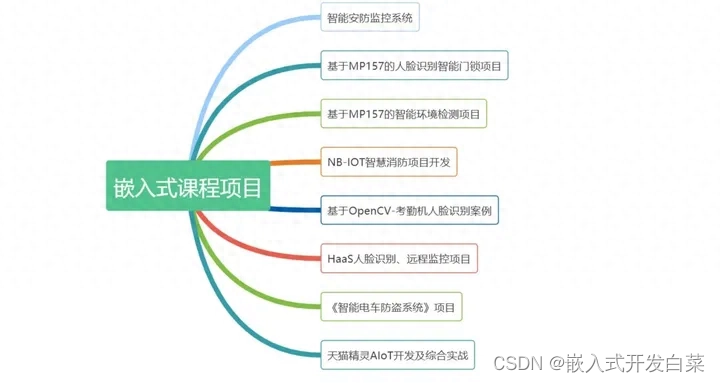

嵌入式物联网的学习之路非常漫长,不少人因为学习路线不对或者学习内容不够专业而错失高薪offer。不过别担心,我为大家整理了一份150多G的学习资源,基本上涵盖了嵌入式物联网学习的所有内容。点击这里扫码进群领资料,0元领取学习资源,让你的学习之路更加顺畅!记得点赞、关注、收藏、转发哦!