文章目录

- ODDR原语

- 1. OPPOSITE_EDGE 模式

- 2. SAME_EDGE 模式

ODDR原语

例化模板:

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

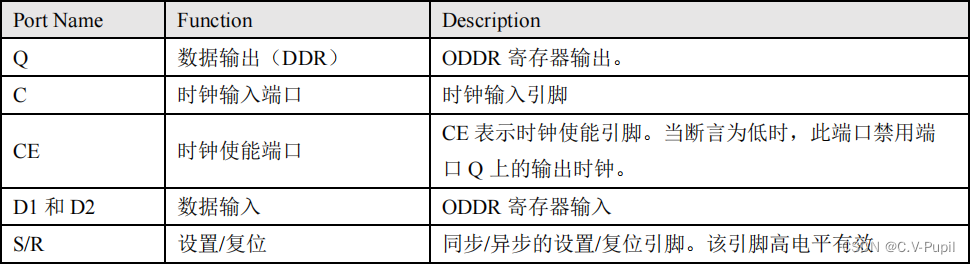

这里的 D1 和 D2 是数据的两个输入端口,输出端口会在上升沿这里需要注意的是 set和 reset 同时只能有一个被置高,也因此,描述端口时,使用的 S/R。除了这些端口外,ODDR原语还包含一些可用属性,

这里简单描述下 ODDR 的两种操作模式:

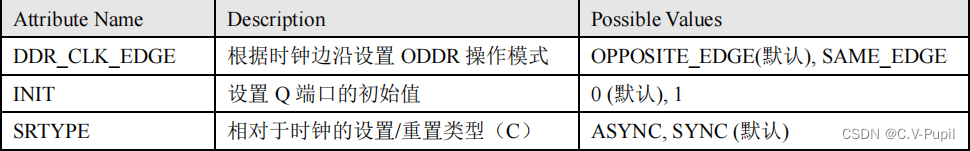

1. OPPOSITE_EDGE 模式

在该模式中,时钟的两个边沿被用来以两倍的吞吐量从 FPGA 逻辑中捕获数据。这种结构与 virtex-6 的实现比较相似。两个输出都提供给 IOB 的数据输入或者三态控制输入。使用OPPOSITE_EDGE 模式的输出 DDR 时序图如图 46-4 所示:

在该模式下,输入数据在两个边沿被采样,可以看到输出端 OQ 上首先输出的是 D1A,随后再输出 D2A。

该模式下,上升沿读取D1数据,并在时钟周期的前半个周期输出,下降沿读取D2数据,并在时钟周期的后半个周期输出。

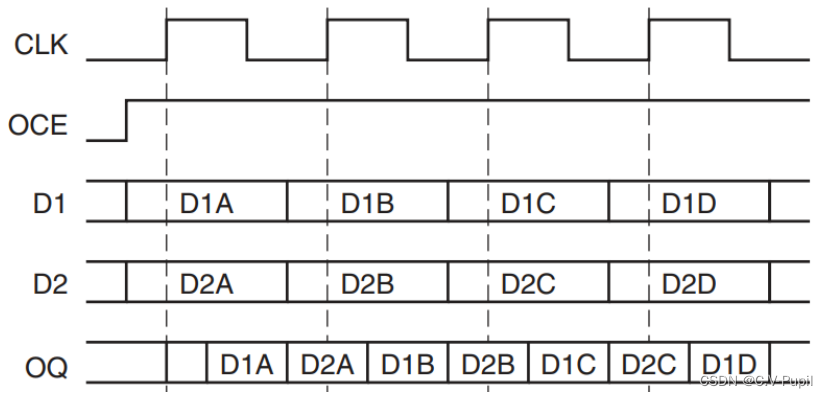

2. SAME_EDGE 模式

在该模式下,数据可以在相同的时钟边沿送给 IOB。相同的时钟沿将数据送给 IOB 可以避免建立时间违规,并允许用户使用最小的寄存器来执行更高的 DDR 频率来进行寄存器的延迟,而不是使用 CLB 寄存器。图 46-5 显示了使用 SAME_EDGE 模式的输出 DDR 的时序图:

可以看到,在该模式下,输出端 OQ 同样也是先输出 D1 端采集到的值,再输出 D2 端采集到的值。

该模式下,时钟周期的上升沿同时读取D1,D2数据,并在前半个时钟周期输出D1,后半个时钟周期输出D2。

用法举例说明:

一般我们使用GMII在一个时钟周期内有8bit数据发送,当我们使用RGMII时需要发送4bit数据,此时我们可以用ODDR进行传输,使用4个ODDR例化。

genvar i;

generate

for (i = 0;i < 4;i= i+1)

begin : ODDR_rgmii_txd

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0 ), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_rgmii_txd (

.Q(rgmii_txd[i] ), // 1-bit DDR output

.C(gmii_tx_clk ), // 1-bit clock input

.CE(1'b1 ), // 1-bit clock enable input

.D1(gmii_txd[i] ), // 1-bit data input (positive edge)

.D2(gmii_txd[i+4]), // 1-bit data input (negative edge)

.R(~reset_n ), // 1-bit reset

.S(1'b0 ) // 1-bit set 与R不能同时为1

);

end

endgenerate