$test$plusargs和$value$plusarg的区别和使用

本文参考的文章vcs2021 user guiger 别的版本可能会有不一样

纯学习笔记

文章原文

(

t

e

s

t

test

testplusargs)

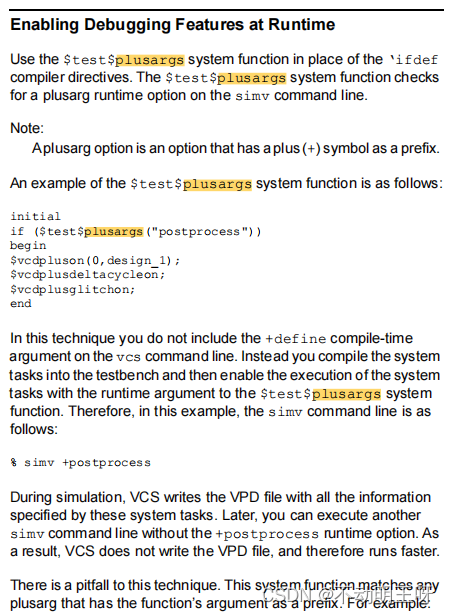

在运行时启用调试功能

在“ifdef”编译器指令的位置使用

t

e

s

t

test

testplusargs系统函数。

t

e

s

t

test

testplusargs系统函数检查simv命令行上是否有plusarg运行时选项。

注意:

加号(+)符号作为前缀的选项称为plusarg选项。

t

e

s

t

test

testplusargs系统函数的示例如下:

initial

if (

t

e

s

t

test

testplusargs(“postprocess”))

begin

$vcdpluson(0,design_1);

$vcdplusdeltacycleon;

v

c

d

p

l

u

s

g

l

i

t

c

h

o

n

;

e

n

d

在这种技术中,您不需要在

v

c

s

命令行上包含

+

d

e

f

i

n

e

编译时参数。相反,您将系统任务编译到测试台中,然后使用

vcdplusglitchon; end 在这种技术中,您不需要在vcs命令行上包含+define编译时参数。相反,您将系统任务编译到测试台中,然后使用

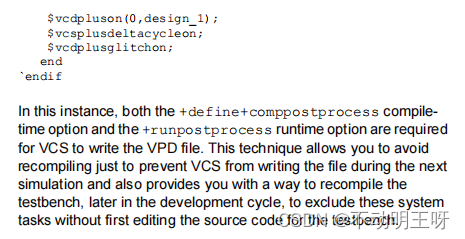

vcdplusglitchon;end在这种技术中,您不需要在vcs命令行上包含+define编译时参数。相反,您将系统任务编译到测试台中,然后使用test$plusargs系统函数的运行时参数启用系统任务的执行。因此,在这个示例中,simv命令行如下:

% simv +postprocess

在仿真期间,VCS根据这些系统任务指定的所有信息写入VPD文件。随后,您可以执行另一个不包含+postprocess运行时选项的simv命令行。因此,VCS不会写入VPD文件,因此运行速度更快。

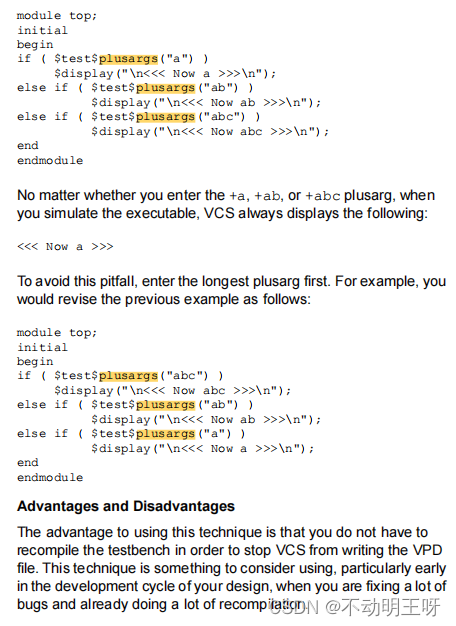

这种技术存在一个陷阱。这个系统函数匹配任何具有函数参数作为前缀的plusarg。例如:

module top;

initial

begin

if (

t

e

s

t

test

testplusargs(“a”) )

$display(“\n<<< Now a >>>\n”);

else if (

t

e

s

t

test

testplusargs(“ab”) )

$display(“\n<<< Now ab >>>\n”);

else if (

t

e

s

t

test

testplusargs(“abc”) )

$display(“\n<<< Now abc >>>\n”);

end

endmodule

无论您输入+a、+ab还是+abc plusarg,当您仿真可执行文件时,VCS始终显示以下内容:

<<< Now a >>>

为了避免这个陷阱,先输入最长的plusarg。例如,您可以将上面的示例修改如下:

module top;

initial

begin

if (

t

e

s

t

test

testplusargs(“abc”) )

$display(“\n<<< Now abc >>>\n”);

else if (

t

e

s

t

test

testplusargs(“ab”) )

$display(“\n<<< Now ab >>>\n”);

else if (

t

e

s

t

test

testplusargs(“a”) )

$display(“\n<<< Now a >>>\n”);

end

endmodule

优点和缺点

使用这种技术的优点是,您不必重新编译测试台,以停止VCS写入VPD文件。特别是在设计的早期开发周期中,当您正在修复许多错误并已经进行了大量重新编译时,这是值得考虑的技术。

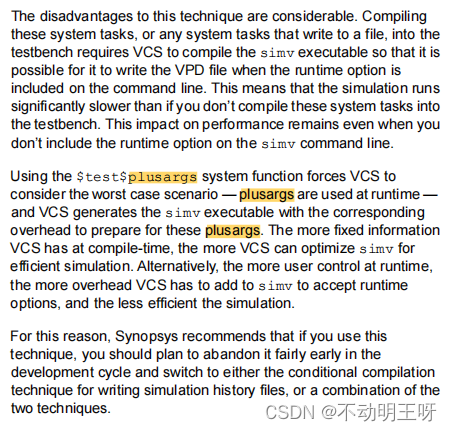

这种技术的缺点相当明显。将这些写入文件的系统任务或任何写入文件的系统任务编译到测试台中,需要VCS编译simv可执行文件,以便在命令行中包含运行时选项时能够写入VPD文件。这意味着与不将这些系统任务编译到测试台中相比,仿真运行速度要慢得多。即使在simv命令行上不包含运行时选项时,性能影响仍然存在。

使用

t

e

s

t

test

testplusargs系统函数会迫使VCS考虑最坏情况——在运行时使用plusargs——并且VCS会生成带有相应开销的simv可执行文件,以准备处理这些plusargs。VCS在编译时获得的固定信息越多,VCS就能够更好地优化simv,以实现高效的仿真。或者,用户在运行时控制得越多,VCS在simv中添加运行时选项的开销就越大,仿真效率就越低。

因此,Synopsys建议如果使用这种技术,应计划在开发周期的早期放弃它,并切换到用于编写仿真历史文件的条件编译技术,或两种技术的组合。

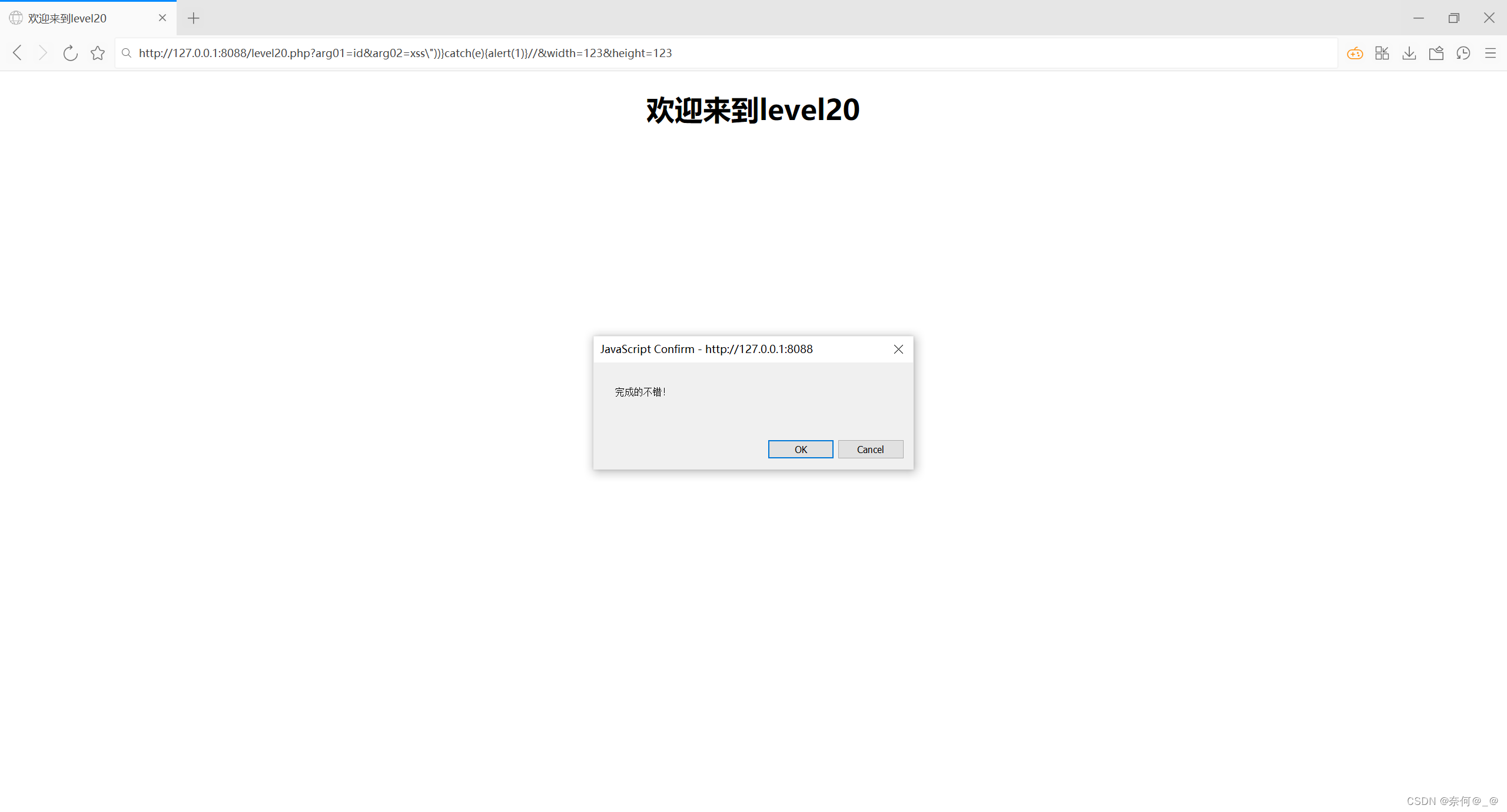

$value$plusargs

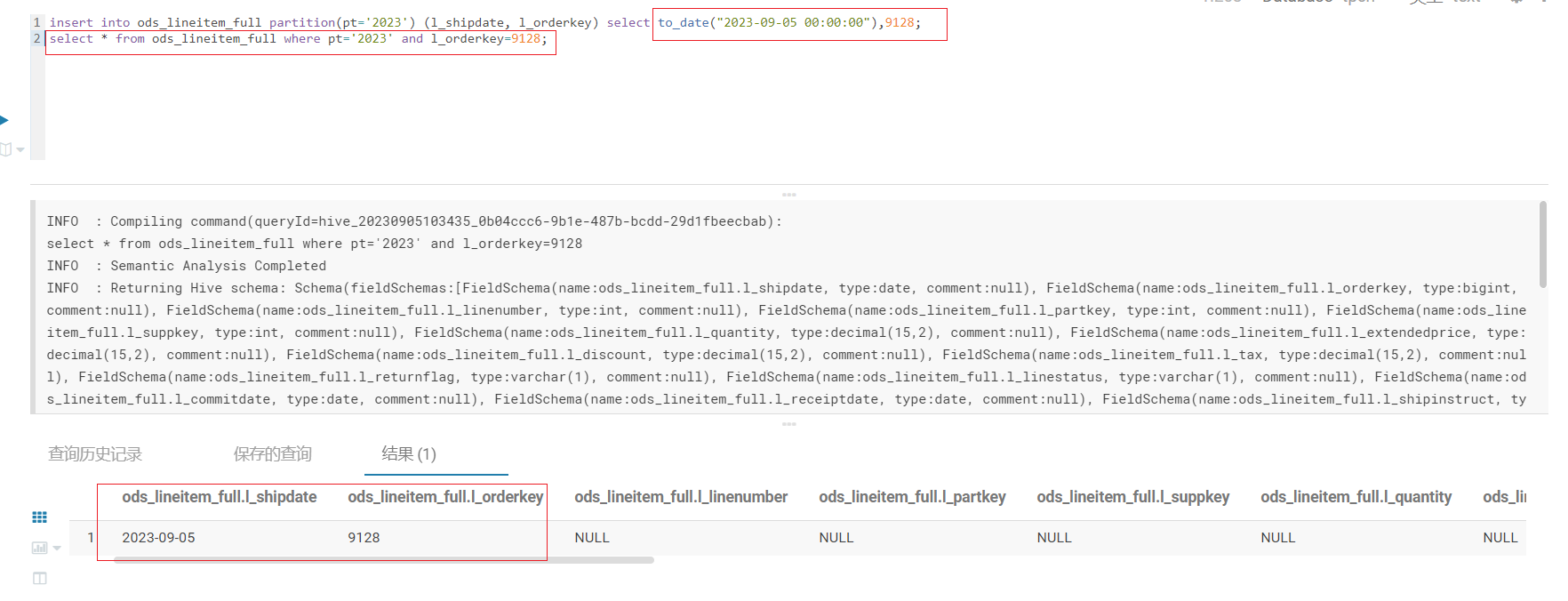

测试文件

module dut;

//$test$plusargs

initial

if ($test$plusargs("postprocess"))

begin

$display("postprocess");

end

//$value$plusargs

reg [31:0] r1;

integer status;

initial

begin

$monitor("r1=%0d at %0t",r1,$time);

#1 r1=0;

#1 status=$value$plusargs("r1=%d",r1);

end

endmodule

仿真指令

make comp

./simv +postprocess +r1=20

仿真结果

postprocess

r1=x at 0

r1=0 at 1

123

r1=20 at 2