参考文章:

聊一聊芯片后端的标准单元-standard cell - 知乎 (zhihu.com)

standard cell中的7T和9T中的"T"指的是什么?或者是什么的缩写? - Layout讨论区 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

数字后端基本概念介绍——Standard Cell_Tao_ZT的博客-CSDN博客

为什么会需要standard cell?

Standard cell,标准单元,或者简称cell,是数字芯片后端最基本的概念之一。我们为何要设定标准单元呢,以及这些cell是怎么应用到我们的后端设计中的呢?

首先,在芯片设计最早期,门电路不多,晶体管都靠手画在图纸上,所有芯片都是一些逻辑简单的全定制芯片的时代,是不存在什么标准单元的概念的。那时的工程师们只需要把一个一个的晶体管摆好,电路就可以正常工作了。但是随着集成化越来越高,所有的门电路都靠一个个手画变得非常不现实,一个非常朴素的想法就是把一些用过很多次的电路打包,就比如最基本的与或非门,我们要用的时候直接调用这个包就行了,就像复制粘贴一样,这就非常方便了。比如一个二输入与门,我只要设计好它的电路,画出它的版图,提取出来它的各项参数,就可以无限次的在整个芯片上复制了。而后,更进一步,我们可以把整个芯片所有可重用的部分都打包起来,为了方便我们摆放和连线,我们会制定一些规范化的rule,比如我们规定每个包要有固定的高度,称为row,宽度可以以一个CPP(栅极间距,contacted poly pitch)的距离变化,称为site。这样就成为了一个std cell。

Std cell可以大大简化我们的设计复杂度,它的意义,就像盖楼房的砖头,构成生物的细胞,画画的颜料一样。如果对于任何一个逻辑门都要求后端从头晶体管开始设计,那是真的无法想象的。目前所有的芯片已经全部采用了这种设计方式。但是,不可避免地,它会有一些资源的浪费,因为每一个cell都是有统一的设计规则,必然不能针对性的在一些小的方面进行优化。举个例子,在芯片的某个地方可以把pin出在cell左侧比较好route,但是这种cell设计的都是在右侧。当然,类似这样的影响在大型design中可以忽略了。

设计std cell是一件非常复杂的事,不亚于设计一款芯片的复杂程度。首先是电路的设计,schematic design。有一些具有相对复杂逻辑功能的cell,它的逻辑电路如何设计,如何兼顾PPA地进行设计,其实是很难的,设计结束后还要进行许多的验证之类。而后layout工程师要设计画出cell的版图。我们后端设计一般绕线层十几层顶天了,版图工程师要面对的是数不清的各种各样的层,有metal,有oxide,有poly,有n区有p区,应有尽有,还要考虑尽可能出pin M1或者M2出,低一点,给我们APR预留更多的绕线资源。而后还要有专门的工程师来进行cell 参数的提取,一般就是指power和timing的提取。Power应该主要就是leakage,timing就很麻烦了,需要在各个corner下,每个corner出一套它的各项参数。举个例子,一个cell的delay信息,基本需要在各个PVT条件下,测出各个引脚在各种逻辑状态下,input transition和output load各种情形下,cell的delay值。更别提一些OCV的信息,还有POCV的lvf信息了。最终所有这一切做好后,就可以生成cell的LIB文件了。结合cell的LEF文件(物理信息),我们后端就可以愉快的用这些cell搭积木啦。

我们后端在用的时候,这些cell就是一个一个的黑匣子,看不见内部,只能看到它的大小和出pin的信息。读入网表文件后,相应的cell就出现在我们的GUI界面了。对了,前端在综合的时候也需要读cell的lib。他们拿到的RTL代码不会指定一个与门要用哪种cell,比如我们目前有两种不同的与门cell,逻辑功能一样,但是有一些别的差异,综合工具就会全面考虑这一块电路,选用相应的cell作为那一段verilog代码里表示的与门。

standard cell中的7T和9T中的"T"指的是什么?或者是什么的缩写?

Q:

对标准单元所说的9 track和12 track是什么意思?(同一种工艺下)这两种单元有什么区别?

A: 7T指7个track, stand cell的高度。

P.S.,

一般site width就是metal 2 pitch ,比如SMIC18 的 0.56 x 5.04 , 0.56 就是metal 2 pitch,

因为std cell pin基本上都是由metal 2 连接出来的,

高度一般都是 site width的整数倍,比如7, 8, 9 , 10 ,12 倍,也就叫做7/8/9/10/12 track单元,

比如 0.56 x 5.04 的就是9 track, 0.56 x 3.92 的就是 7 track,

0.2 x 2.4 ( SMIC 65 ) 是12 track, 0.2 x 1.8 ( TSMC65) 是9 track,

区别主要是:

1)带不带tap (n/p well pickup) ,但是也不是绝对的,

比如SMIC18 sc-x 9 track带tap, sc-m 7track不带tap,不带tap的要用tapcell来偏置电位,

但是比如 TSMC40 nm的 12 track TCBNBWP12T ,也不带tap,

TSMC65 tcbn65bwp 9 track 带 tap,

2)一般来说9 track是 属于标准size, 7 track属于小size,也就是低功耗一些,速度慢些,

10、12 track 是高速, 一般 metal1的rail做的更宽, 管子好像没啥区别, rail做的宽,自然能走更多的电流,自然速度就快了, 功耗大了,有的还添加metal2 rail比如65nm以下的库, 这样速度更快了,

选几个track 是由设计目标决定的,如果简单些 ,就选9 track标准带tap的, 比较方便

低功耗选7 track,timing不够就选12 track的,

ARM的9 track叫sage-x , 7 track叫metro, 12 track叫POP (performance optimization packets),

Standard Cell在lib和lef中的表现形式

Standard cell是设计中最基本的逻辑单元了,是基本门和简单逻辑电路。我们平时常用的buffer, inverter, register等都属于标准单元。

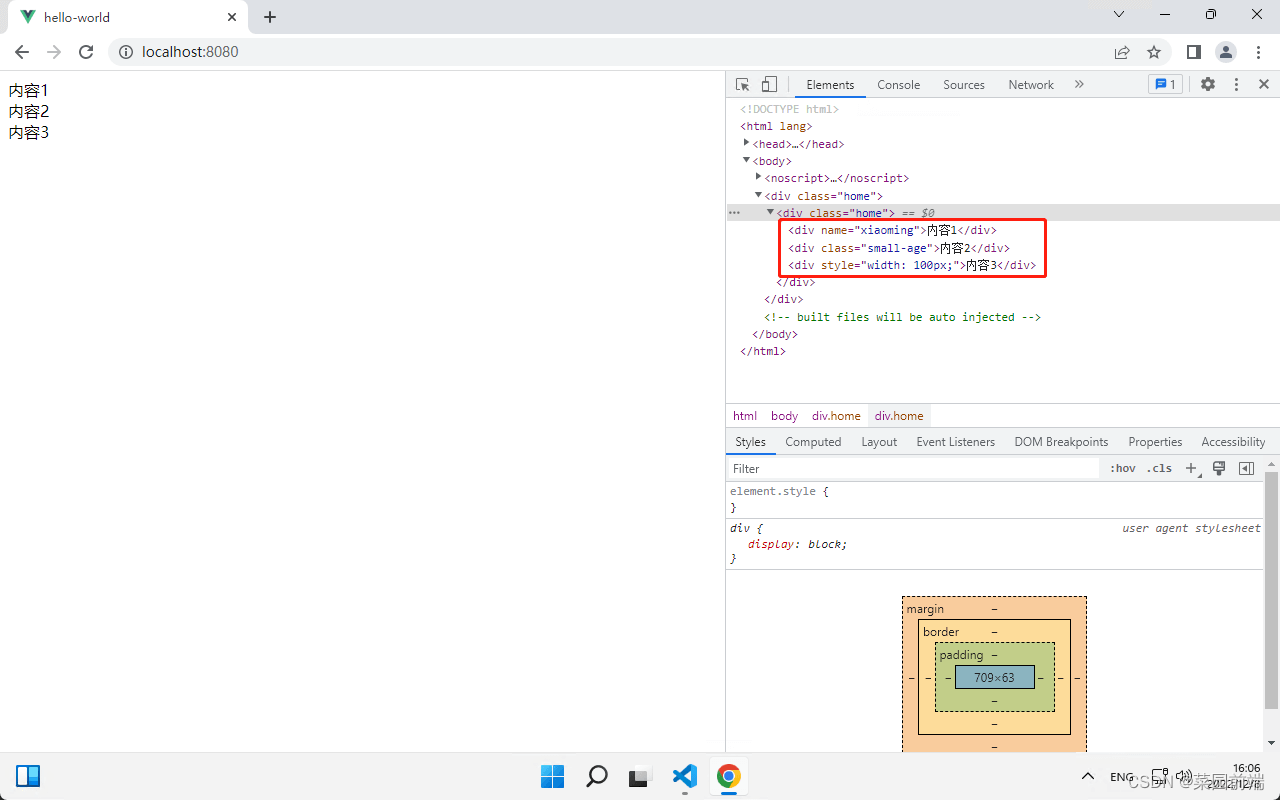

standard cell的时序信息记录在.lib文件中:

cell (INVX12_CSC28SL) {

area : 0.86528;

cell_footprint : "inv";

threshold_voltage_group : "LVT";

pg_pin (VDD) {

pg_type : primary_power;

voltage_name : "VDD";

}

...物理信息记录在lef文件中:

MACRO INVX12_CSC28SL

CLASS CORE ;

ORIGIN 0 0 ;

FOREIGN 0 0 ;

SIZE 1.26 BY 0.64 ;

SYMMETRY X Y ;

SITE unit ;

PIN VDD

DIRECTION INOUT ;

USE POWER ;

SHAPE ABUTMENT ;

PORT

LAYER M1 ;

RECT -0.052 0.6 1.612 0.68 ;standard cell在netlist中完成例化,INVX12_F_CSC28SL是cell名字,U28是例化以后的名字。

INVX12_F_CSC28SL U28(

.Z(n21), .A(n24)

);

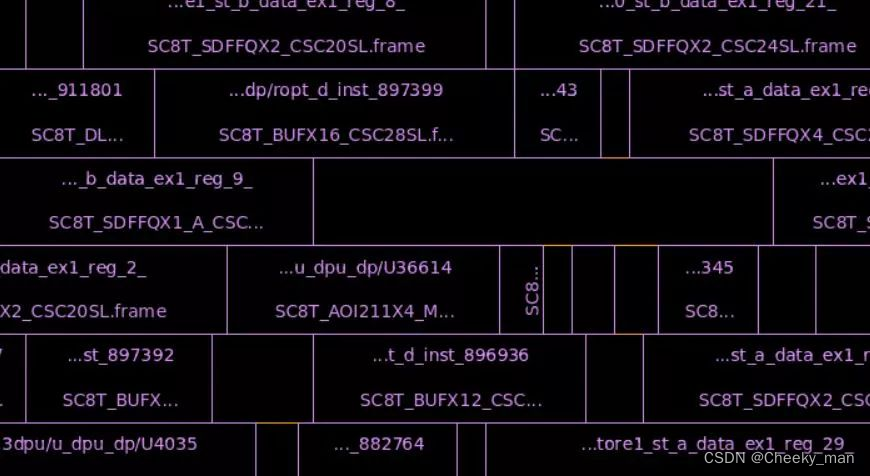

下图就是stardand cell在软件中的样子。他们被安放在row上