实验四 移位寄存器与计数器

一 实验目的

1 掌握任意进制计数器的构成方法;

2 熟悉双向移位寄存器的使用方法。

二 实验内容

1 任意进制计数器的构成方法:

用中规模集成计数器74HC161和与非门74LS00,构成十进制计数器。要求分别使用同步预置、异步清零两种功能来设计。用数码管显示。

实验验证分别用同步预置、异步清零两种方法设计的计数器。

(1)同步预置和异步清零的区别与实验设计思路

“同步”和“异步”是对于时钟而言的。“同步”输入信号和时钟信号有关,实际上输入信号和时钟信号进行了与运算或者与非运算,输入信号和时钟信号的运算结果是有效的,器件的状态才会改变。“异步”输入信号和时钟信号无关,是指输入信号变为有效状态,器件的状态就改变。

因此,同步预置需要下一个时钟的有效沿和预设条件达成才能完成置数;异步清零只需要预设条件达成就能完成置数。

由于本实验需要设计十进制计数器,所以与非门的输入需要对应的是计数器1010或1001输出信号。当与非门的输出接在Clear端的时候,产生低电平的状态是无效的,计数器马上就复位,对应的是异步清零电路,此时与非门的输对应的是计数器1010输出信号;当与非门的输出接在Load端的时候,产生低电平的状态是有效的,计数器需要等到下一个CLK信号才复位,对应的是同步预置电路,此时与非门的输对应的是计数器1001输出信号。

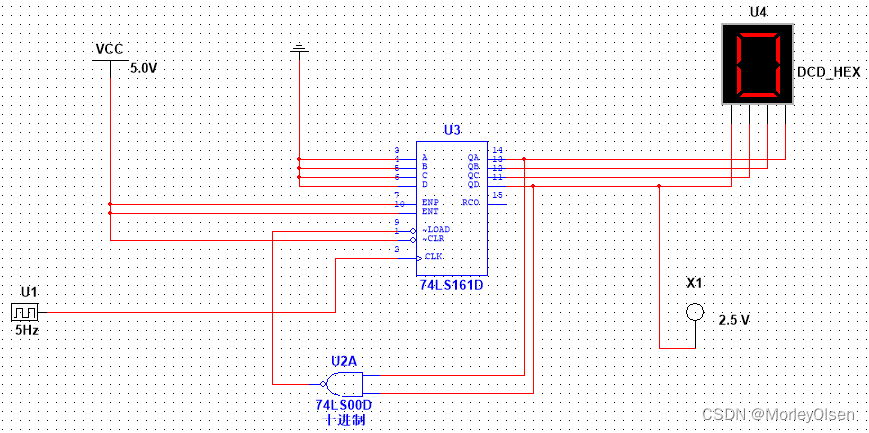

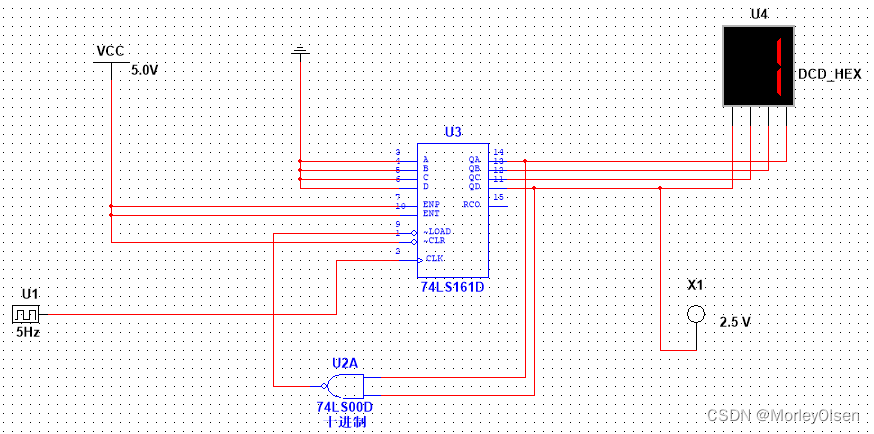

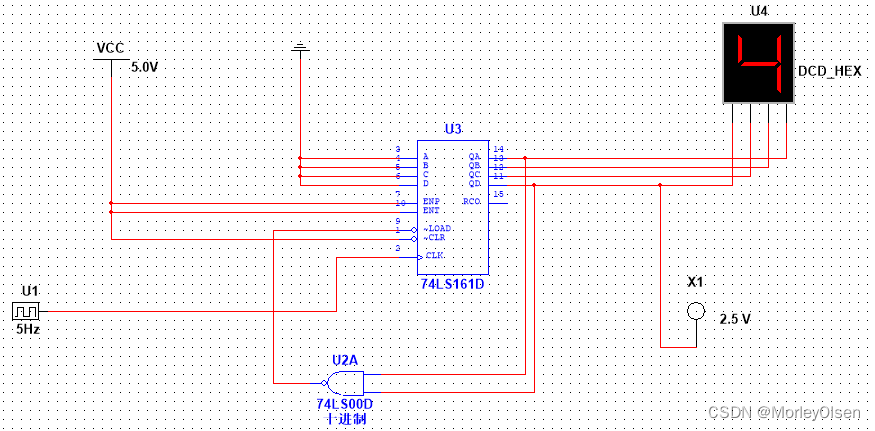

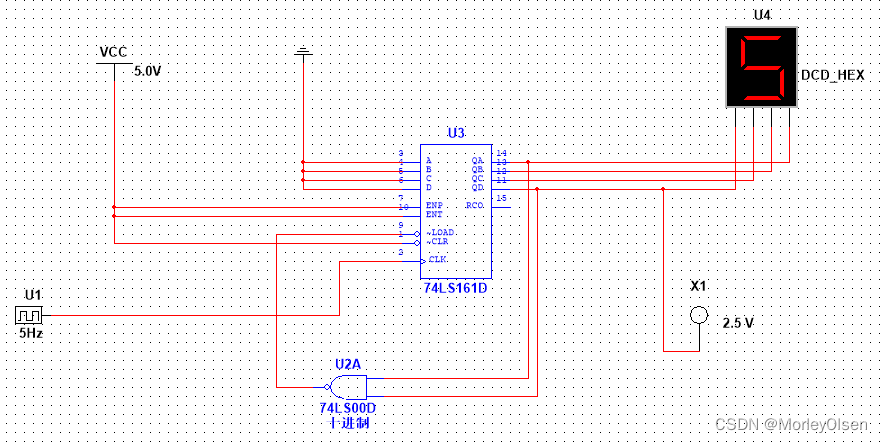

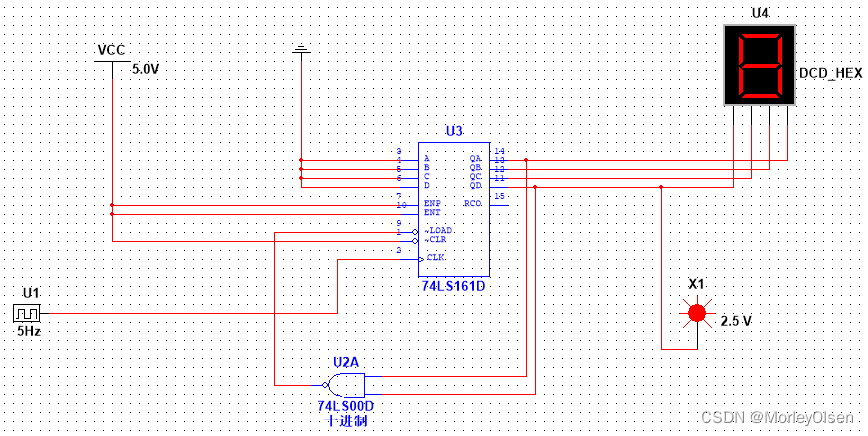

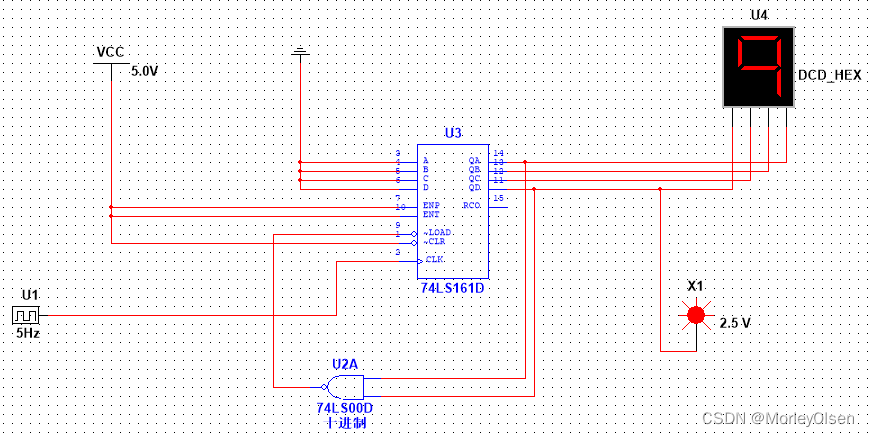

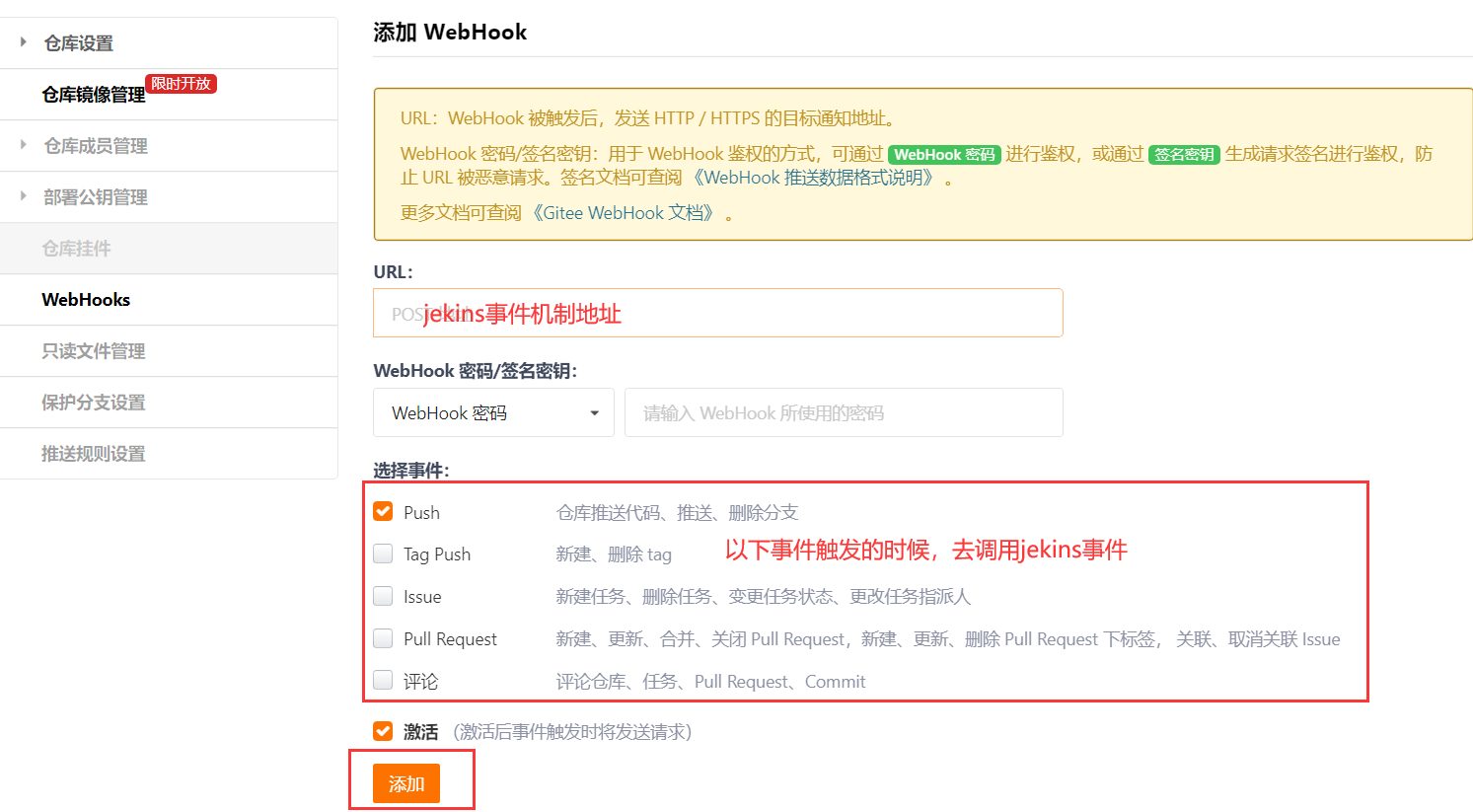

(2)Multisim电路图

根据上述分析,可以得到两种方法设计的计数器电路。最终电路结果如下面两个电路图所示。

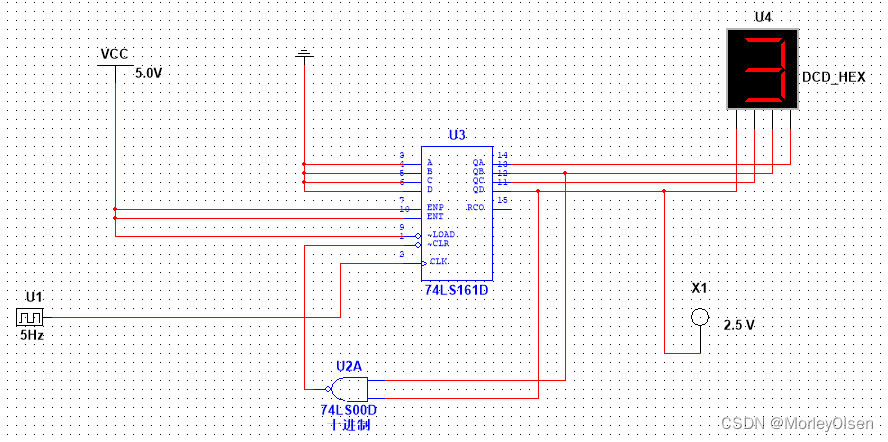

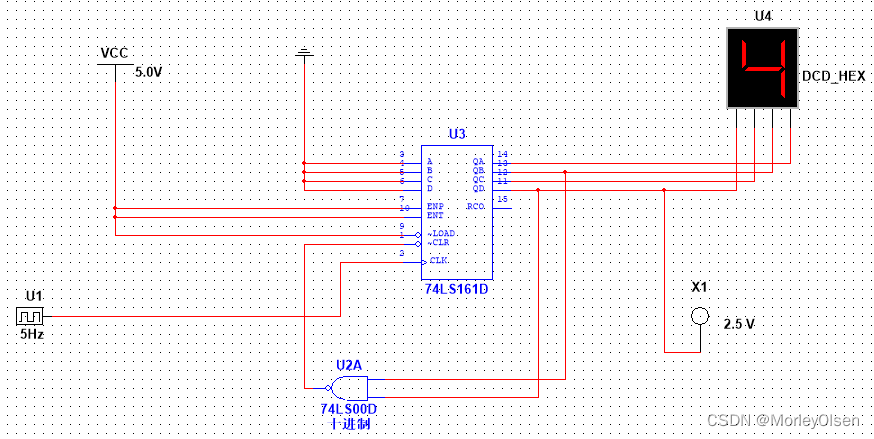

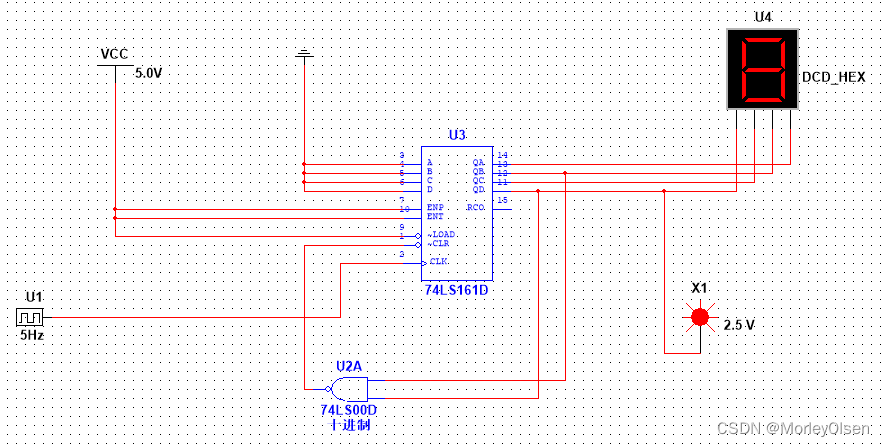

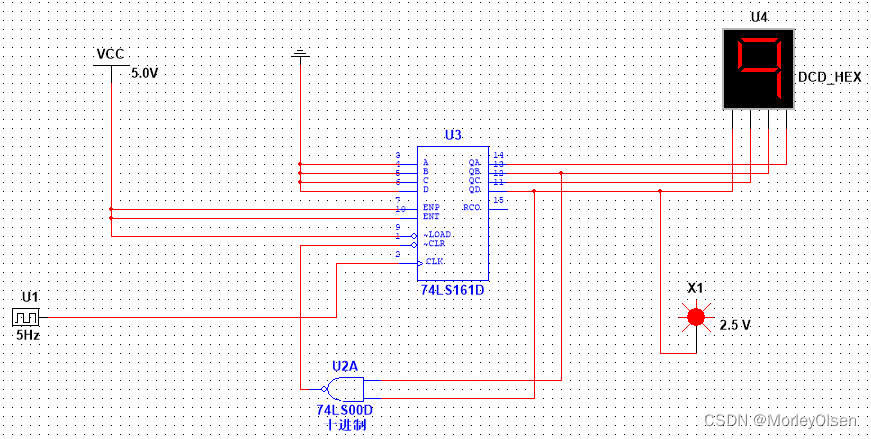

同步预置:

异步清零:

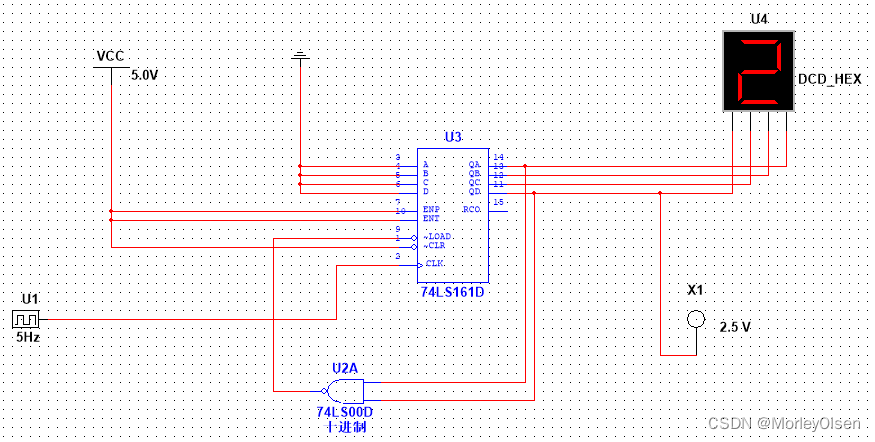

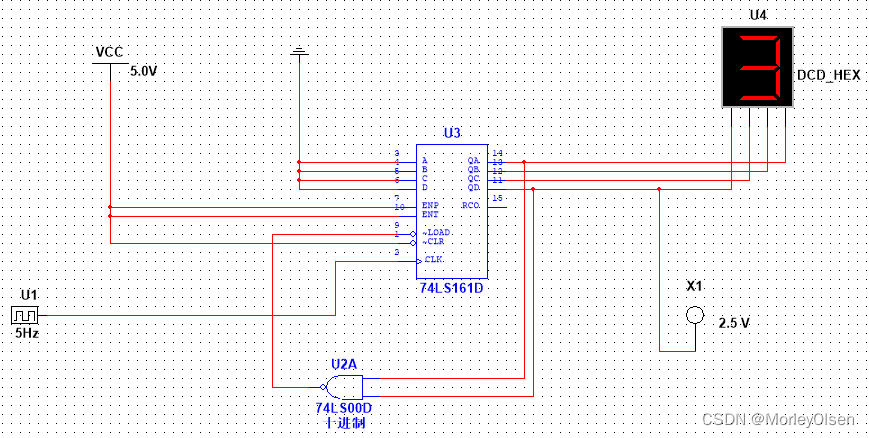

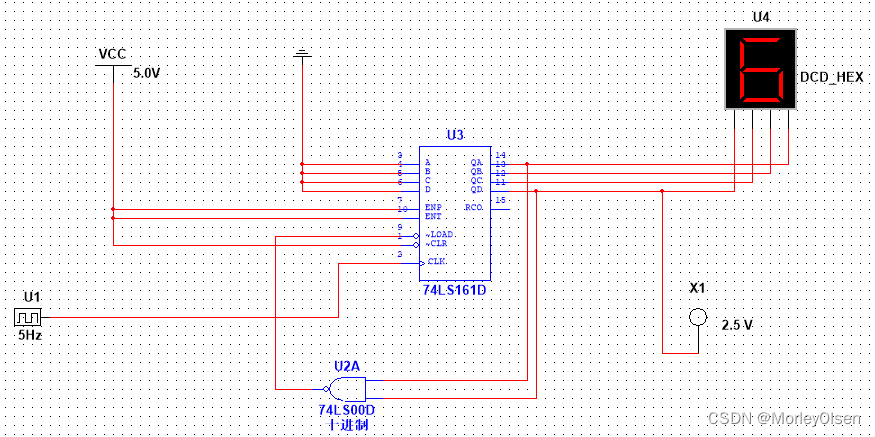

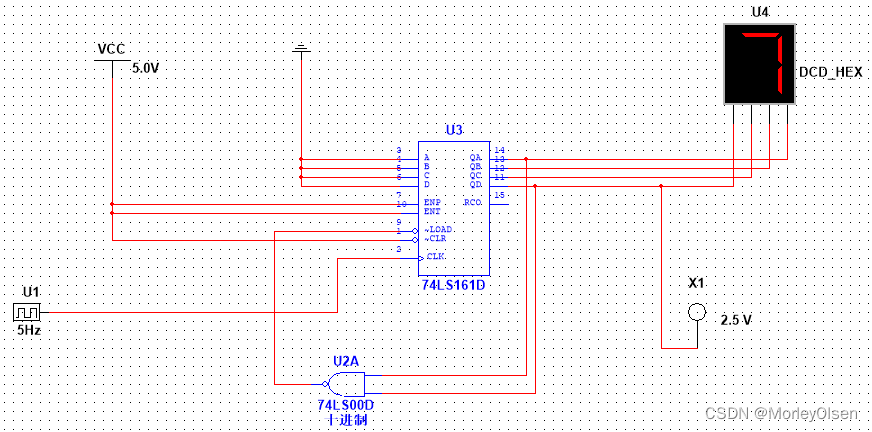

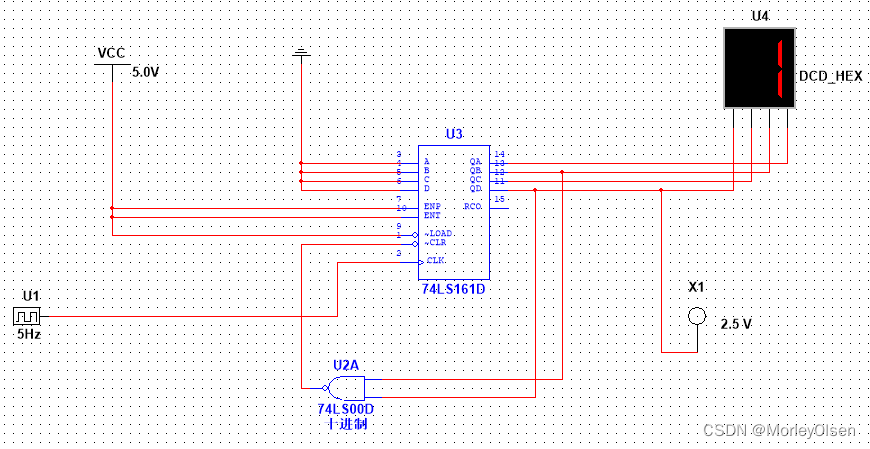

(3)仿真模拟过程

在软件中连接成以上电路图后,点击运行即可开始仿真。下面将依次展示两种设计方法实现的电路的每个步骤过程及电路对应的输出状态。

同步预置:

| 当前计数器输出信号 | 电路对应的输出状态 |

| 0000 |

|

| 0001 |

|

| 0010 |

|

| 0011 |

|

| 0100 |

|

| 0101 |

|

| 0110 |

|

| 0111 |

|

| 1000 |

|

| 1001 |

|

实验验证情况与预期情况完全拟合。另,同步预置电路的运行过程视频可见附件4-1-1.mkv。

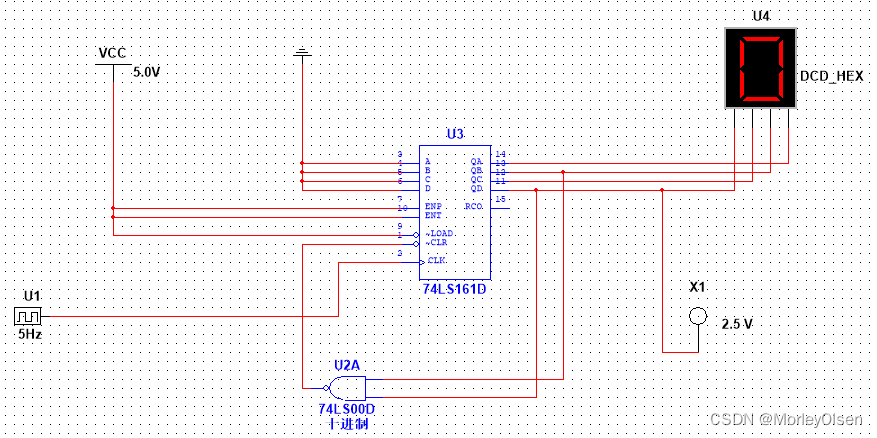

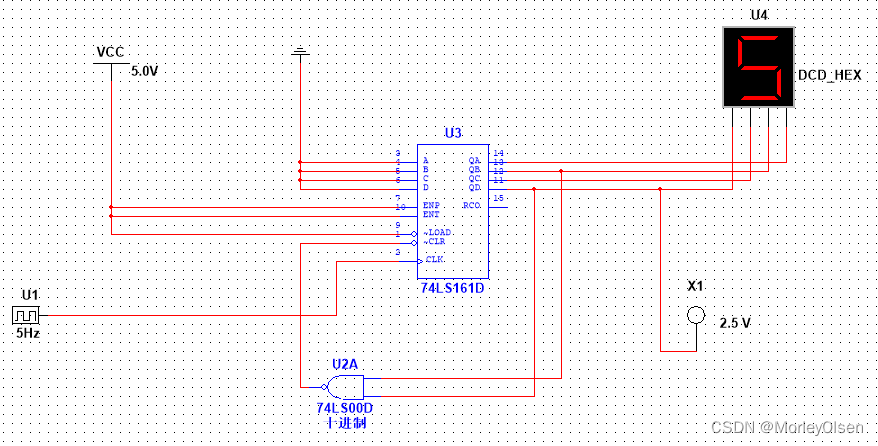

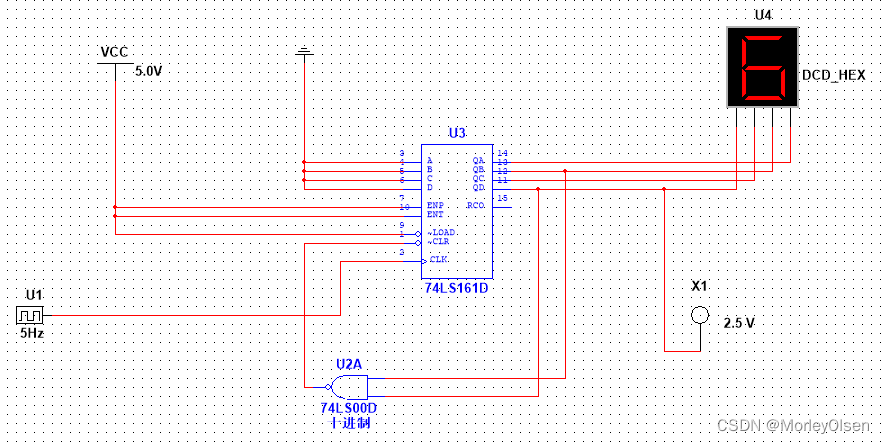

异步清零:

| 当前计数器输出信号 | 电路对应的输出状态 |

| 0000 |

|

| 0001 |

|

| 0010 |

|

| 0011 |

|

| 0100 |

|

| 0101 |

|

| 0110 |

|

| 0111 |

|

| 1000 |

|

| 1001 |

|

| 1010 | 不存在该状态,瞬间消失 |

实验验证情况与预期情况完全拟合。另,异步清零电路的运行过程视频可见附件4-1-2.mkv。

2 设计4位环形计数器:

用4位双向移位寄存器74HC194,设计一个能够自启动的4位环形计数器,并测试其输入CP和输出QA、QB、QC、QD的逻辑关系。

(1)双向移位寄存器的使用与实验设计思路

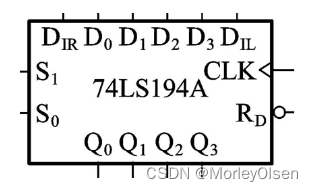

双向移位寄存器的结构如下图所示。

其工作原理为:S1=S0=1,Q1被选中;S1=S0=1,D1被选中,处于并行输入状态;S1=0,S0=1,Q0被选中,处于右移状态;S1=1,S0=0,Q2被选中,处于左移状态;RD’=0,触发器将被同时置0,处于复位状态。将五种状态总结成表格后,结果如下表所示。

| RD’ | S1 | S0 | 工作状态 |

| 0 | X | X | 置零 |

| 1 | 0 | 0 | 保持 |

| 1 | 0 | 1 | 右移 |

| 1 | 1 | 0 | 左移 |

| 1 | 1 | 1 | 并行输入 |

由于本实验需要设计一个能够自启动的环形计数器,因此可以采用双向移位寄存器的右移功能来循环信号。通过分析,可以将QD接在右移的输入端。同时,在电路启动前,因为第一个与非门有一个输入端为0,因此第一个与非门的输出为1,致使S0=S1=1,此时执行并行输入的功能,读取A、B、C、D各端的信号(0111)并输入。之后Q端并行输出对应的A、B、C、D信号,且Q端经过第二个与非门。在启动电路启动后,第一个与非门的两个输入均为1,因此第一个与非门的输出为0,致使S0=0且S1=1,此时双向移位寄存器执行右移的功能,并每来一个时钟就右移一位数字,同时把末位的数字移到首位。

理论移位情况为:0111->1011->1101->1110->0111。

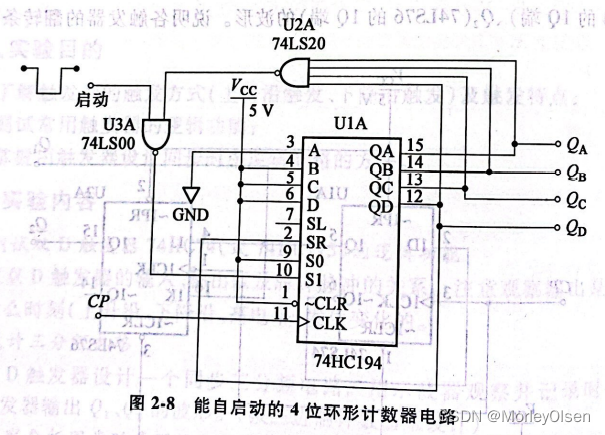

(2)理论电路图和Multisim电路图

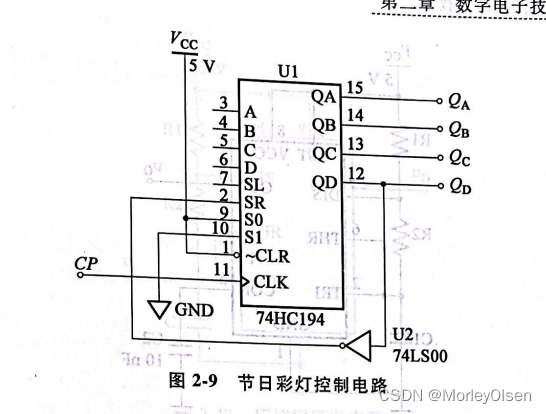

理论电路图:

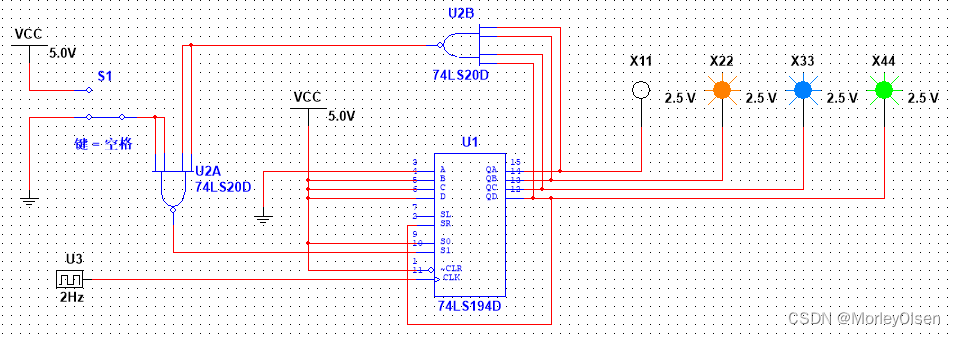

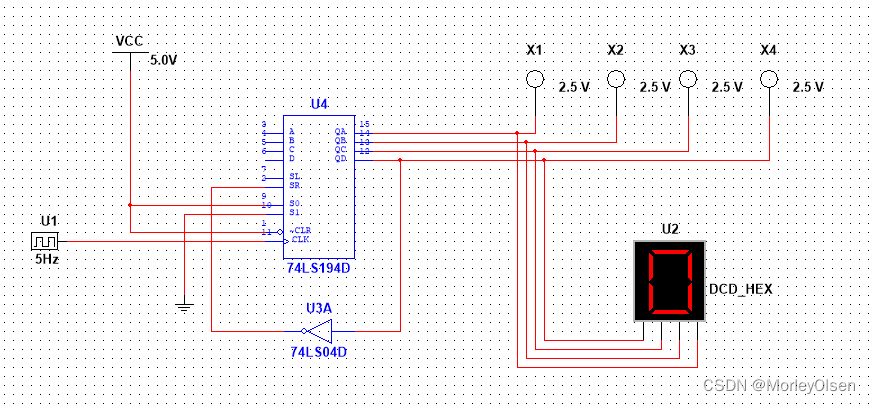

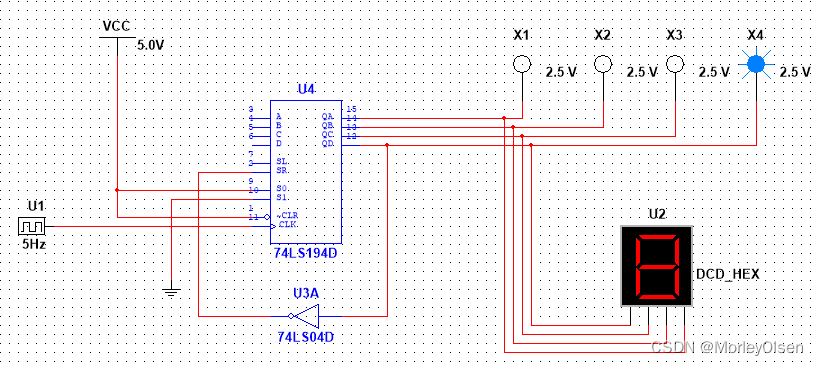

Multisim电路图:

(3)仿真模拟过程

在软件中连接成以上电路图后,点击运行即可开始仿真。下面将依次展示每个步骤过程及电路对应的输出状态。

启动前:

0:输出信号为0111;

启动后:

1:输出信号为0111;

2:输出信号为1011;

3:输出信号为1101;

4:输出信号为1110;

实验验证情况与预期情况完全拟合。另,4位环形计数器的运行过程视频可见附件4-2.mkv。

(4)输入CP和QA、QB、QC、QD的逻辑关系

根据模拟仿真实验的运行过程中可知,当CP每输入一个上升沿信号时,双向移位寄存器执行一次右移功能,使得Q端的各位输出均右移一位,并把末位的数字移到首位中,即实现一次环形计数功能。

3 设计节日彩灯控制电路:

用4位双向移位寄存器74HC194和与非门74LS00,设计一个节日彩灯控制电路。要求:当输入连续脉冲时,输出端的4个发光二极管右移逐位亮,继而右移逐位灭。将实现结果绘制成状态转换图。

(1)实验设计思路

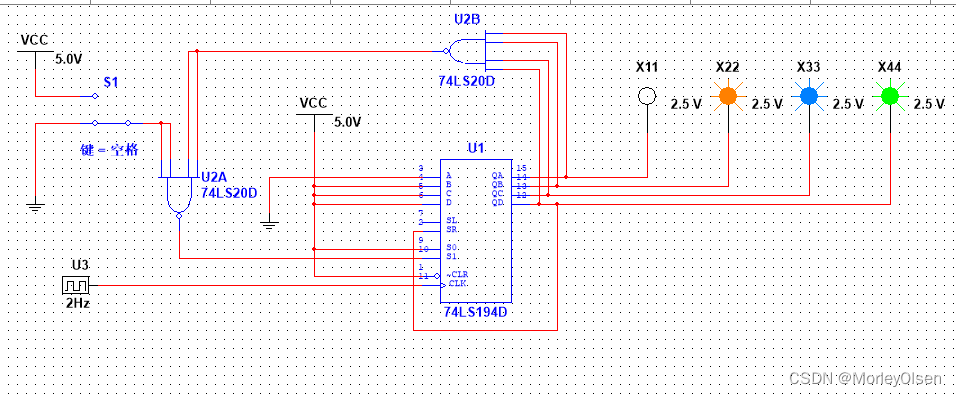

根据本实验要求可知,4个发光二极管右移逐位亮,继而右移逐位灭,因此双向移位寄存器需要执行右移功能,则令S0=1,S1=0,同时QD反向之后接在SR上。电路初始时,Q端的输出均为0,此时SR为1。电路刚开始执行时,每来一个CLK上升沿信号,Q端的输出均向右移一位,同时首位为SR=1的输入信号,直到四个彩灯均点亮为止。当QD=1时,经过反向器后SR会变成0,因此当下一个CLK上升沿信号来临时,Q端的输出依然均向右移一位,同时首位为SR=0的输入信号,直到四个彩灯均熄灭为止。所以,通过上述分析我们不难发现,该电路会依次经过8个状态,即四个彩灯依次点亮的过程加上四个彩灯依次熄灭的过程。

由于是设置节日彩灯,因此使用不同颜色的发光二极管probe显示输出,并通过DCD_HEX观察不同输出情况时Q端所对应的信号值。理论的输出probe情况和DCD_HEX情况如下表所示。

| CLK | SR | QA | QB | QC | QD | 点亮的probe序号 | 显示器的显示内容 |

| 初始状态 | 1 | 0 | 0 | 0 | 0 | / | 0 |

| ↑ | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| ↑ | 1 | 1 | 1 | 0 | 0 | 1、2 | 3 |

| ↑ | 1 | 1 | 1 | 1 | 0 | 1、2、3 | 7 |

| ↑ | 1(下一个CLK来临前变为0) | 1 | 1 | 1 | 1 | 1、2、3、4 | F(15) |

| ↑ | 0 | 0 | 1 | 1 | 1 | 2、3、4 | E(14) |

| ↑ | 0 | 0 | 0 | 1 | 1 | 3、4 | C(12) |

| ↑ | 0 | 0 | 0 | 0 | 1 | 4 | 8 |

| ↑ | 0(下一个CLK来临前变为1) | 0 | 0 | 0 | 0 | / | 0 |

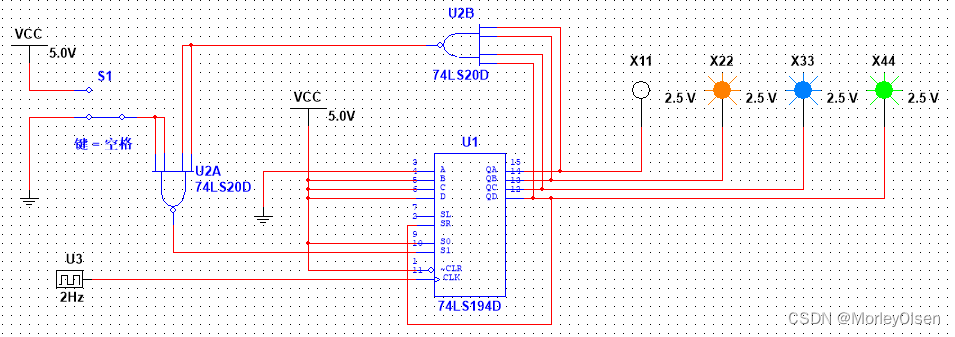

(2)理论电路图和Multisim电路图

理论电路图:

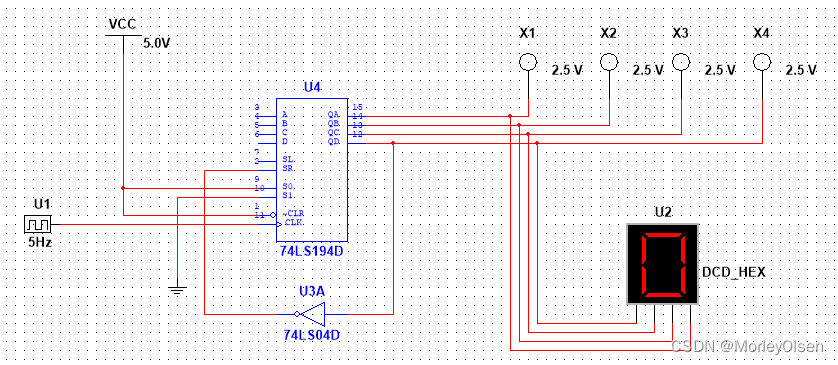

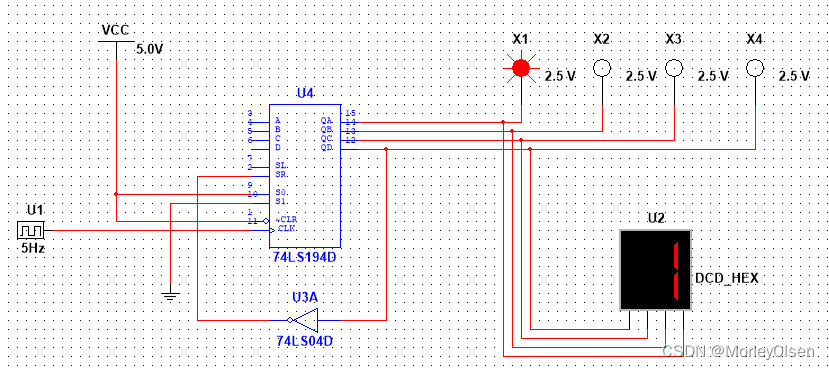

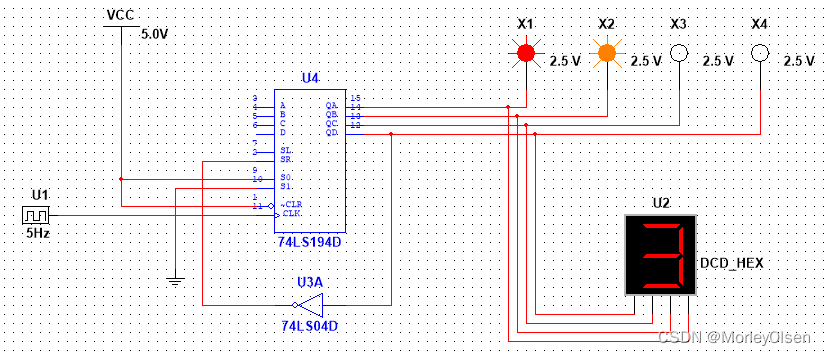

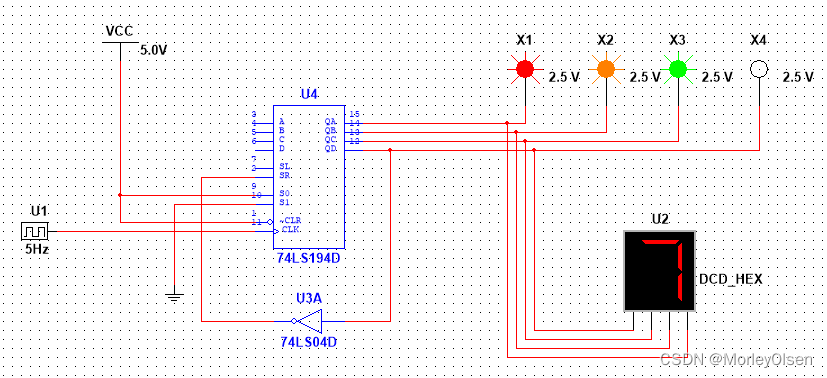

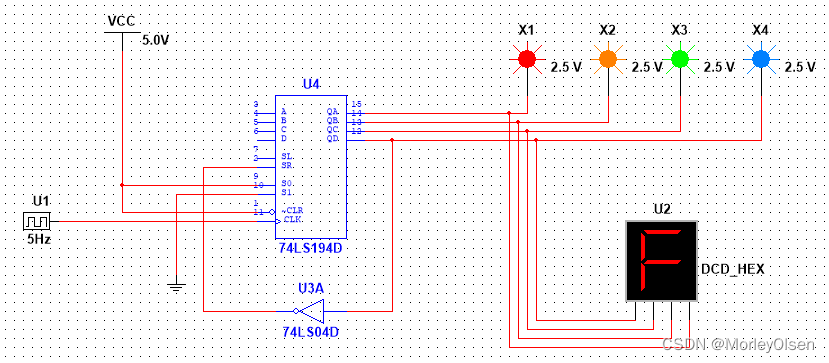

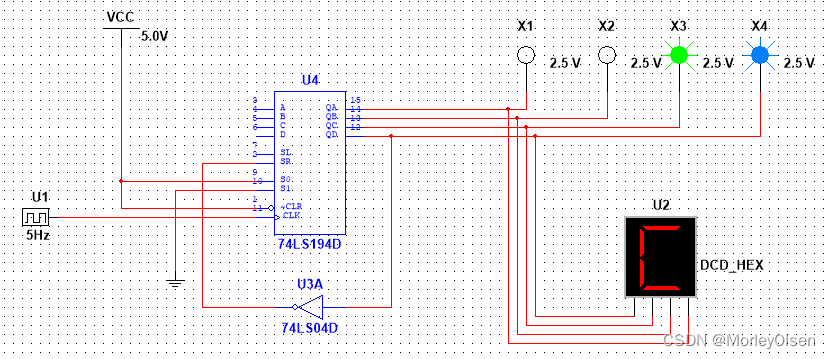

Multisim电路图:

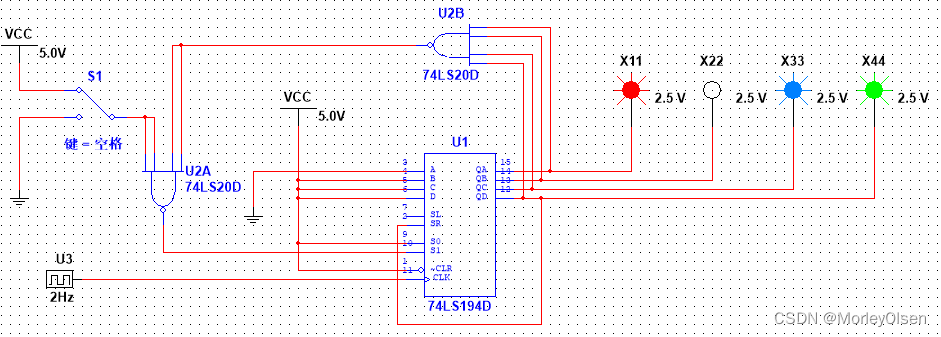

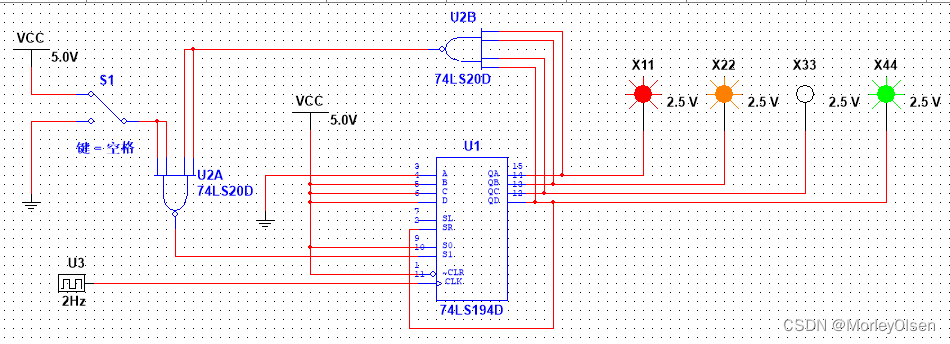

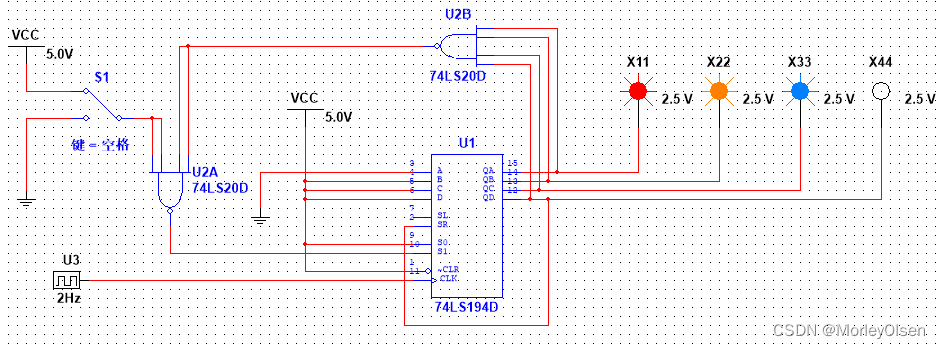

(3)仿真模拟过程

在软件中连接成以上电路图后,点击运行即可开始仿真。下面将依次展示每个步骤过程及电路对应的输出状态。

0:电路初始状态,彩灯均未被点亮。

1:第一个彩灯点亮。

2:第二个彩灯点亮。

3:第三个彩灯点亮。

4:第四个彩灯点亮。

5:第一个彩灯熄灭。

6:第二个彩灯熄灭。

7:第三个彩灯熄灭。

8:第四个彩灯熄灭。彩灯从左往右依次点亮并熄灭的一个过程结束,回到电路原来的初始状态。

实验验证情况与预期情况完全拟合。另,4位环形计数器的运行过程视频可见附件4-3.mkv。

(4)实验结果及状态转换图

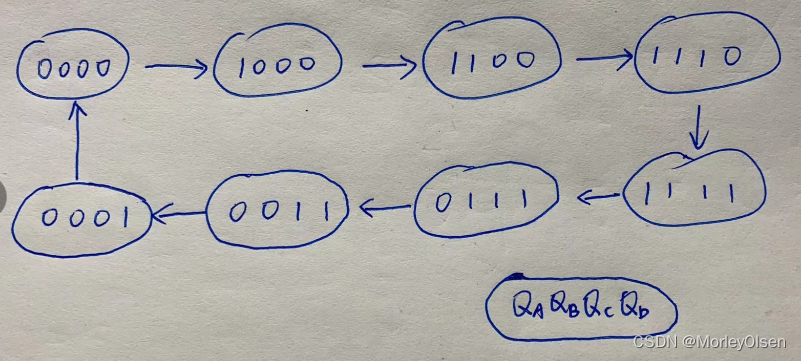

根据模拟仿真实验的运行过程中可知,Q端输出信号依次对应为0000->1000->1100->1110->1111->0111->0011->0001->0000。通过上述变化过程可以得到状态转换图如下图所示。由于输出即为Q端信号,因此不在状态转换图中展示输出变化。

三 实验总结

通过本次实验,我再一次对移位寄存器和计数器的功能进行了巩固。移位寄存器是用来寄存二进制数字信号且能进行信息移动的时序逻辑电路。根据移位寄存器存取信息的方式不同,可以分为串入串出、串入并出、并入串出、并入并处这四种形式。因此,移位寄存器可以构成计数器、顺序脉冲发生器、串行累加器、串并转换器、并串转换器等功能仪器。

另外,在第三个实验中,与非门的两个输入端均为同一种输入时,可作为反向器使用。即反相器为与非门的特殊连接情况。

同时,我对实验教材中的《实验七:Vivado工具与Verilog HDL的使用》进行了阅读,了解到Minisys实验板的使用步骤为:创建一个项目->添加源代码->仿真->综合->引脚分配->实现->产生比特流文件并下载,并对实验板的结构进行了粗略的认识。