相关阅读

Verilog基础专栏![]() https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12263729.html?spm=1001.2014.3001.5482

由于Verilog HDL标准中对语法的描述使用了Backus Naur Form(BNF)。本文将对其中的约定进行描述。

- 小写单词,其中一些包含嵌入的下划线,用于表示语法类别。例如:module_declaration

- 粗体字用于表示保留的关键字、运算符和标点符号,它们作为语法的必要部分。例如:module => ;

- 竖线用于分隔备选项目,除非它以粗体显示,在这种情况下,它代表自己。例如:unary_operator ::= + | - | ! | ~ | & | ~& | | | ~| | ^ | ~^ | ^~

- 方括号包含可选项目。例如:input_declaration ::= input [range] list_of_variables;

- 大括号({ })将重复项括起来,除非它以粗体显示,在这种情况下,它代表自己。大括号内的项目可能出现零次或多次;这与等价的左递归规则一样,重复从左到右发生(即用自己定义自己)。因此,以下两条规则是等效的: list_of_param_assignments ::= param_assignment { , param_assignment } list_of_param_assignments ::= param_assignment | list_of_param_assignment , param_assignment

- 如果任何类别的名称以斜体部分开头,则相当于没有斜体部分的类别名称(可以忽略斜体部分)。斜体部分旨在传达一些语义信息。例如,“msb_index”和“lsb_index”等同于“index”。

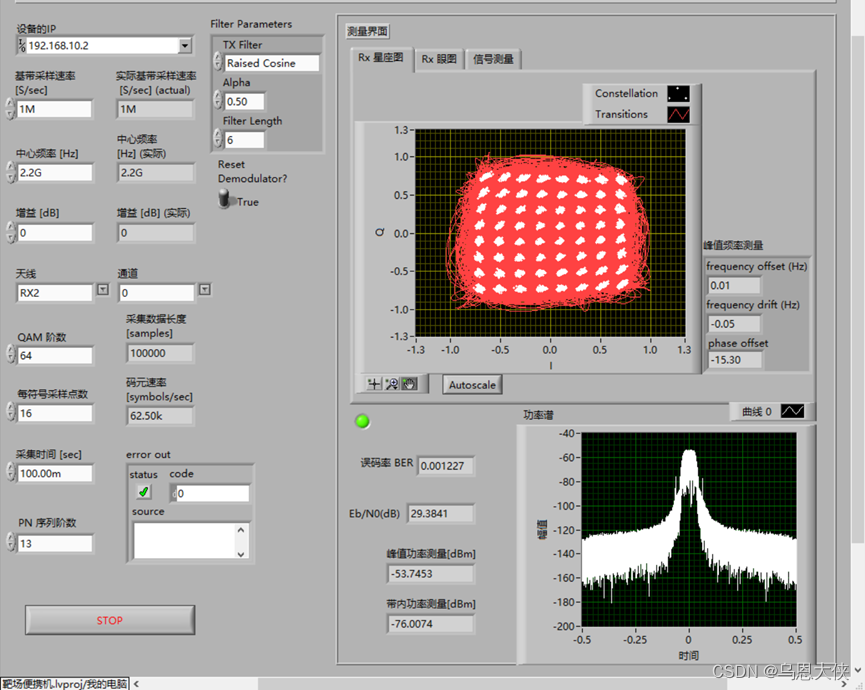

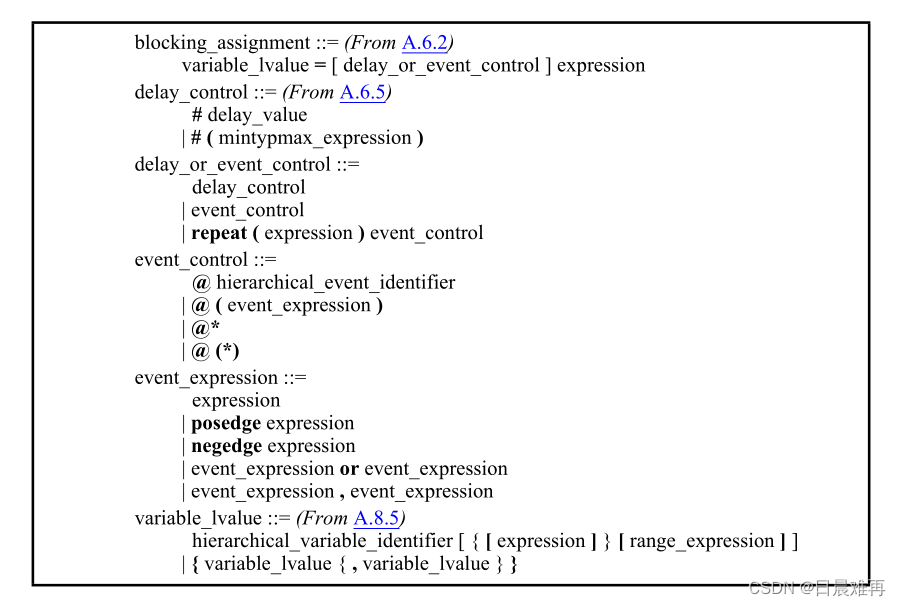

在本文,使用过程赋值的BNF定义作为例子讲解,如下图所示。

第一个范式首先将blocking_assignment定义为左边是variable_lvalue 中间是等号 = 而右边是可选的delay_or_event_control加上expression。

第二个范式定义了delay_control为#加上delay_value或者#加上小括号()包围的mintypmax_expression。

第三个范式定义了第一个范式中的delay_or_event_control,为delay_control或event_control或使用repeat语句的event_control。

第四个范式定义了第三个范式中的event_control,为@加上hierarchical_event_identifier或@加上小括号()包围的event_expression以及Verilog2001标准新增的@(*)或@*。

第五个范式定义了第四个范式中的event_expression,为expression,或posedge关键词加上表达式或negedge关键词加上表达式,或or连接的event_expression,或,连接的event_expression(递归定义自己)。

最后一个范式定义了variable_lvalue可以是hierarchical_variable_identifier加上可选的[]包围的多个数组表达式索引,以及可选的最后的[]包围的位选或域选表达式,variable_lvalue还可以是使用拼接运算符{}连接起来的多个variable_lvalue(递归定义自己)。

注意到,这里的定义中,有一些语法类别的定义并未给出,比如expression或range_expression,这些类别一般使用广泛,会在其他地方统一给出定义,可以自行查阅。

![[FlareOn6]Snake 题解](https://img-blog.csdnimg.cn/50509cf1936b4affa6a992d113a08eb3.png)