对于芯片验证,在验证寄存器环节,如果我们需要根据大量的寄存器来构建我们的sequence或者激励,比如irq测试,我们需要测试irq信号源到寄存器门口的连接是否正常,irq 寄存器各个field的接线排序是否有弄错,以及最基本读写功能等。如果能够借助脚本来统一产生我们的sequence或者激励必须能减轻我们的工作量并且能够统一化。

刚好python有个SystemRDL包就是用来对寄存器描述语言(rdl)进行各种处理,下面我们就来看看这个包都能做些什么,下一篇再介绍一些实际应用中的简单例子。

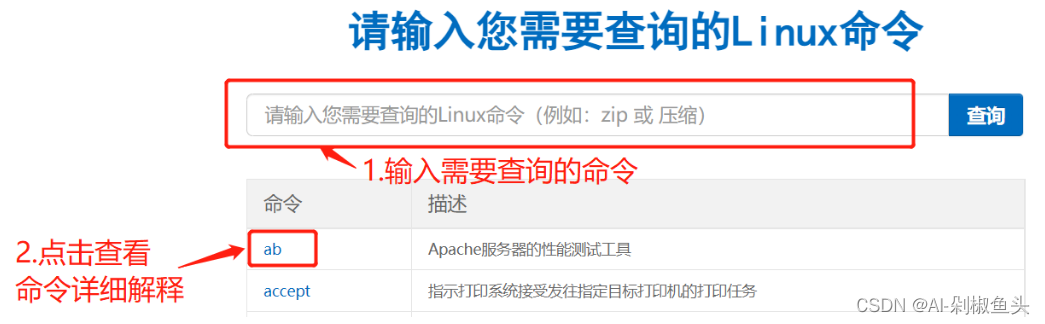

一.RDLCompiler(systemrdl.RDLCompiler)

systemrdl-compiler 模块为Accellera的SystemRDL 2.0寄存器描述语言实现了通用编译器前端。该项目的目标是提供一个免费和开放的编译器,降低使用行业标准寄存器描述语言的门槛。通过提供易于遍历和查询的复杂寄存器模型,编写自定义寄存器空间视图生成器应该容易得多

首先来看这样一段rdl描述:

reg my_reg_t {

field {} f1;

field {} f2;

};

addrmap top {

my_reg_t A[4];

my_reg_t B;

};经过compiler处理之后会变成下面这种树型结构:

每个树型结构上的一个节点都是一个component(systemrdl.component.Component,除root外,每个component都是另外一个component的子项(children)。

一些常用的函数:

compile_file(path: str, incl_search_paths: Optional[List[str]] = None, defines: Optional[Dict[str, str]] = None)→ FileInfo功能:解析并编译单个rdl文件,并将其附加到RDLCompiler的根命名空间。

参数含义:

path:rdl文件的路径

incl_search_paths:可选参数,相当于include,函数会在给的路径下搜索rdl文件

define:可选参数,RTL宏定义 ,是个字典,key是macro,value是macro text

elaborate(top_def_name: Optional[str] = None, inst_name: Optional[str] = None, parameters: Optional[Dict[str, RDLValue]] = None)→ RootNode功能:基于compile_file产生的树型结构info信息产生Node信息文件。

参数:

top_def_name (str):显式选择哪个addrmap作为top

inst_name (str) :top的例化名字

parameters (dict) :override top instance的字典

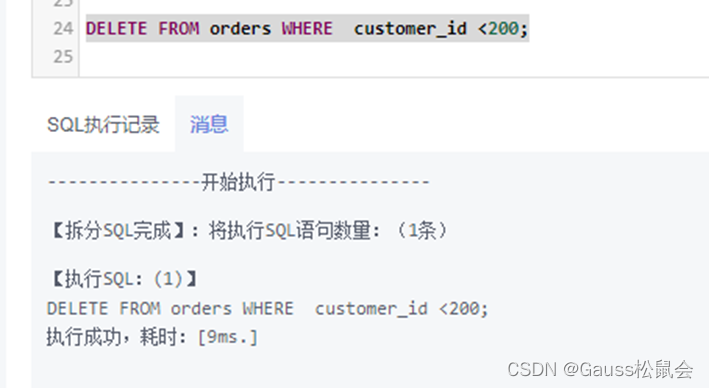

二. Node(systemrdl.node.Node)

"节点”叠加是一种附加的数据结构,用来简化查询和遍历寄存器模型。与寄存器模型的大部分交互都应通过 Node 对象进行,Node包含以下信息:

a. 当前component的实例

b. 当前component的实例的“母亲”

c.当前component的实例的索引idx(多次例化的情况)

上面的rdl对应的Node信息如下:

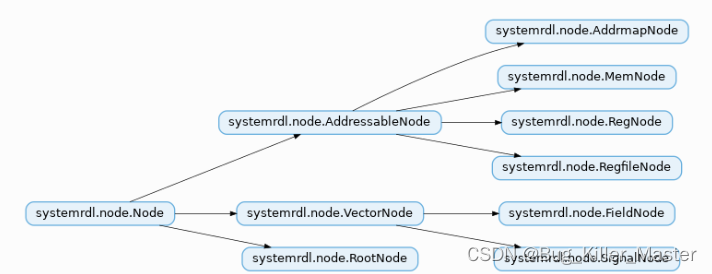

Node也是分层级的,不同层级之间是继承关系,用户可以使用自己感兴趣的层级的Node:

一些常用的重要的函数:

get_property(prop_name: str, **kwargs: Any)→ Any功能:或者component在rdl描述中的值

参数:

prop_name (str):property name

未完待续。。。