一、IC封装

在之前文章中有大致提过封装,这里展开讲讲

芯片生产流程_沧海一升的博客-CSDN博客每个半导体产品的制造都需要数百个工艺,泛林集团将整个制造过程分为八个步骤:晶圆加工-氧化-光刻-刻蚀-薄膜沉积-互连-测试-封装。_芯片生产流程https://blog.csdn.net/qq_21842097/article/details/119679132

1、概述

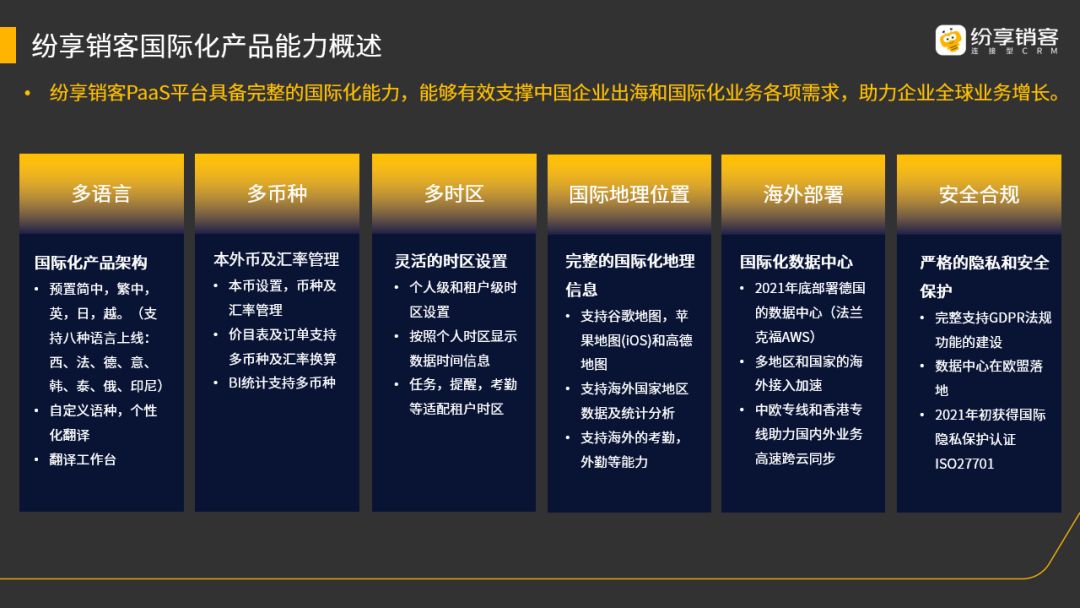

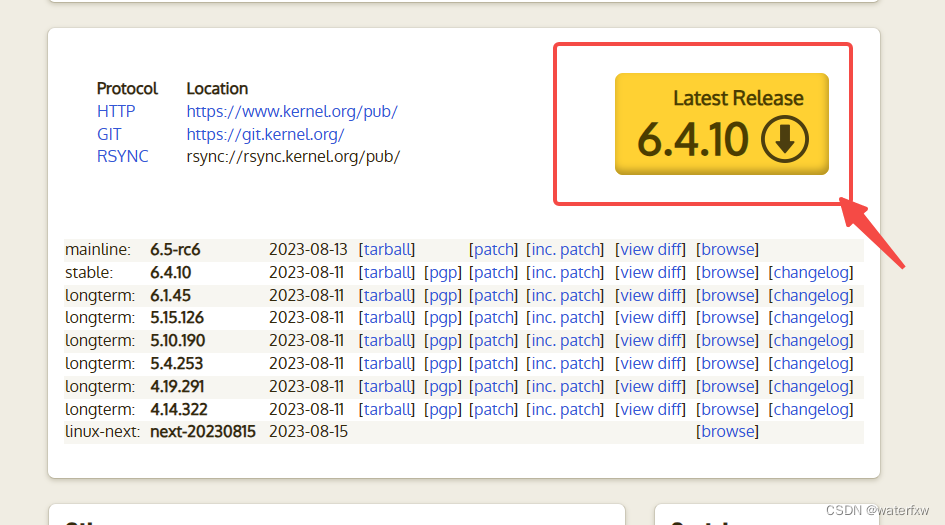

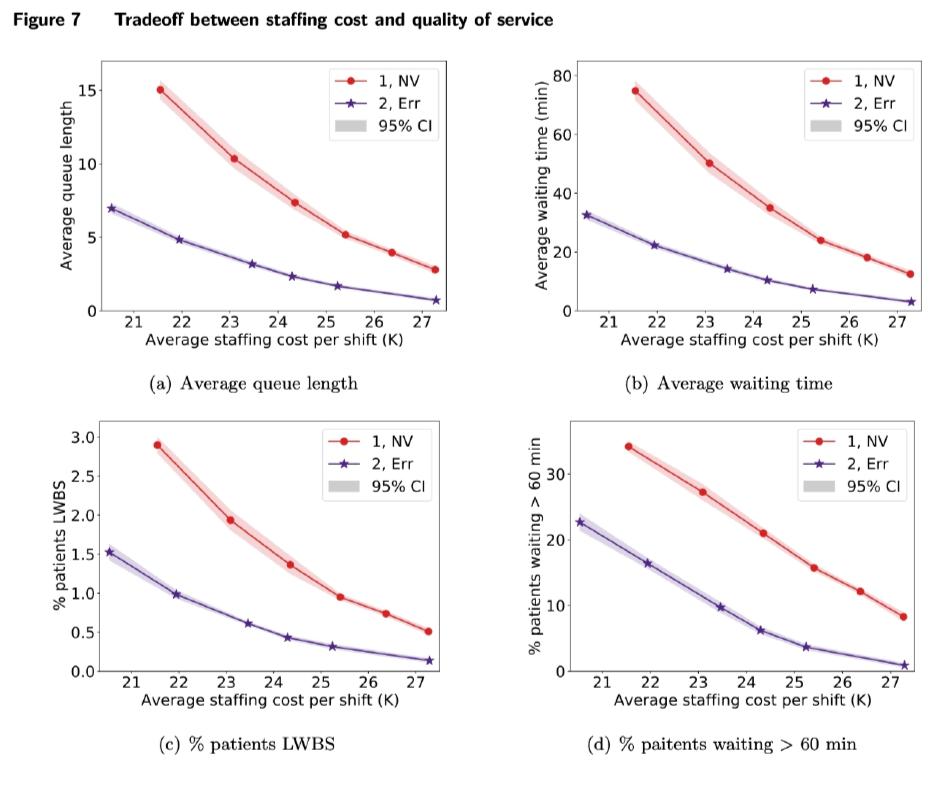

电子系统的集成主要分为三个层次:芯片上的集成,封装内的集成,PCB 板级集成,如下图所示集成的层次:

芯片上集成的基本单元是晶体管,我们称之为Function Cell,集成在一起形成了芯片。封装内集成的基本单元是上一步完成的裸芯片或者小芯片Chiplets,我们称之为功能单元Function Unit,这些在封装内集成形成了SiP。PCB 上集成的基本单元是上一步完成的封装或SiP,我们称之为MicroSystem,这些在PCB 上集成为尺度更大的系统。

封装(Package),就是把集成电路裸片(Die)放在一块基板或者框架上,然后把用来连接外部的管脚引出来,是引脚和裸片固定成为一个整体。IC 封装是对集成电路进行外部保护的方式,

保护内部电路正常功能。

IC 封装可以从不同角度进行分类,比如按封装材料分类:金属封装、陶瓷封装、塑料封装;

按与PCB 连接方式分类:插孔封装、表面贴装(框架类、基板类);按封装外形分类:TSSOP

(薄小外形)、QFP(四方引脚扁平式封装)、QFN(四方无引脚扁平封装)、BGA(球栅阵列封装)等;按封装实现工艺分类:倒装封装、晶圆级封装;按具体工艺技术分类:内插器(Interposer)技术、TSV 技术。

上图展示了传统封装流程,其中电气连接具体方式可以是引线键合、倒装、TSV 通孔连

接,电镀和切筋打弯是特指引脚式封装的流程,对于BGA 封装来说,这一步骤应是生长焊球。

2、封装技术迭代

封装技术也是随着集成电路步发展的 ,可以说每一代封装技术,都在克服集成电路中 I/O管脚数量的増加以及芯片尺寸的减少,这两种原因所产生的封装缺陷。从上世纪六七十年代开始,半导体界就开始关注封装技术的发展。每个时代以具体的封装形式为代表,芯片和PCB 连接方式逐步朝着先进方向发展。IC 封装可以分为如下几个阶段:通孔插装时代(如TO、DIP 封装),表面安装器件时代(如SOP、QFP 封装),面积阵列表面封装时代(如BGA、CSP 封装),高密度封装时代(如3D 堆叠、3D TSV),每个封装阶段也都有其特定的技术特点和优点。

每一个具体的封装形式都有其对应着的先进封装工艺技术以及拥有此技术的国际国内代表企业。主要先进封装技术有:BGA(球栅阵列式)、CSP(芯片尺寸封装)、FC(倒装芯片技术)、WLP(晶圆级封装)、SiP(系统级封装)。

3、封装的三种连接方式

(1)引线键合连接方式

早先的封装比较简单,主要起着芯片保护、尺度放大、电气互连的作用。其示意图大致

如下图。

引线键合,通过键合线将芯片的引脚连接到封装基板或者引线框架,然后再连接到外部引脚,通过引脚的排列方式,可分为BGA,CGA,QFP,LCC,SOP,DIP 等多种封装形式。

(2)芯片倒装连接方式

为了提高封装内的功能密度,需要在封装内集成更多的功能单元,传统的键合线连接方式已经无法满足要求,人们发明出多种多样的先进封装技术。在芯片表面布线,通过RDL

(Redistribution Layer) 重新布线层将PAD 连接到占位更宽松的位置并制作凸点Bump。然后通过Bump,芯片就可以直接安装在基板上了,如下图芯片倒装 ,这种工艺被称为倒装焊 Flip Chip。倒装焊工艺出现于上世纪60 年代,和键合线基本是同时代的产物。

(3)TSV 连接方式

倒装焊芯片由于无法堆叠,人们就发明出了能打穿整个芯片体的通孔技术,被称作TSV(Through Silicon Via)技术。下图TSV 互连,就是芯片上的TSV 示意图,通过TSV 可将芯片上下表面通过金属导体连接起来,为芯片堆叠做好了准备。

TSV 有许多工艺难点需要克服,最需要解决的是TSV 的位置选择和孔径缩小。因为TSV

需要穿过整个芯片体,位置选择不好就会损坏内部的电路连接和晶体管,所以位置选择很重

要。孔径的缩小也是为了尽可能少占芯片上的空间。

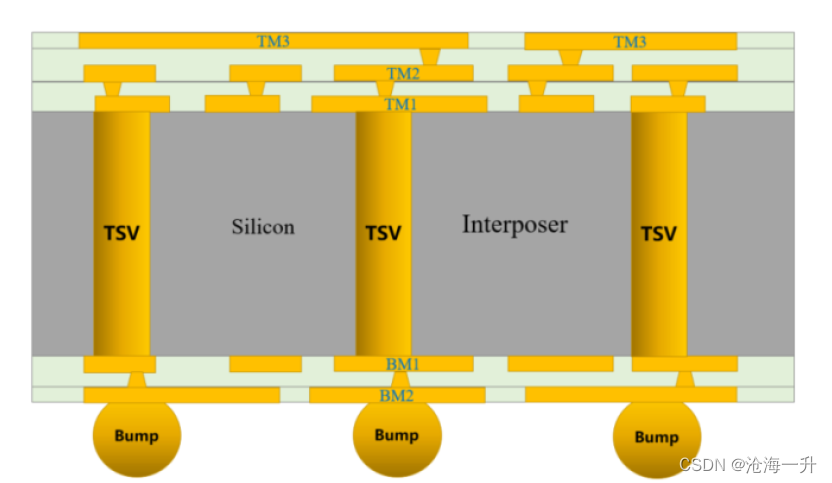

为了进一步提高集成度,人们又发明出了在硅基板Interposer 上制作出TSV,如下图硅基板TSV。

Interposer 被称为硅转接板,插入器,可以提供比普通基板更高的互连密度。上图所示为典型的硅转接板,上面3 层金属,下面2 层金属,中间通过硅通孔连接。Interposer上的TSV 通常比芯片上的TSV 尺寸大一些、密度小一些,制作难度也要低一些,制作好Interposer,就可以将芯片或者芯粒安装在硅转接板上了。

4、封装内的四种集成方式

传统的封装由于内部结构比较单一,都是用键合线将芯片引脚连接的引线框架或者基板,而外部引脚排布方式却多样化,因此人们谈论起封装,说的就是其外部的各种封装形式。而到了SiP 和先进封装时代,这种情况发生了巨大的改变,SiP 和先进封装其外部封装形式逐渐统一到引脚排布更多、互连密度更大的BGA,CGA 等封装形式,而封装内部由于有了集成的功能,其结构变得越来越复杂,人们对封装的关注逐渐由外部的封装形式转变为内部的封装结构。

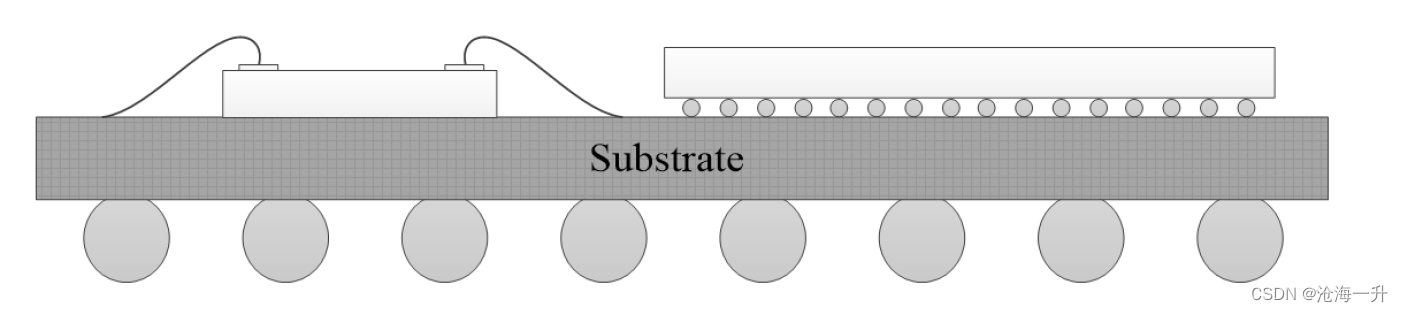

(1)2D 集成

2D 集成是指在基板的表面水平安装所有芯片和无源器件的集成方式。基板上表面所处的平面为XY 平面,所有芯片和无源器件均安装在基板平面,芯片和无源器件和 XY 平面直接接触,基板上的布线和过孔均位于 XY 平面下方,如下2D 集成示意图。

常见的2D 集成技术应用于MCM、部分SiP 以及PCB。2D 集成的SiP,其工艺路线和MCM 非常相似,和MCM 主要的区别在于2D 集成的SiP 规模比MCM 大,并且能够形成独立的系统。

(2)2D+集成

2D+集成是指的传统的通过键合线连接的芯片堆叠集成。所有芯片和无源器件均地位于

XY 平面上方,部分芯片不直接接触基板,基板上的布线和过孔均位于XY 平面下方,如下 2D+集成示意图。

(3)2.5D 集成

2.5D 顾名思义是介于2D 和3D 之间,通常是指既有2D 的特点,又有部分3D 的特点的一种维度,现实中并不存在2.5D 这种维度。所有芯片和无源器件均XY 平面上方,至少有部分芯片和无源器件安装在中介层上(Interposer),在XY 平面的上方有中介层的布线和过孔,在XY 平面的下方有基板的布线和过孔。

2.5D 集成的关键在于中介层Interposer,一般会有几种情况,1)中介层是否采用硅转接板,2)中介层是否采用TSV,3)采用其他类型的材质的转接板;在硅转接板上,我们将穿越中介层的过孔称之为TSV,对于玻璃转接板,我们称之为TGV。

硅中介层有TSV 的集成是最常见的一种2.5D 集成技术,如上图有TSV 的2.5D 集成示意图,芯片通常通过MicroBump 和中介层相连接,作为中介层的硅基板采用Bump 和基板相连,硅基板表面通过RDL 布线,TSV 作为硅基板上下表面电气连接的通道,这种2.5D 集成适合芯片规模比较大,引脚密度高的情况,芯片一般以FlipChip 形式安装在硅基板上。

硅中介层无TSV 的2.5D 集成的结构一般如上图所示,有一颗面积较大的裸芯片直接安装在基板上,该芯片和基板的连接可以采用Bond Wire 或者Flip Chip 两种方式,大芯片上方由于面积较大,可以安装多个较小的裸芯片,但小芯片无法直接连接到基板,所以需要插入一块中介层(Interposer),在中介层上方安装多个裸芯片,中介层上有RDL 布线,可将芯片的信号引出到中介层的边沿,然后通过Bond Wire 连接到基板。这类中介层通常不需要TSV,只需要通过Interposer 上表面的布线进行电气互连,Interposer 采用Bond Wire 和封装基板连接 。

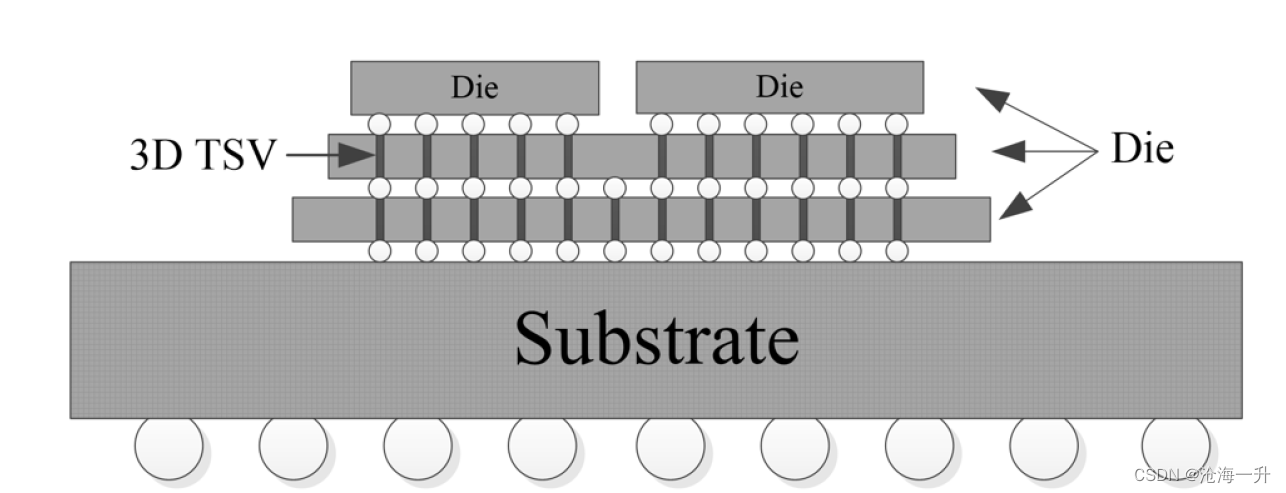

(4)3D 集成

3D 集成和2.5D 集成的主要区别在于:2.5D 集成是在中介层Interposer 上进行布线和打孔,而3D 集成是直接在芯片上打孔(TSV)和布线(RDL),电气连接上下层芯片。所有芯片和无源器件均位于XY 平面上方,芯片堆叠在一起,在XY 平面的上方有穿过芯片的TSV,在XY 平面的下方有基板的布线和过孔。

3D 集成大多数应用在同类芯片堆叠中,如下图,多个相同的芯片垂直堆叠在一起,通过穿过芯片堆叠的TSV 互连。同类芯片集成大多应用在存储器集成中,例如DRAM Stack,FLASH Stack 等。

不同类芯片的3D 集成中,如下图,一般是将两种不同的芯片垂直堆叠,并通过TSV电气连接在一起,并和下方的基板互连,有时候需要在芯片表面制作RDL 来连接上下层的TSV。

二、TSV的工艺技术

目前3D 集成技术主要有三种:引线键合、芯片倒装、TSV(硅通孔)技术。这些技术之间的差异在于互连线的连接方式不同,由于互连越来越显著的重要性,一个基板上需要集成更多的功能,键合能够实现这一想法,但键合互连线较长,对信号传输有很大的影响,这让芯片间的垂直互连成为一个高度关注的研究方向。

这里3D IC 是指在垂直方向将多个裸芯片堆叠起来,用TSV 实现电连接,相比2D IC 它具有如下几个优势:(a)极大地减小了互连线的长度。(b)有效地提高了互连密度。(c)可实现异质集成。对于不同功能的芯片如:传感器、射频芯片、存储器、处理器等,采用了不同的工艺制程技术和衬底材料,3D IC 可将这些芯片集成在一个系统。

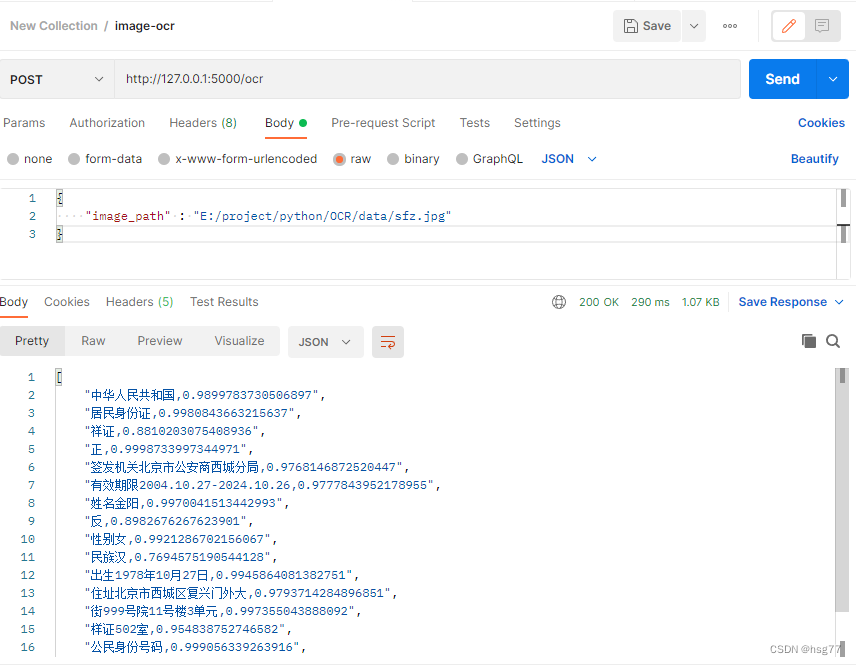

目前来说,3D IC 朝着小体积、高集成度、高数据带宽、多功能的方向发展,最终的目标是实现高度集成的异质3D IC,如图1三维集成电路示意图,由图可知,芯片的存储器、处理器等逻辑器

件分布在整个三维空间。TSV 技术是实现3D IC 的关键技术,3D IC 的设计就是TSV 的设计。

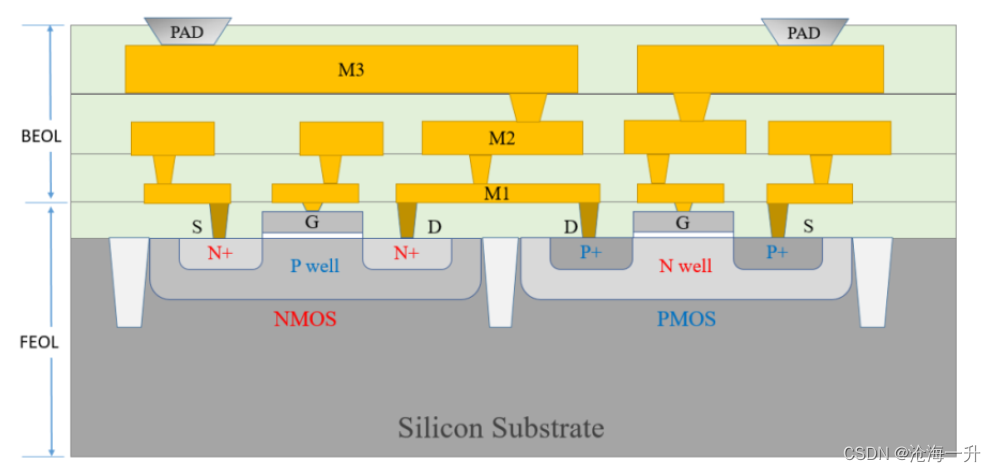

1、制造技术

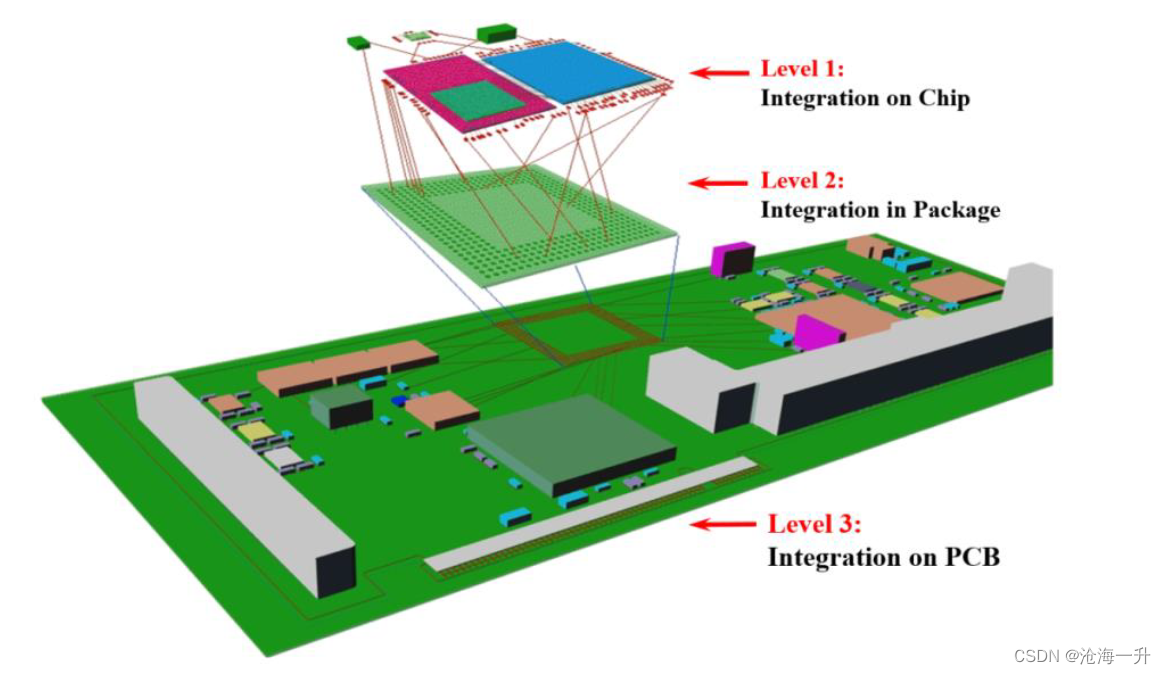

芯片上的集成主要分为两大环节:器件制造和金属互连,也称为前段工艺FEOL 和后段工艺BEOL。器件制造就是在单晶硅片上制造出被我们称为功能细胞的晶体管、电阻、电容、二极管等。晶体管的制造过程,主要包括隔离、栅结构、源漏、接触孔等形成工艺,一般称之为前段工艺(FEOL, Front End of Line)。晶体管层制造好后,通过铜等金属制造接触孔连接晶体管和首层布线,然后通过多层金属布线和过孔进行电气互连,之后引出焊盘形成,一般称为后段工艺(BEOL, Back End of Line)。

上图给出了前段工艺FEOL 和后段工艺BEOL 的结构示意图,先在硅基底上制造晶体管,然后通过金属互连将它们连接起来并引出到芯片的PAD。了解前段、后段工艺之后,可以更好的理解TSV 的制造工艺流程。

TSV的制造根据工艺顺序的不同 ,可分为先通孔技术、中和后通孔技术 。

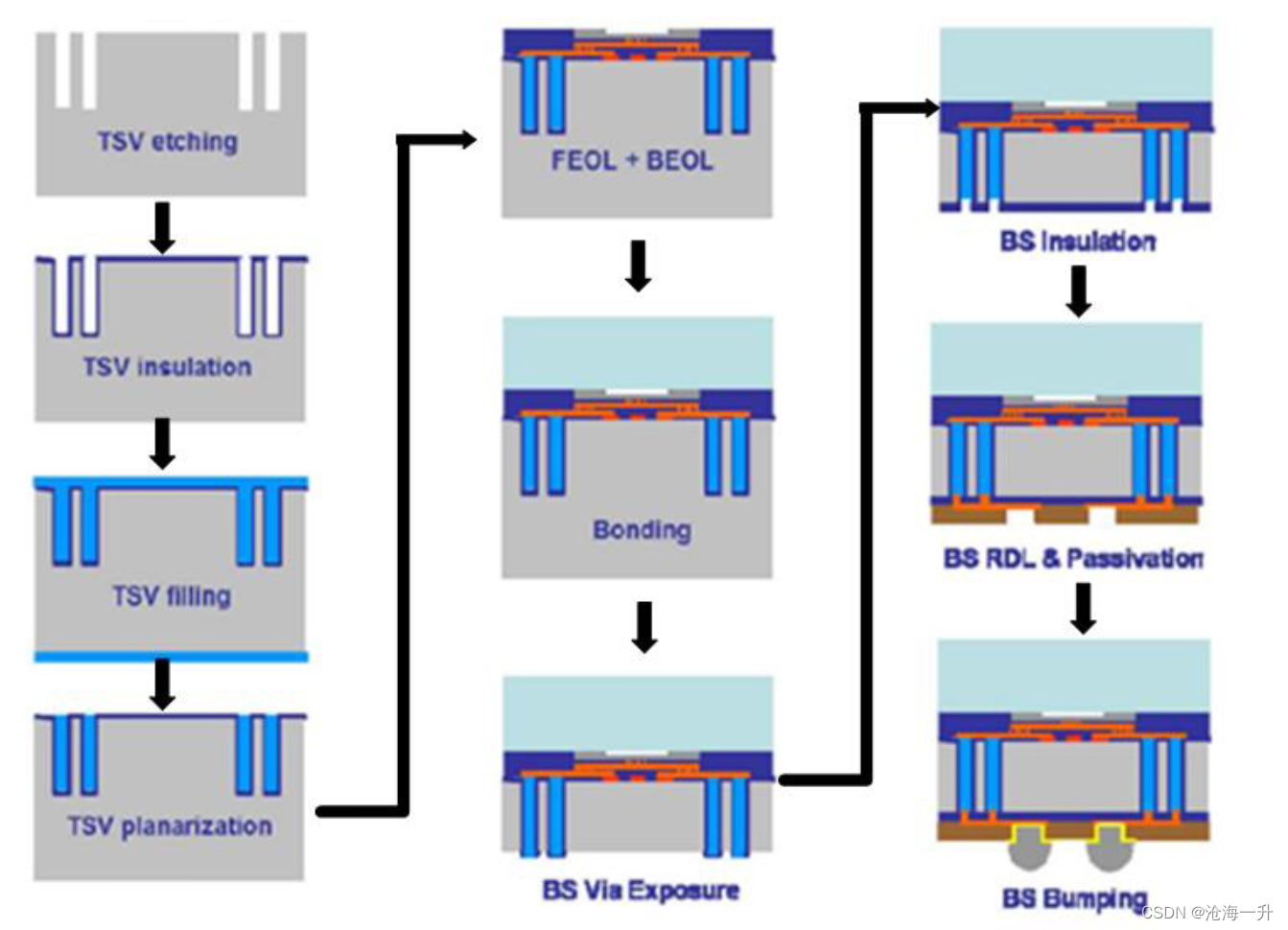

(1)Via First

先通孔技术是指在制做CMOS 器件之前,在空白硅片上制作出通孔。

在完成 TSV的制造后, FEOL中通常需要进行退处理等高温流程 ,这些流程的工艺温度可达 一千摄氏度以上,势必会对 TSV造成影响这也就对 TSV的导电材料提出了很高的要求,耐高温的多晶硅材料是更好的选择,但 多晶硅的电导率小于铜之类常用金属材料,因此的寄生电阻会比较大,也降低了对其他材质敏感性 ,这些都是研究三维集成电 路的性能时需要考虑的因素。

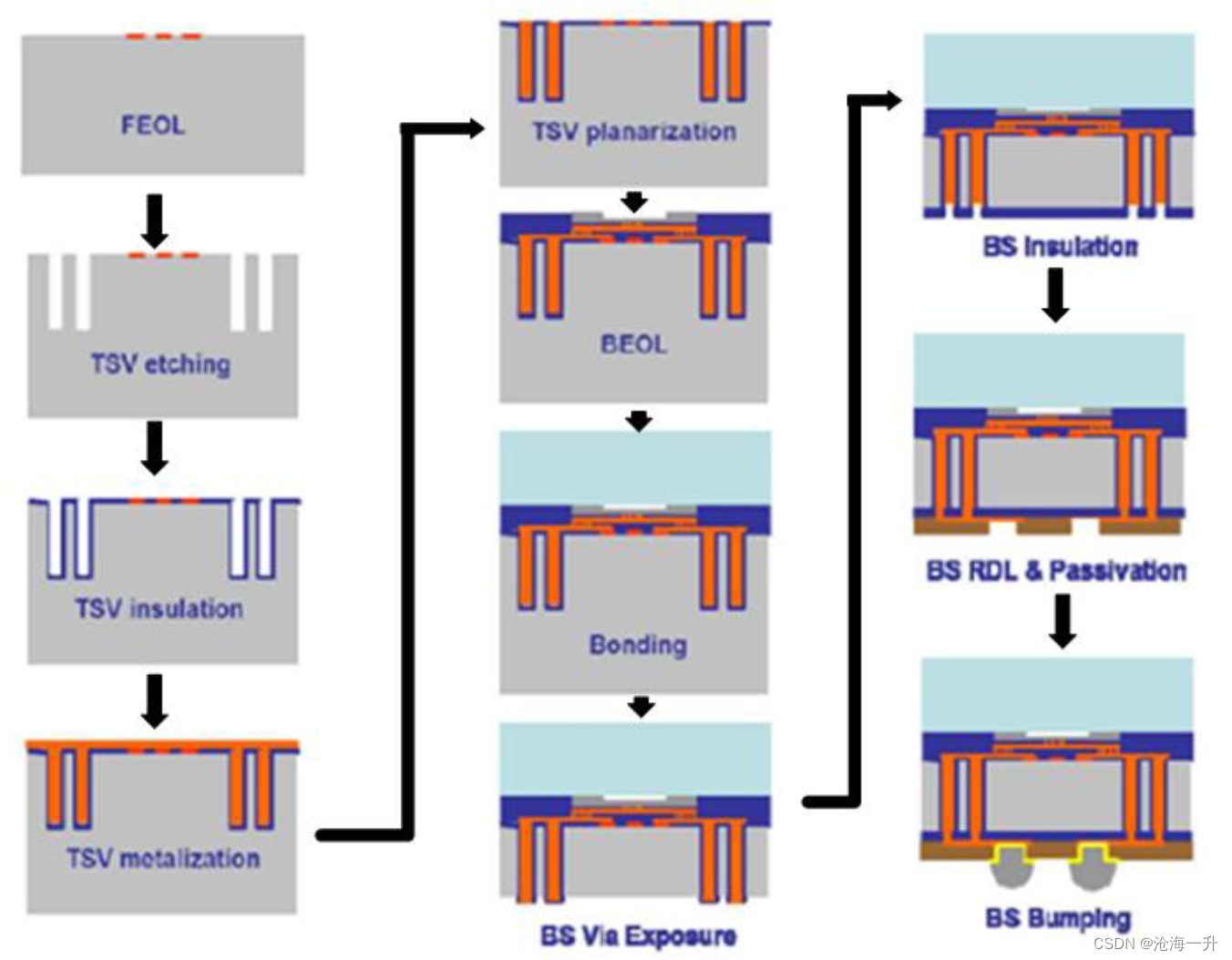

(2)Via Middle

中通孔技术在FEOL和 BEOL中间完成了 SV的刻蚀与制造过程 ,当完成所有的器件制作后, 在空白硅片处利用 DRIE技术 钻出 TSV通孔,然后通过电镀工艺将完成TSV金属导体的制造。

中通孔工艺技术不需要面对FEOL的热量冲击 ,BEOL中温度最高只 工序中温度最高只有400摄氏度, 这就使材料钨能够用作金属填充料 ,和多晶硅TSV相比,寄生电阻降低了很多;同时金属钨在热稳定性上更具优势。但是中通孔技术的TSV有着较高的深宽比,从而 导致较高的寄生阻抗以及增加工艺难度 。

(3)Via Last

后通孔技术是在BEOL或者芯片减薄键合完毕后进行 TSV的制作,相比先通孔和中通孔技术,后通技术的 TSV需穿过金属互连线层, 从而造成了金属布线 空间局促的现象 。

根据制造TSV工艺是在键合前还是后, 还可以将将工艺过程进一步分为正面制造( Front Side)和背面制造( Back Side)两种方式。由于TSV制造 不需要承受 FEOL 与 BEOL的高温,所以可以使用金属铜作为硅通孔的导体材料,其有着低电阻率的优势,但使用金属铜会使得 TSV制造过程对温度与污染要求都更加严格 。尽管后通孔技术降低 了三维传输结构的寄生电阻,但因为其极高的深宽比,使得 相比前通孔 与中通孔技术,其寄生电 感效应依然很突出 。

2、TSV制造的键合方式

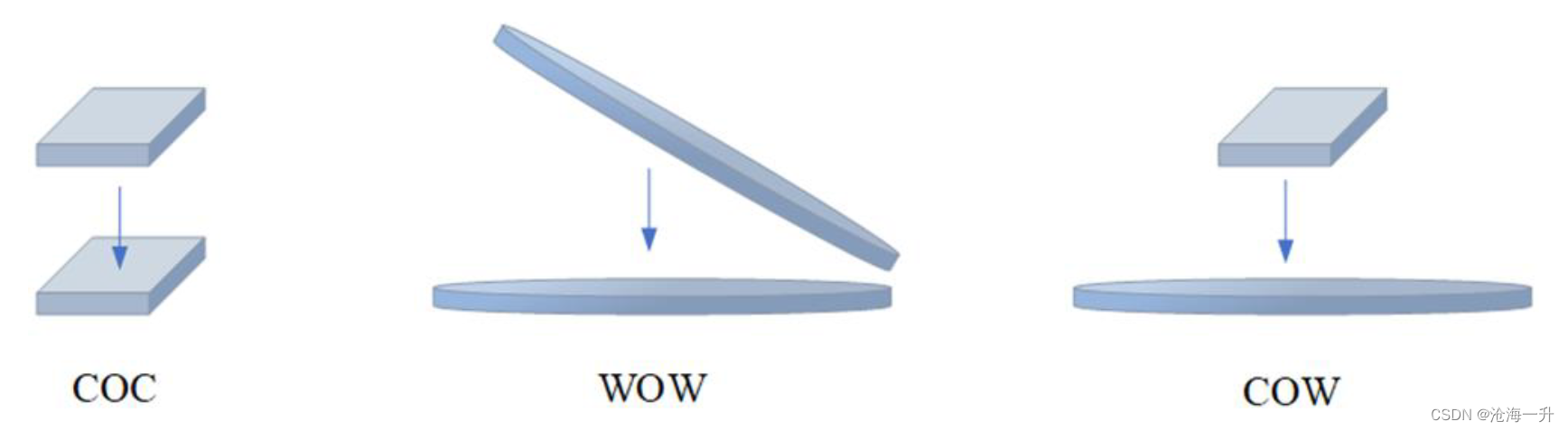

为了适应各种器件的封装需求 ,三维集成电路设计拥有很多种键合方法 ,为三维集成电路提供了灵活多样的工艺方案, 扩展了三维集成的 应用领域。 其中 基于 TSV 的三维集成 键合方式 有三种分类,如图所示

所示,分别为 芯片与芯片的芯片级键合( Chip On Chip, COC)、晶圆片与晶圆片的晶圆 级键合( Wafer On Wafer,WOW)以及芯片与晶圆的键合 (Chip On Wafer,COW)。 这三 类键合方式的优缺点各有不同 ,因此需要根据具体求选择合适的键合方式 。

(1)WOW

晶圆级键合的优点是键合工艺简单,且工艺的生产效率很高,同时工艺过程中的热冲击过程也很少,整个晶圆上大量的芯片直接键合,只需通过一次对准键合就能够完成,但这就要求参与键合的两层晶圆的材料以及热膨胀系数能够良好的匹配,并且晶圆上的芯片大小是相同或者近的。 但因为不能在键合前将晶圆上的失效芯片预先剔除掉而直接选择确好芯片 (Know Good Die,KGD),所以不能保证最终的良品率。这是由于每层晶圆片上的芯成品率不同,确好芯片 的位置也不相同, 这使得某一层晶圆上的确好芯片和另一 晶圆片上对应位置的不良芯片键合的概率变大,这会导致对应垂直方向上所有芯片失效 ,造成大量的成本浪 费。因此, 晶圆级键合适用于 级键合适用于成熟工艺节点的高良率晶圆之间键合。

另一方面,如果键合的两个晶圆片面积不同,会造成浪费因而 WOW键合适用于具有相同衬底材料与同功能芯片的晶圆堆叠的封装 (如 HBM),对于不同功能的晶圆片(如 传感器、 射频器件、 MEMS、及非硅衬底等)该键合方式 并不是最佳的选择 。

(2)COC

芯片级键合的工艺顺序是首先将晶圆片切割成独的芯片,这就能够在键合前 对这些芯 对这些芯片进行测试筛选,并挑选出确好芯片进行有效键合。这种键合方法可以把不良晶片提前淘汰掉,极大增加了产出封装体的良品率,同时能够有效地克服不同尺寸的芯片之间键合所带来的面积失配问题,进而减少三维集成电路的整体造价。不过这种键合方法的最大弊端则在于必须逐个对准,所需对准时间长生产效率低下,对准精度也较低,导致产量较低 。

(3)COW

芯片与晶圆的键合是通过先 将成品率低或者面积较小的 将成品率低或者面积较小的 将成品率低或者面积较小的晶圆片进行切割,对切割出来的芯片进行测试筛选,挑出确好芯片与另一块 晶圆片上的芯片键合。 因此该键合方式相对芯片级键合方式有更高的生产效率。然而,最先键合 的芯片与晶圆要经受后续工艺中的高温冲击,这就要求芯片与晶圆具有良好热稳定性。因此这种经过预先测试后再键合的方法具有较高的良率,也能够实现不同功能或者衬底材料的芯片之间的三维集成。

![[软件工具]精灵标注助手目标检测数据集格式转VOC或者yolo](https://i1.hdslb.com/bfs/archive/785e751fd7911126cf12e5929d1ec80a0b2f8f0c.jpg@100w_100h_1c.png@57w_57h_1c.png)