提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

Xilinx DDR3学习总结——3、MIG exmaple例程仿真

- 前言

- 仿真

前言

前面我们直接把exmaple例程稍加修改就进行了抢先上板测试,证明了MIG模块工作时正常的,但后续如果需要添加读写功能的话,还是需要先进行仿真,因此我们还是先要把modelsim仿真弄起来

仿真

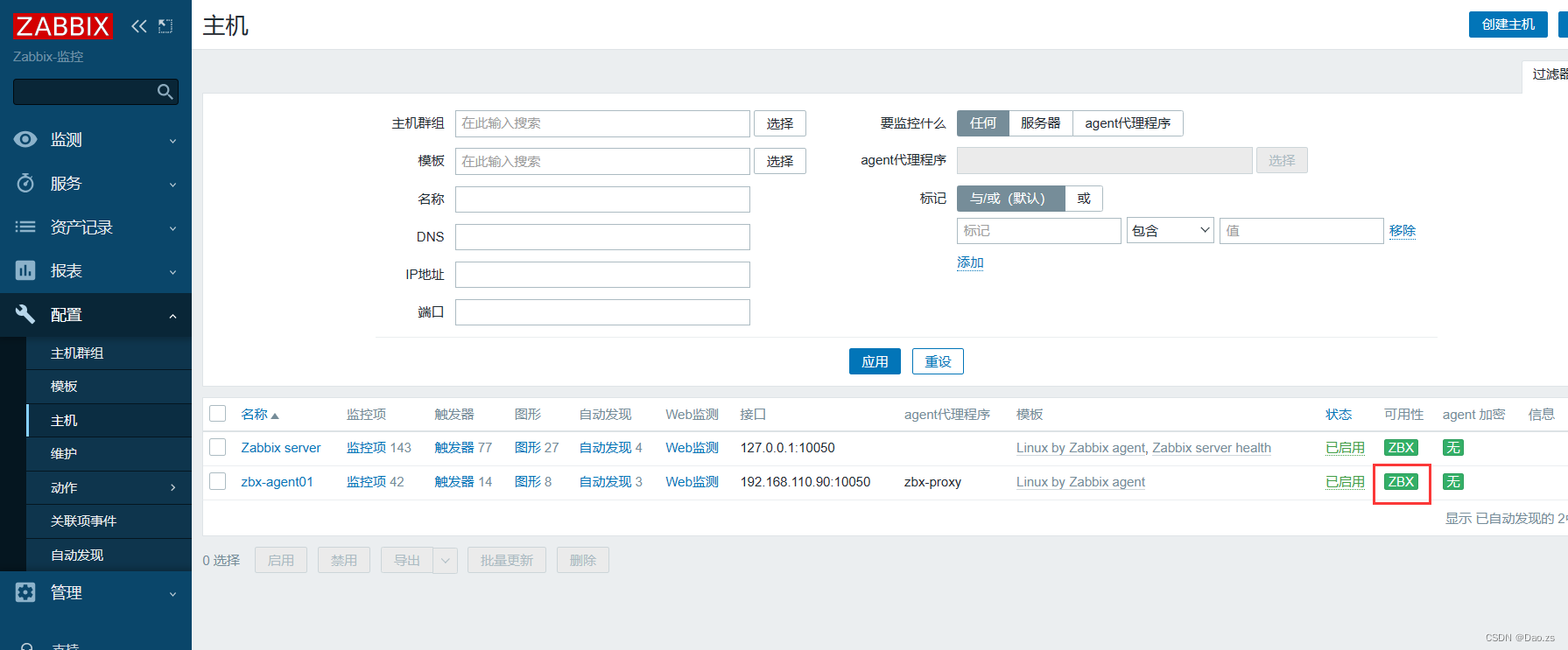

在生成example的时候,vivado就自带仿真激励的是直接可以仿真的,

sim_tb_top.v就是仿真tb文件

ddr3_model.sv

ddr3_model_parameters.vh

这两个文件是DDR3的模型,根据我们MIG的设置生成的,因此我们也需要引用

最后,还有一个sim.do文件,这个文件的内容用于自己do文件的编写的参考,我们依葫芦画瓢,最后形成自己的do文件

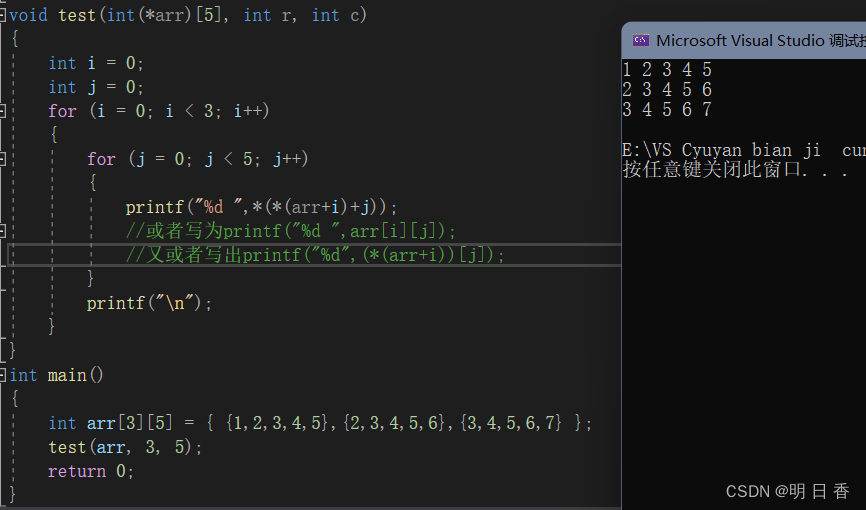

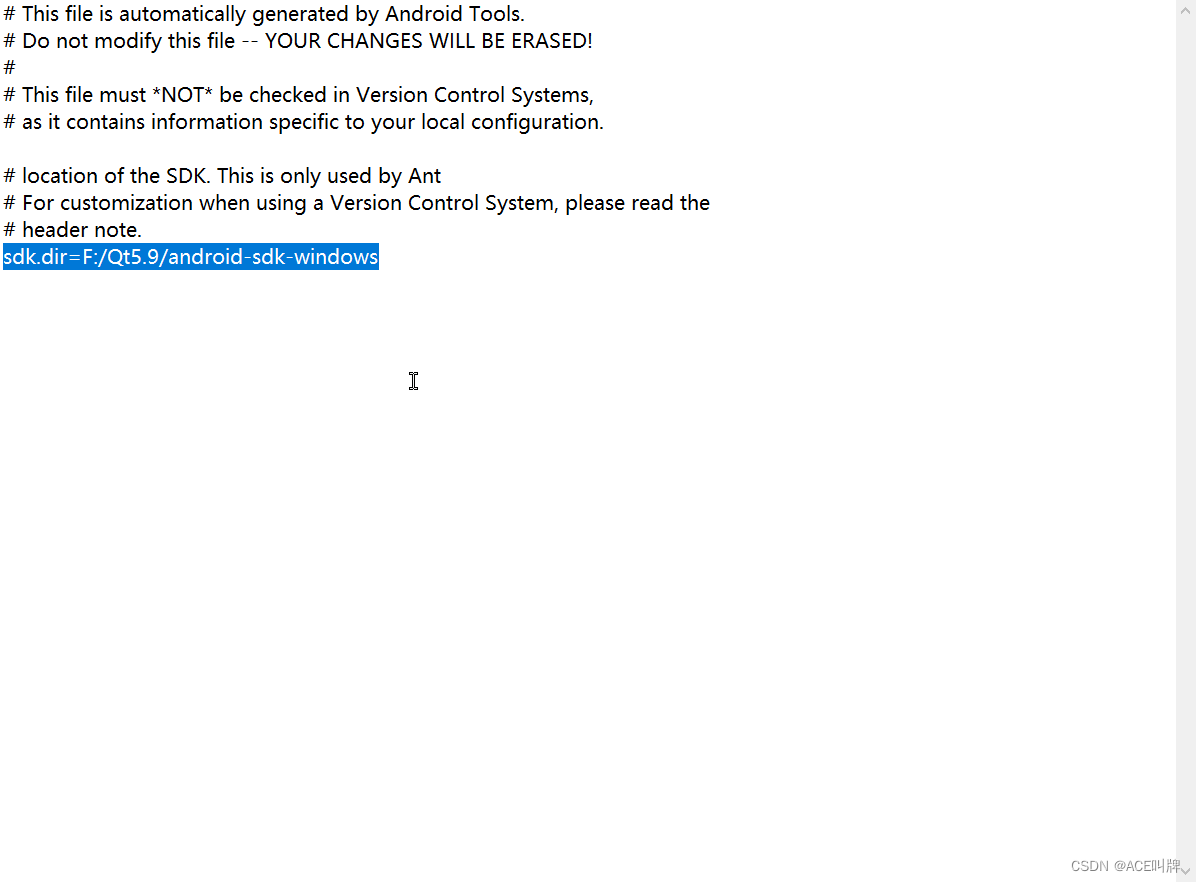

quit -sim

set RTL_PATH .

cd $RTL_PATH

vlib work

vmap work work

vlog -work work $RTL_PATH/imports/mig_7series*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/clk_wiz_0/clk_wiz_0_sim_netlist.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/mig_7series_0.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/mig_7series_0_mig_sim.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/clocking/*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/controller/*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/ecc/*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/ip_top/*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/phy/*.v

vlog -work work $RTL_PATH/mig_7series_0_ex.srcs/sources_1/ip/mig_7series_0/mig_7series_0/user_design/rtl/ui/*.v

vlog -work work $RTL_PATH/imports/example_top.v

vlog -work work $RTL_PATH/imports/wiredly.v

vlog -work work $RTL_PATH/imports/sim_tb_top.v

#Pass the parameters for memory model parameter file#

vlog -work work -sv +define+x4Gb +define+sg107E +define+x16 $RTL_PATH/imports/ddr3_model.sv

vlog -work work D:/Xilinx/Vivado/2020.2/data/verilog/src/glbl.v

vsim -L secureip -L simprims_ver -L unifast -L unifast_ver -L unimacro -L unimacro_ver -L unisim -L unisims_ver -L xpm -voptargs="+acc" sim_tb_top glbl

add wave sim:/sim_tb_top/*

log -r *

run 1209us

do wave.do

注意,因为example_top的sys_rst端口被我删掉了,以及sys_clk_i的输入变成了100M,这两点需要在sim_tb_top.v进行修改。

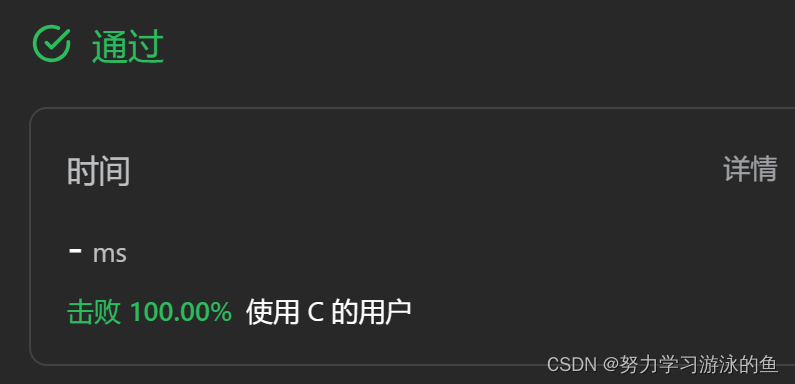

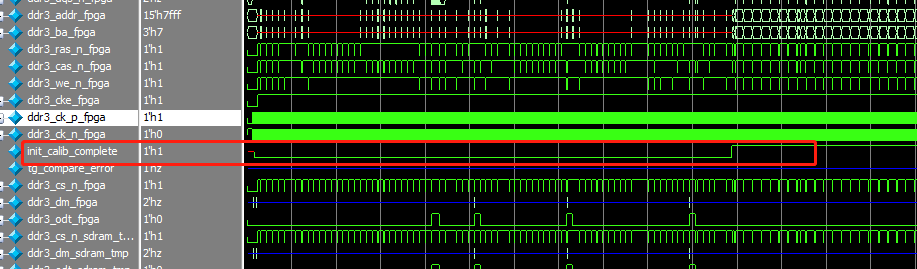

修改完成之后。进行modelsim仿真:

不一会儿 ,DDR3初始化成功的标志就拉高了,说明modelsim仿真成功