萌新的STM32学习-4

STM32系统框架

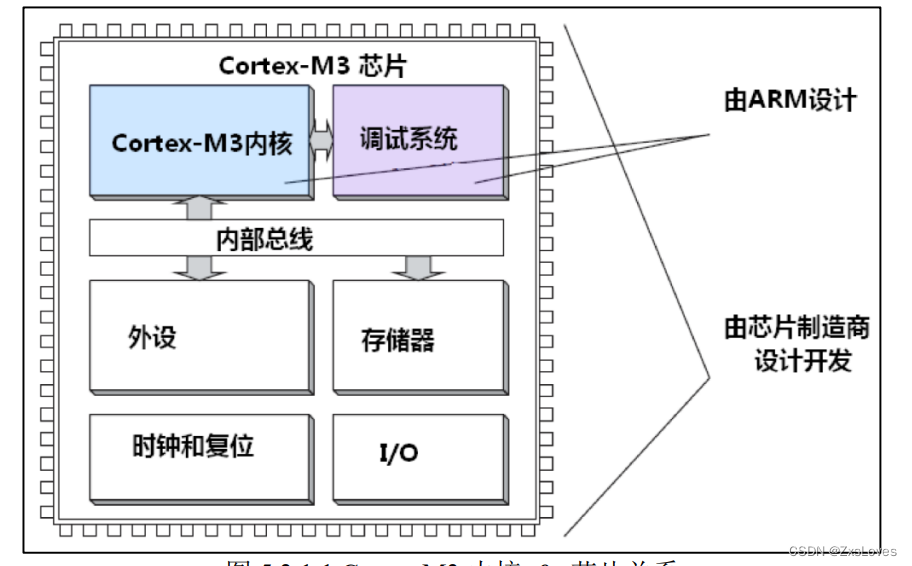

1.1 Cortex M 内核& 芯片

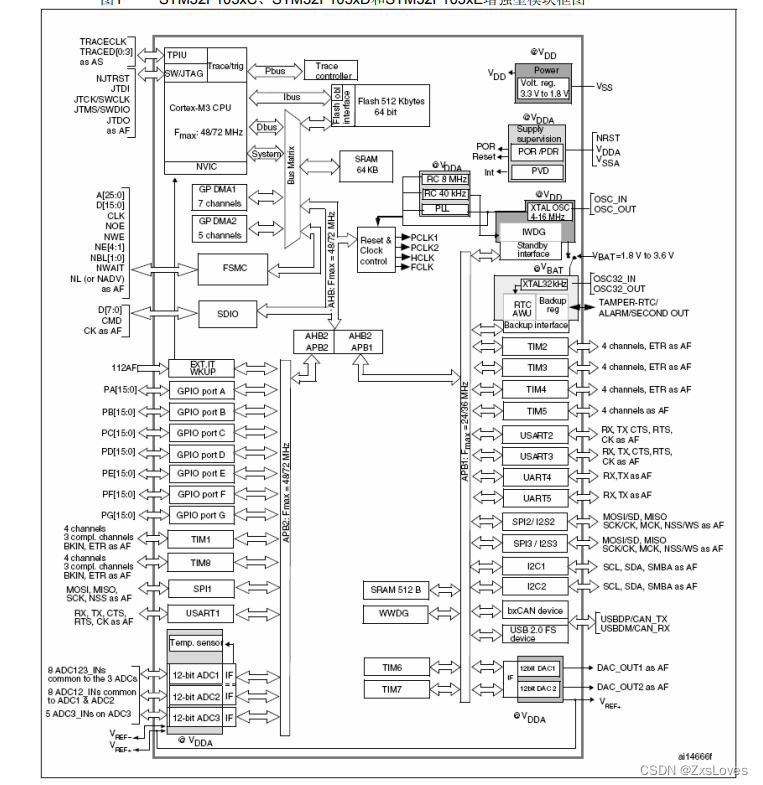

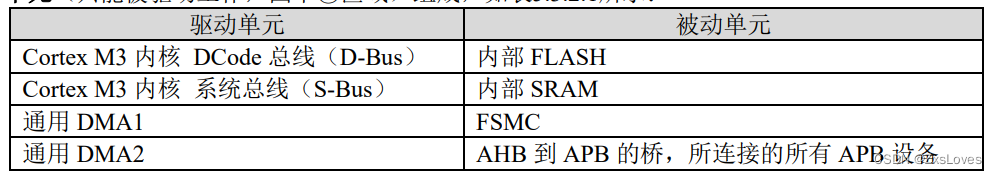

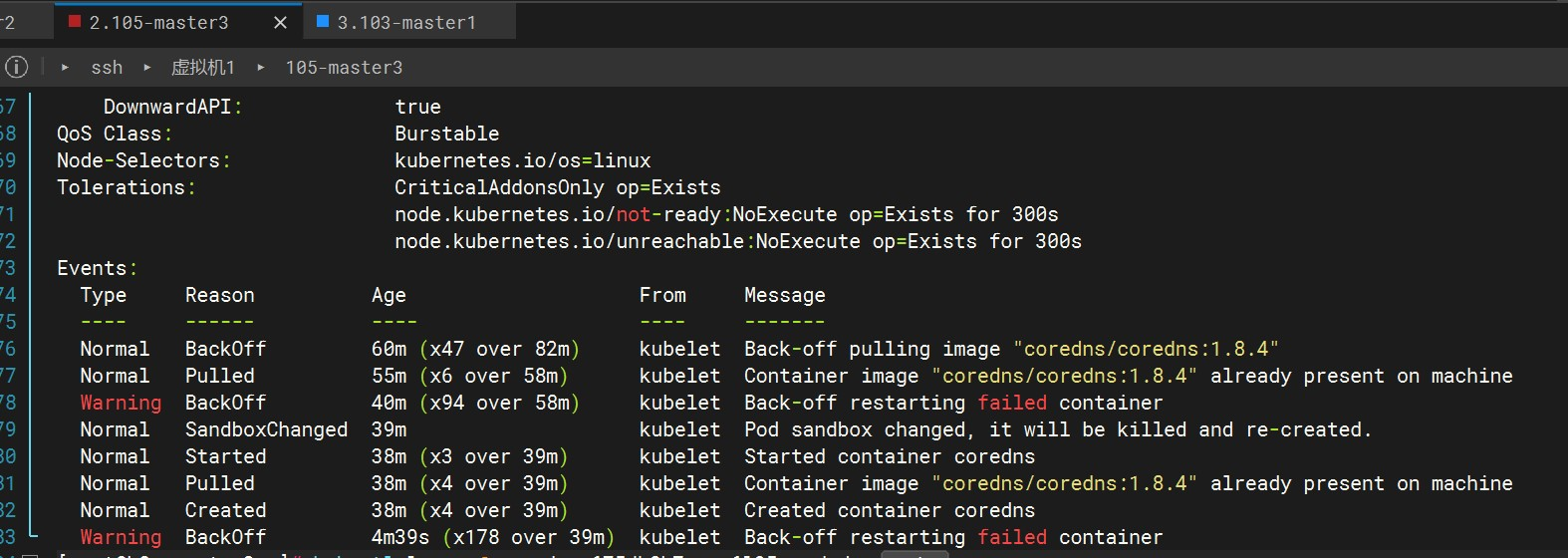

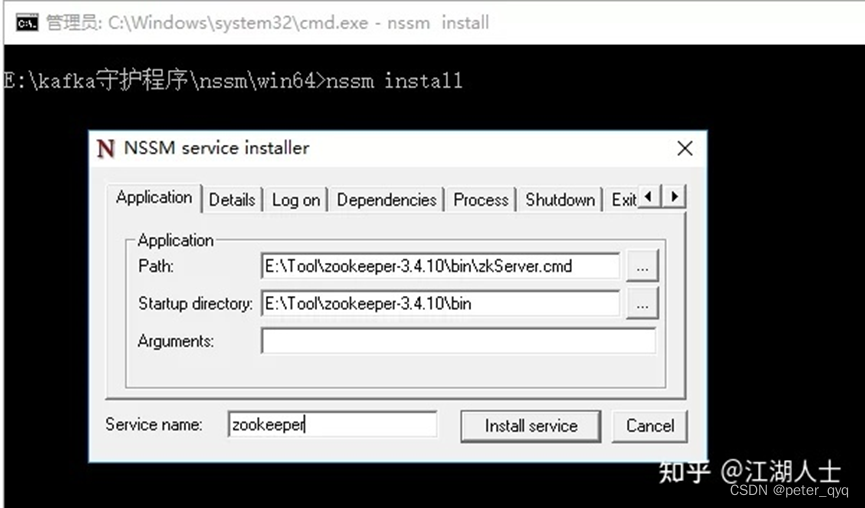

F1有四个驱动单元 四个被动单元

AHB 高级高性能总线

APB 高级外围总线

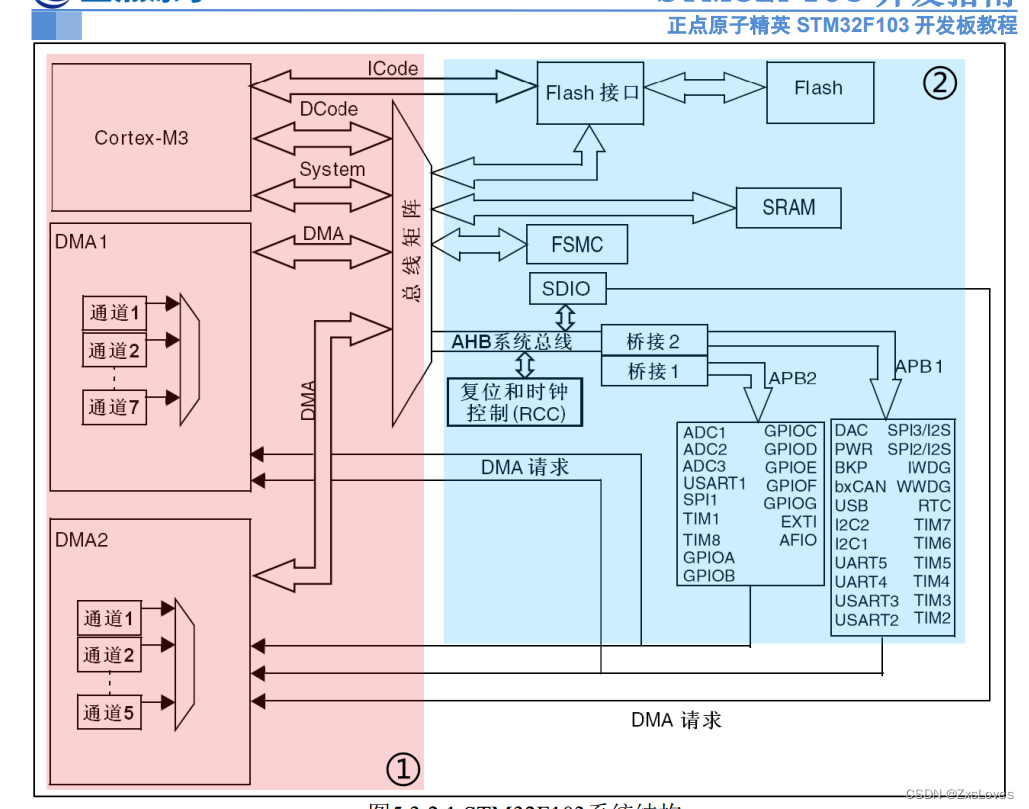

部分系统结构

最上面的ICode 总线直接连接到了内部Flash 不需要通过总线矩阵

. D Code 总线(D - Bus)

这是Cortex M3内核的数据总线,连接闪存存储器数据接口(如:SRAM、FLASH等),用

于各种数据访问,如常量、变量等。

3. 系统总线(S - Bus)

这是Cortex M3内核的系统总线,连接所有外设(如:GPIO、SPI、IIC、TIM等),用于控

制各种外设工作,如配置各种外设相关寄存器等。

4. DMA 总线

DMA是直接存储访问控制器,可以实现数据的自动搬运,整个过程不需要CPU处理。如可

以实现DMA传输内存数据到DAC,输出任意波形,传输过程不需要CPU参与,可以大大节省CPU

支,从而更高效的处理事务。STM32F103ZET6内部有2个DMA控制器,可以实现内存到外设、

外设到内存、内存到内存的数据传输。

5. 内部 FLASH

内部FLASH即单片机的硬盘,用于代码/数据存储,CPU通过ICode总线经FLASH接口访问

内部FLASH,FLASH最高访问速度是24Mhz,因此以72M速度访问时,需要插入2个时钟周期延

迟。

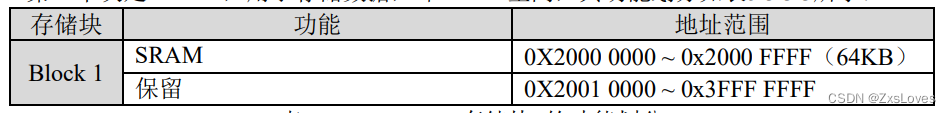

6. 内部 SRAM

内部SRAM即单片机的内存,用于数据存储,直接挂载在总线矩阵上面,CPU通过DCode总

线实现0等待延时访问SRAM,最快总线频率可达72Mhz,从而保证高效高速的访问内存。

7. FSMC

FSMC即灵活的静态存储控制器,实际上就是一个外部总线接口,可以用来访问外部SRAM、

NAND/NOR FLASH、LCD等。它也是直接挂在总线矩阵上面的,以方便CPU快速访问外挂器件。

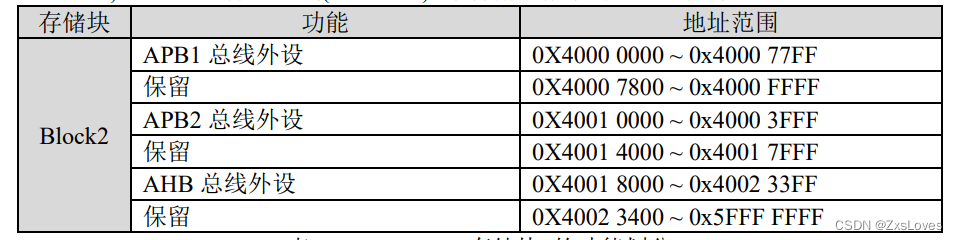

8. AHB/APB 桥

AHB总线连接总线矩阵,同时通过2个APB桥连接APB1和APB2,AHB总线速度最大为

72Mhz,APB2总线速度最大也是72Mhz,但是APB1总线速度最大只能是36Mhz。这三个总线上

面挂载了STM32内部绝大部分外设。

9. 总线矩阵

总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法,保证各

个总线之间的有序访问,从而确保工作正常。

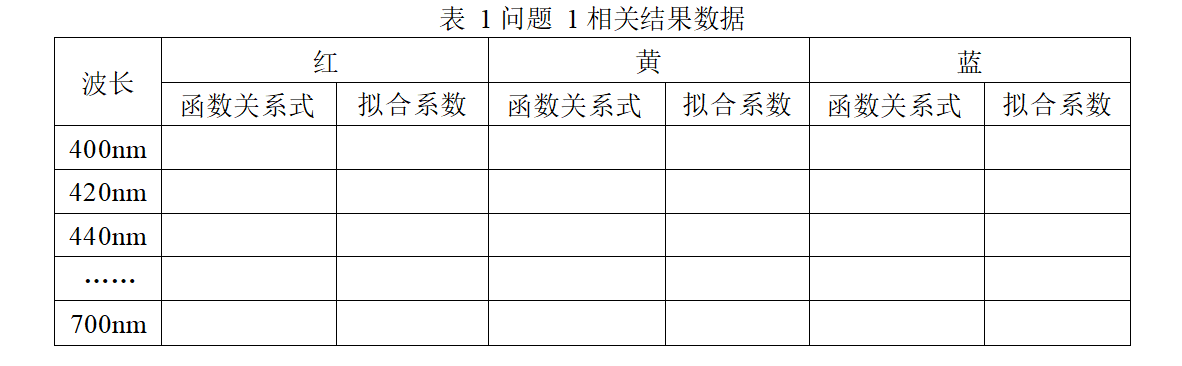

我们现在举例 一个SRAM存储器

假设其中是有19根地址线A0-A18

16根数据线:D0-D15

那么地址就是2的19次方=512K

然后16根地址线就是2个字节 每8位

总的大小是512K乘2

映射范围是0-512K

也就是所说的 0x80000

因为十六进制 1位代表了4个2进制比特位

那么0x80000 其中的一个0 就含有了4位二进制

而8是 111 1111 1111 1111 1111 可能再进一步 就是1000 这么来的吧

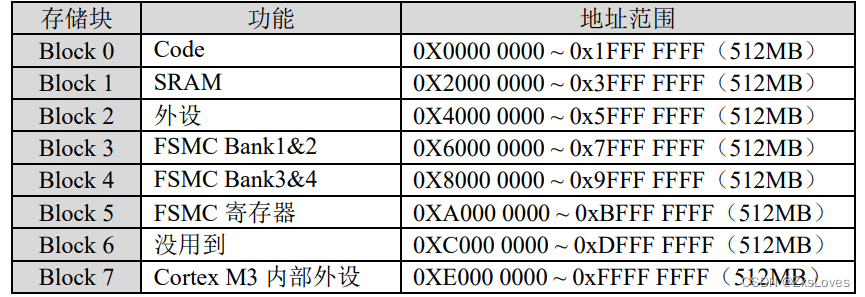

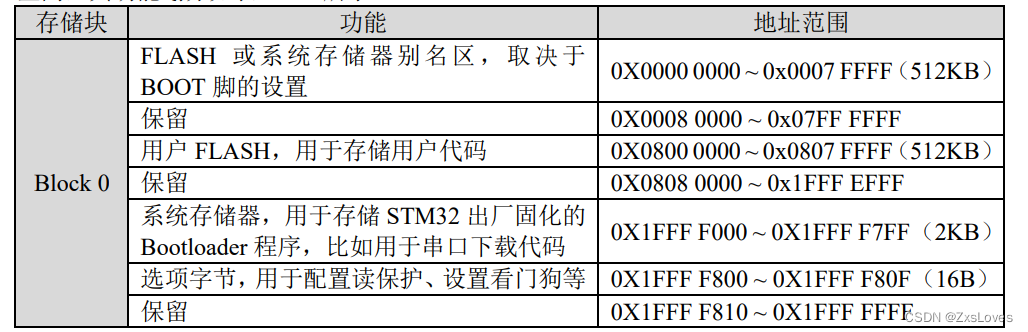

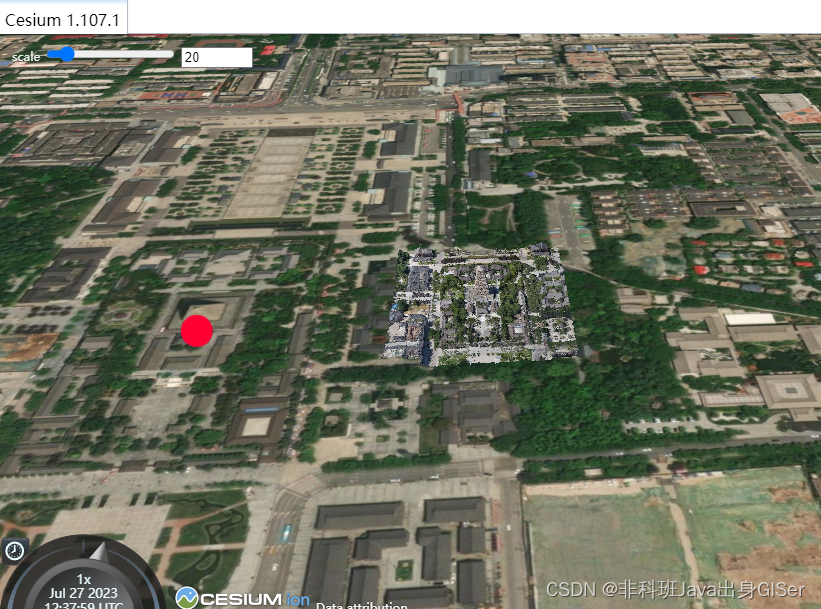

ST将4GB空间分成8个块,每个块512MB,如上图所示,从图中我们可以看出有很多保留区域(Reserved),这是因为一般的芯片制造厂家是不可能把4GB空间用完的,同时,为了方便后续型号升级,会将一些空间预留(Reserved)。

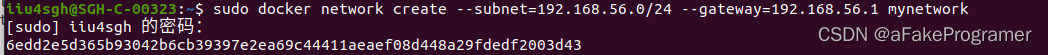

寄存器是单片机内部一种特殊的内存,可以实现对单片机各个功能的控制

简单来说: 寄存器是单片机内部的控制机构

简单的来说我们学习单片机就是学习用寄存器控制各种功能的产品

给存储器分配地址的过程叫存储器映射,寄存器是一类特殊的存储器,它的每个位都有特

定的功能,可以实现对外设/功能的控制,给寄存器的地址命名的过程就叫寄存器映射。

![【练】要求定义一个全局变量 char buf[] = “1234567“,创建两个线程,不考虑退出条件,打印buf](https://img-blog.csdnimg.cn/158df8a0b0db4788b75ad8e5ba8490ad.png)