(二)PCB常见走线等长设计

- 1.蛇形线的等长设计

- 2.DDR的等长分组

- 3.等长的拓扑结构

- 3.1 点对点连接

- 3.2 T型拓扑结构

- 3.3 菊花链拓扑结构

1.蛇形线的等长设计

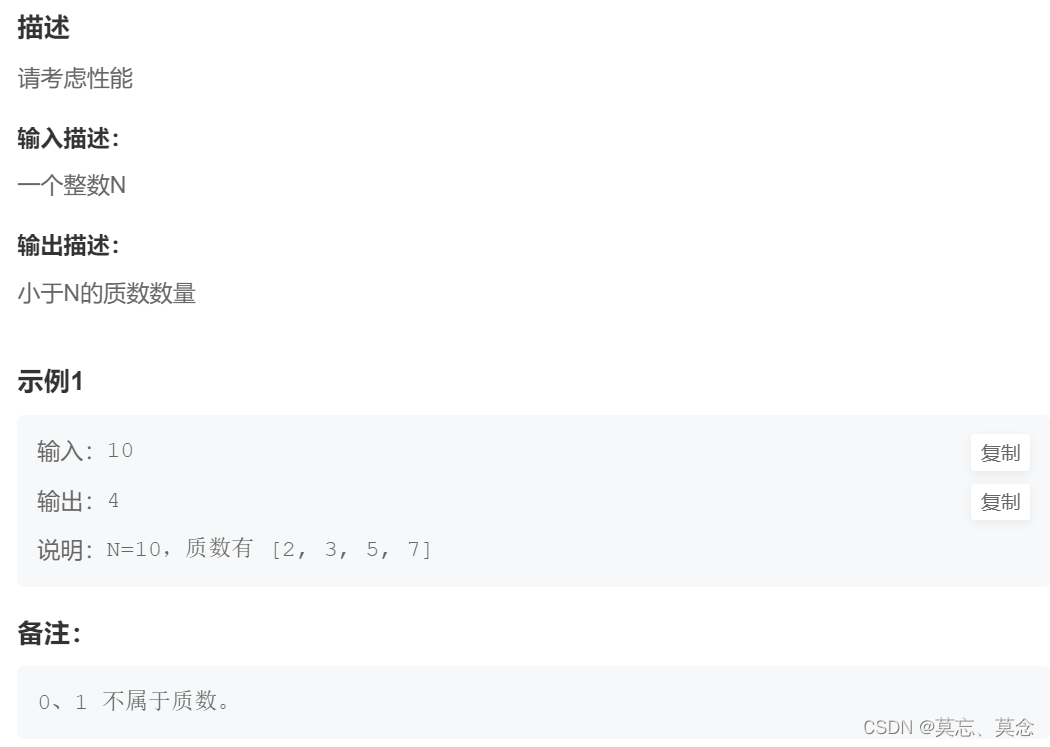

在 PCB 设计中,网络等长调节目的就是为了尽可能地降低信号在 PCB上传输延迟的差异。在 Altium Designer 中实现网络等长调节的方法如下:

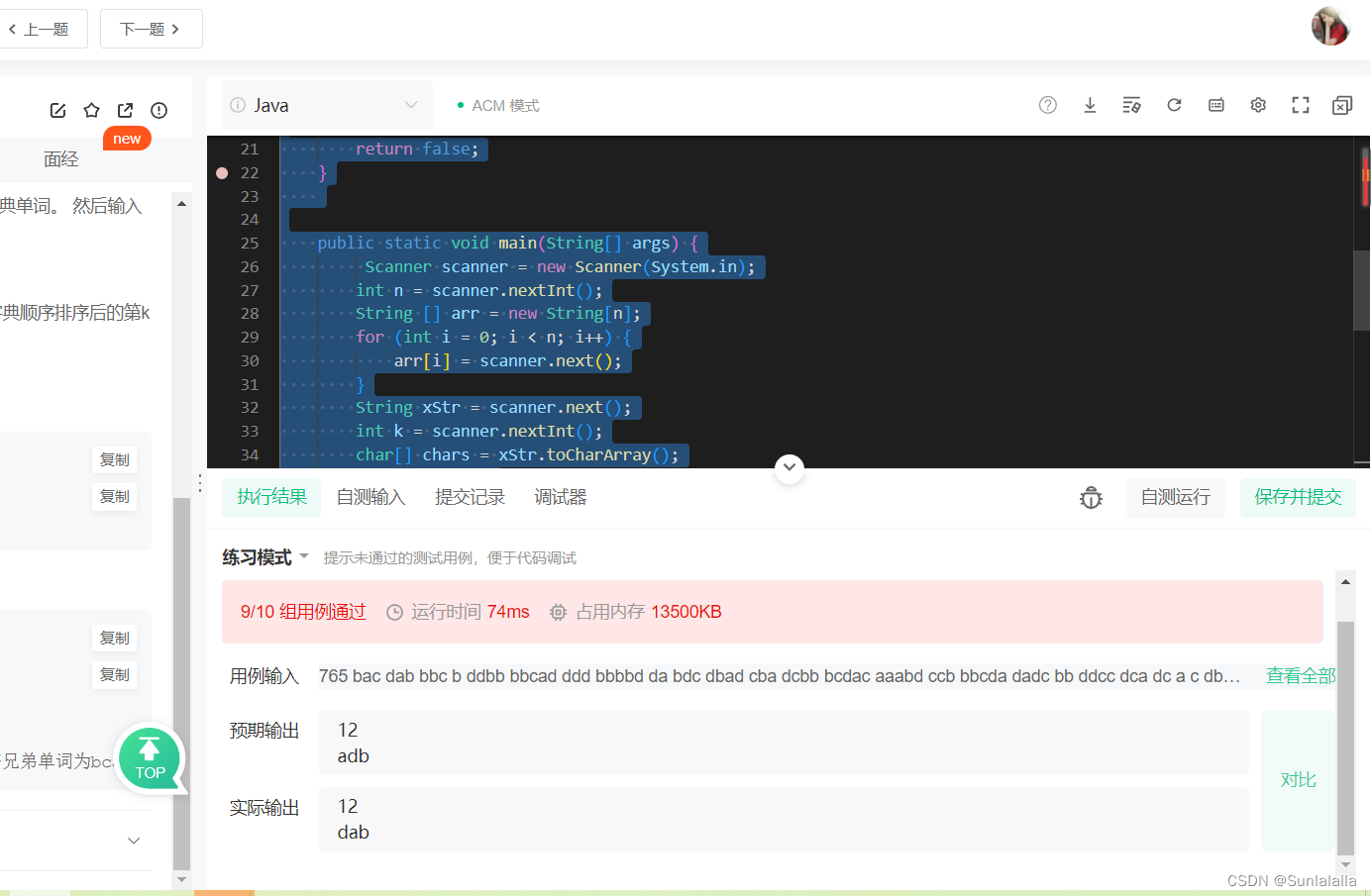

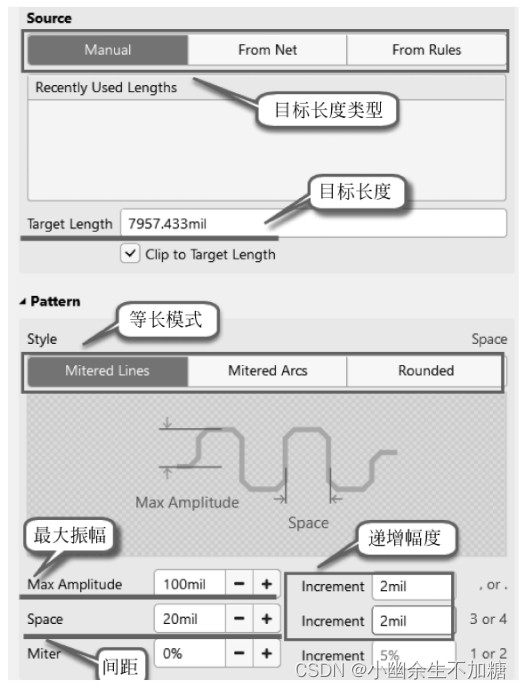

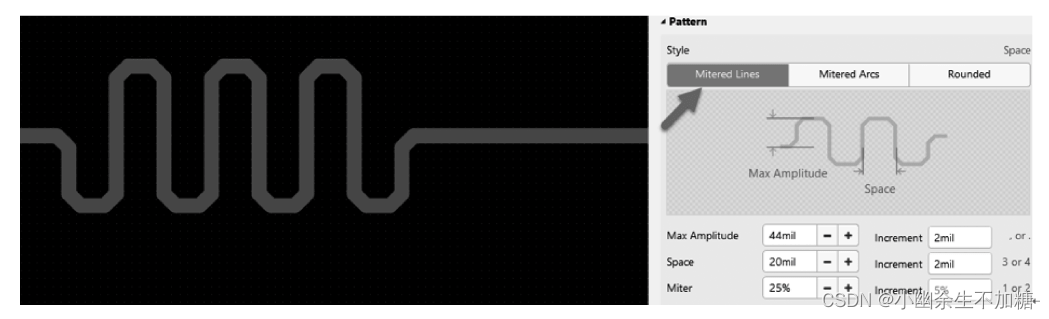

(1)在 Altium Designer 中网络等长调节可通过蛇形走线实现,在进行蛇形等长之前需要完成 PCB相应走线的连通,然后执行菜单栏中“布线”→“网络等长调节”命令,或者按快捷键U+R,单击需要等长的走线并按Tab 键调出“等长属性设置”面板,如图所示。

① Target Length 提供如下三种目标长度类型:

Manual:手工设置等长目标长度。

From Net:依据网络选择等长目标长度。

From Rules:依据规则设置目标长度。

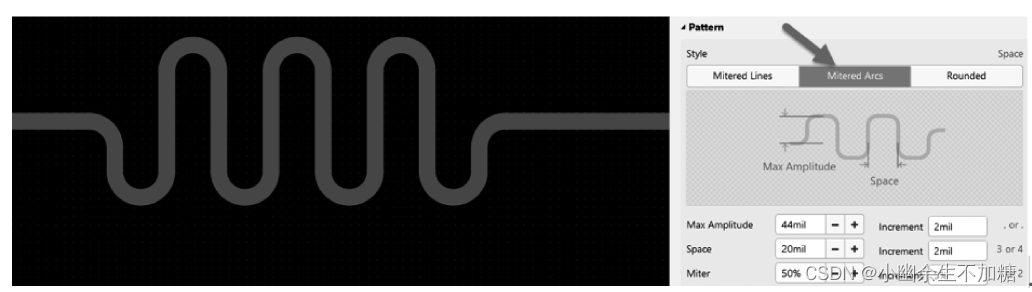

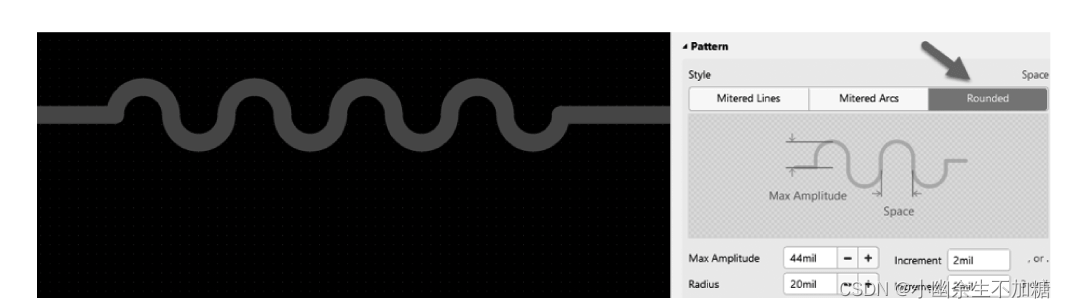

② Pattern 提供如下三种等长模式:

Mitered Lines:斜线条模式。

Mitered Ares 斜弧模式。

Rounded:半圆模式。

三种蛇形等长模式的效果如图所示,一般采用斜弧模式。

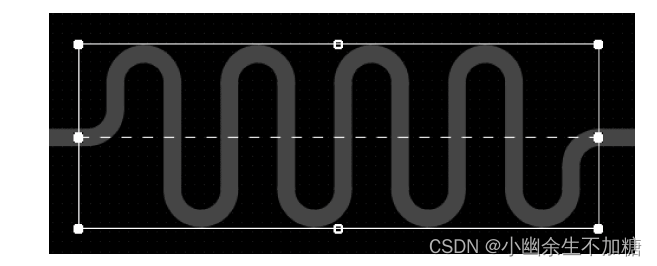

(2)等长参数设置完毕之后,在需要等长的信号线上滑动即可拉出蛇形线。在等长的状态下,按键盘上的<和>键可以分别调整蛇形线的上下振幅,数字键1减小拐角幅度,数字键 2 增大拐角幅度,数字键3 减小Space 间距,数字键4 增大 Space间距。

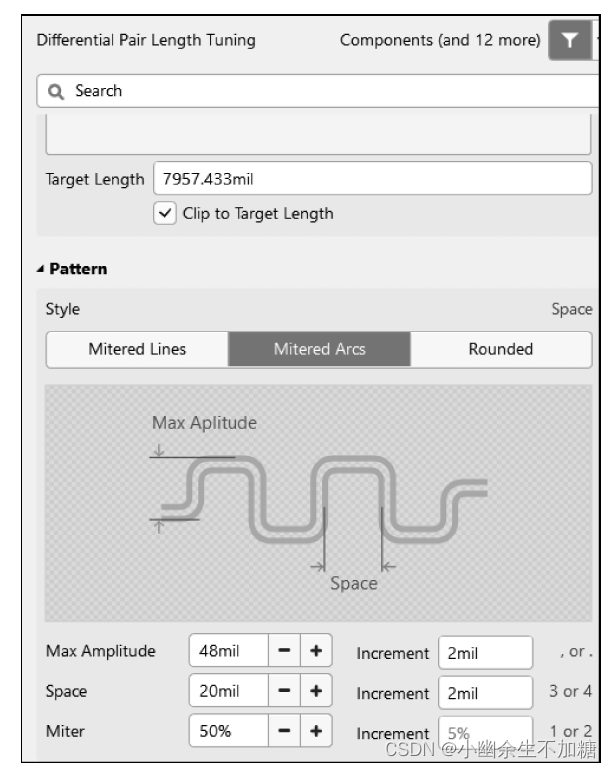

(3)在完成一段蛇形等长之后,如果需要调整蛇形线可以用鼠标拖动调制线进行调整, 如图所示。差分对蛇形线等长类似于单端蛇形等长,执行菜单栏中“布线”→“差分对网络等长调节”命令,或按快捷键U+P,单击需要等长的差分对并按Tab 键调出“差分对等长设置”面板,设置方式类似于单端等长的设置,如图所示。

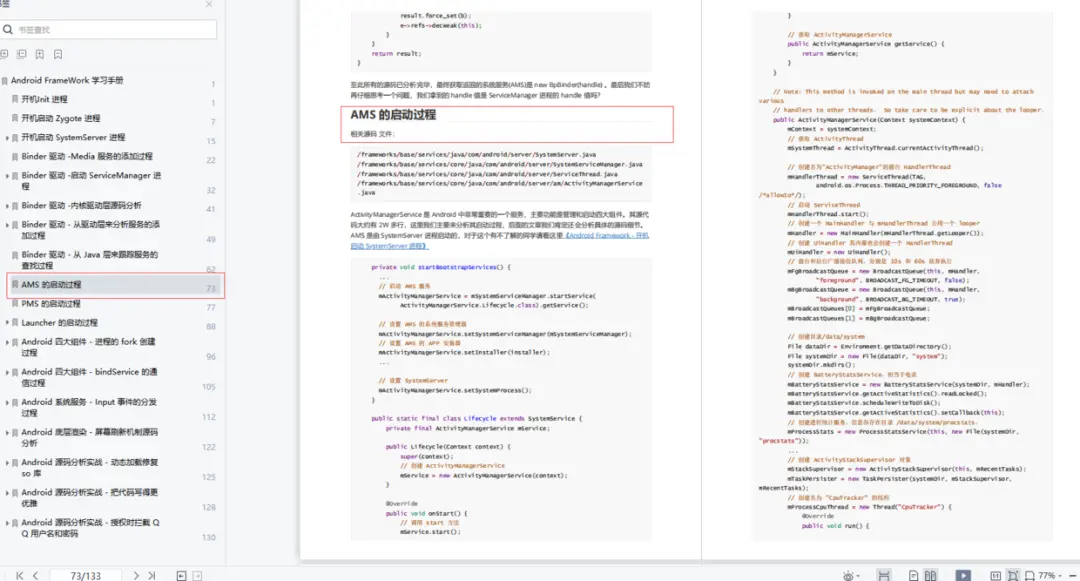

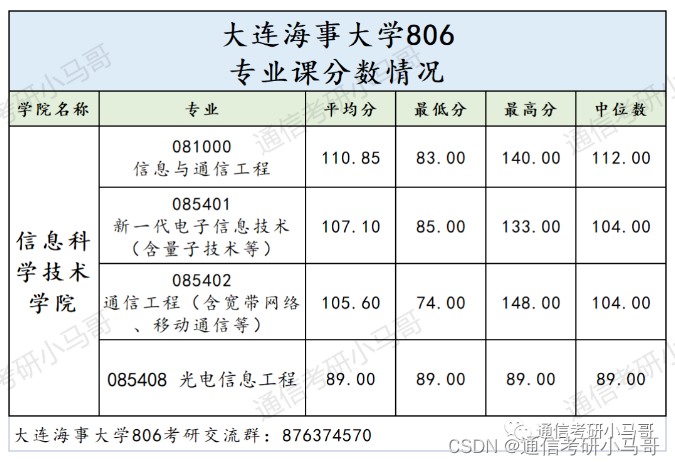

2.DDR的等长分组

DDR进行布线分组一般分为数据组和地址组两类。

数据组:数据线每8 根一组(D0D7/D8D15),外加相应的 DQS(数据锁存)差分对和 DQM(数据掩码)。注:DDR 数据线用 DQS 来锁存,数据线布线优先级最高。

地址组:包含地址线(A0~A14)、时钟线(CLK、CLKN)以及控制线(BA0、BA1、BA2、WE、CAS、ODT、RESET、CKE、RAS、CS 等)。注:地址、控制线需以CLK为基准线进行等长处理。CLK控制数据信号的采集,因此要比最长的数据线长。

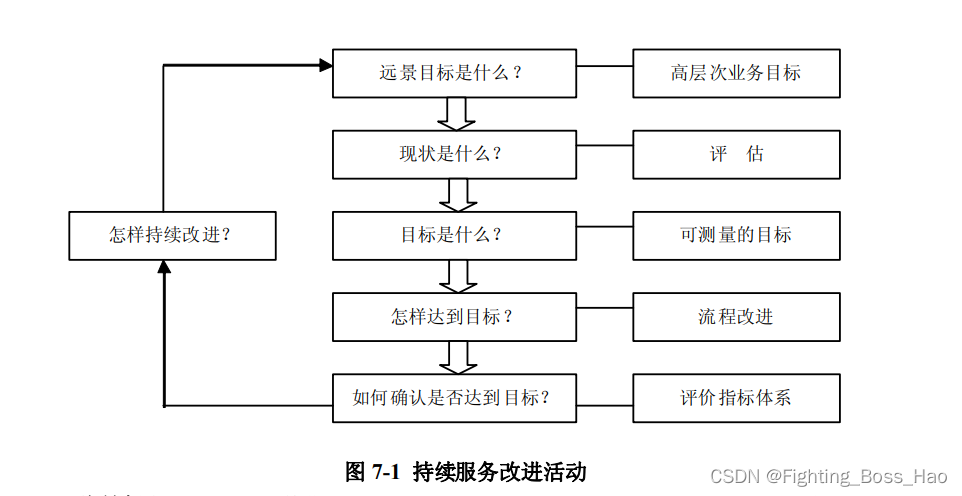

3.等长的拓扑结构

3.1 点对点连接

点对点连接,即一个焊盘连接到另一个焊盘,连接通道上是相对唯一的,主要是针对单片 DDR而言,如图所示。

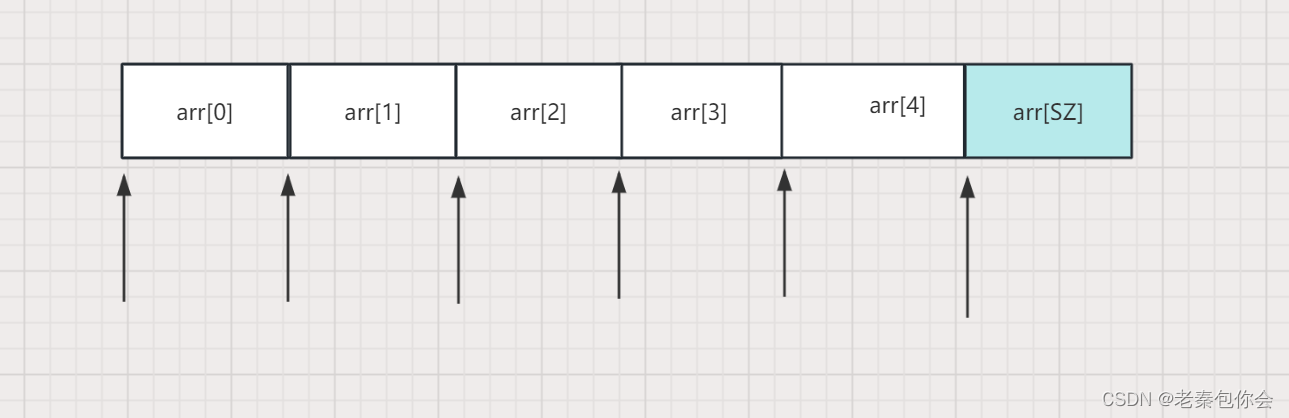

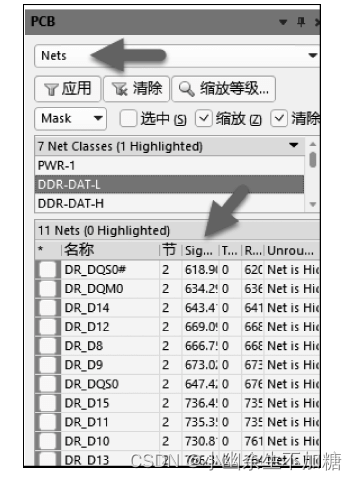

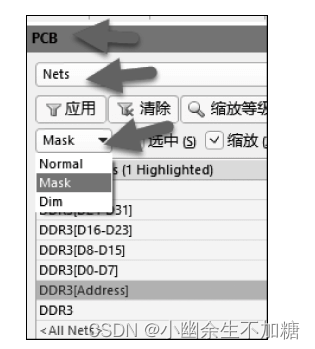

点对点的等长较为简单,只需在 Nets 中查看长度,参照组内最长走线进行等长即可,如图所示。若主控和 DDR 之间有排阻,如图所示。等长时可备份一个原理图文件,然后修改原理图,将电阻两端短接,导人PCB中,即可按点对点的方式等长。等长完成后,再把备份的原理图加到工程中,重新导入 PCB。注:在进行等长操作时,可使用 PCB 面板中的筛选工具,选择 Mask 或者 Dim 模式,可进行高亮操作,如图所示。

3.2 T型拓扑结构

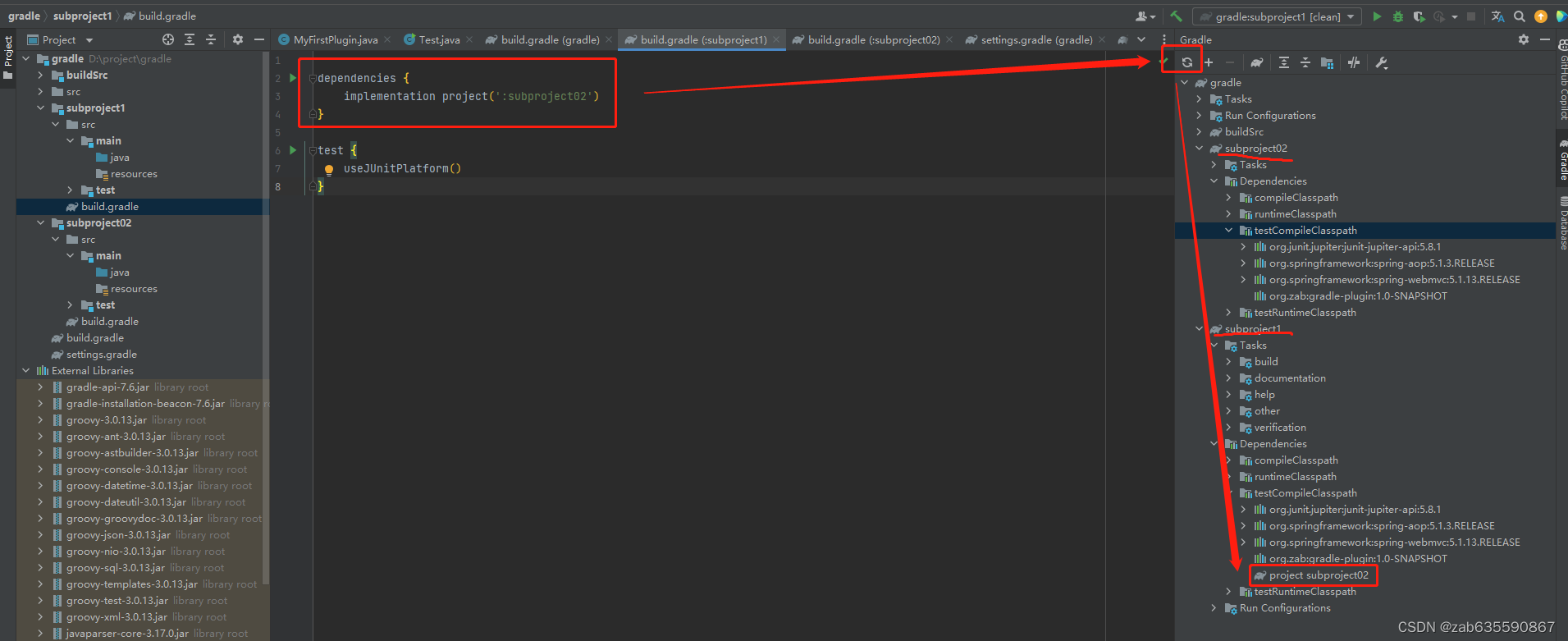

DDR2 及之后系列与DDR相比,少了延时补偿技术,为了不使每片 DDR2 的时钟线和数据选通信号的长度误差太大,一般可采用T型结构进行绕线等长。

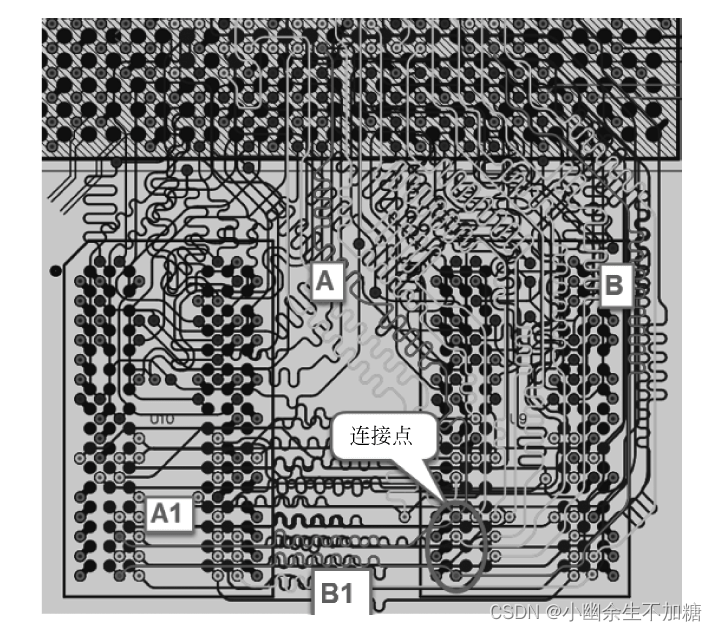

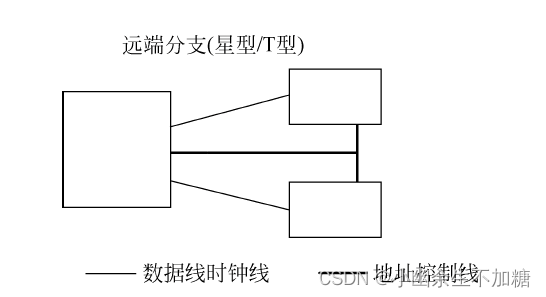

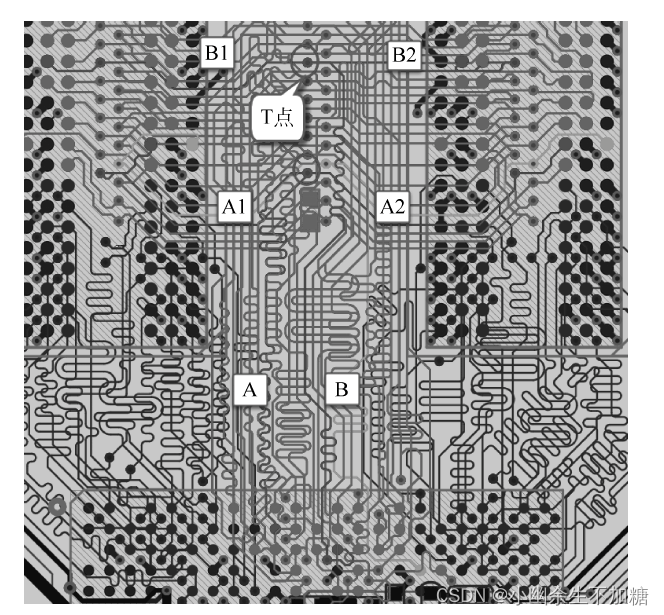

T 型等长,简易结构如图 所示。实际上就是让 CPU 到每一个 DDR 的走线长度相等,T点两边的分支走线要求尽可能短,长度尽可能相等,如图所示。实现A+A1=A+A2=B+B1=B+B2。

3.3 菊花链拓扑结构

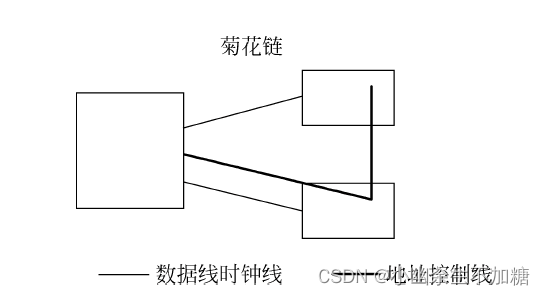

菊花链的结构相对比较简单,阻抗也比较容易控制,其简易结构如图 所示。从图中可看出,信号是在相邻两个元件之间进行传输的,从 CPU 到第一片 DDR,再到第二片 DDR。实际连接图如图 所示,实现 A=B,A1=B1。

注:经仿真验证,当DDR速率跑到1.6Gb/s时,相对T型连接,菊花链更能满足信号完整性要求。