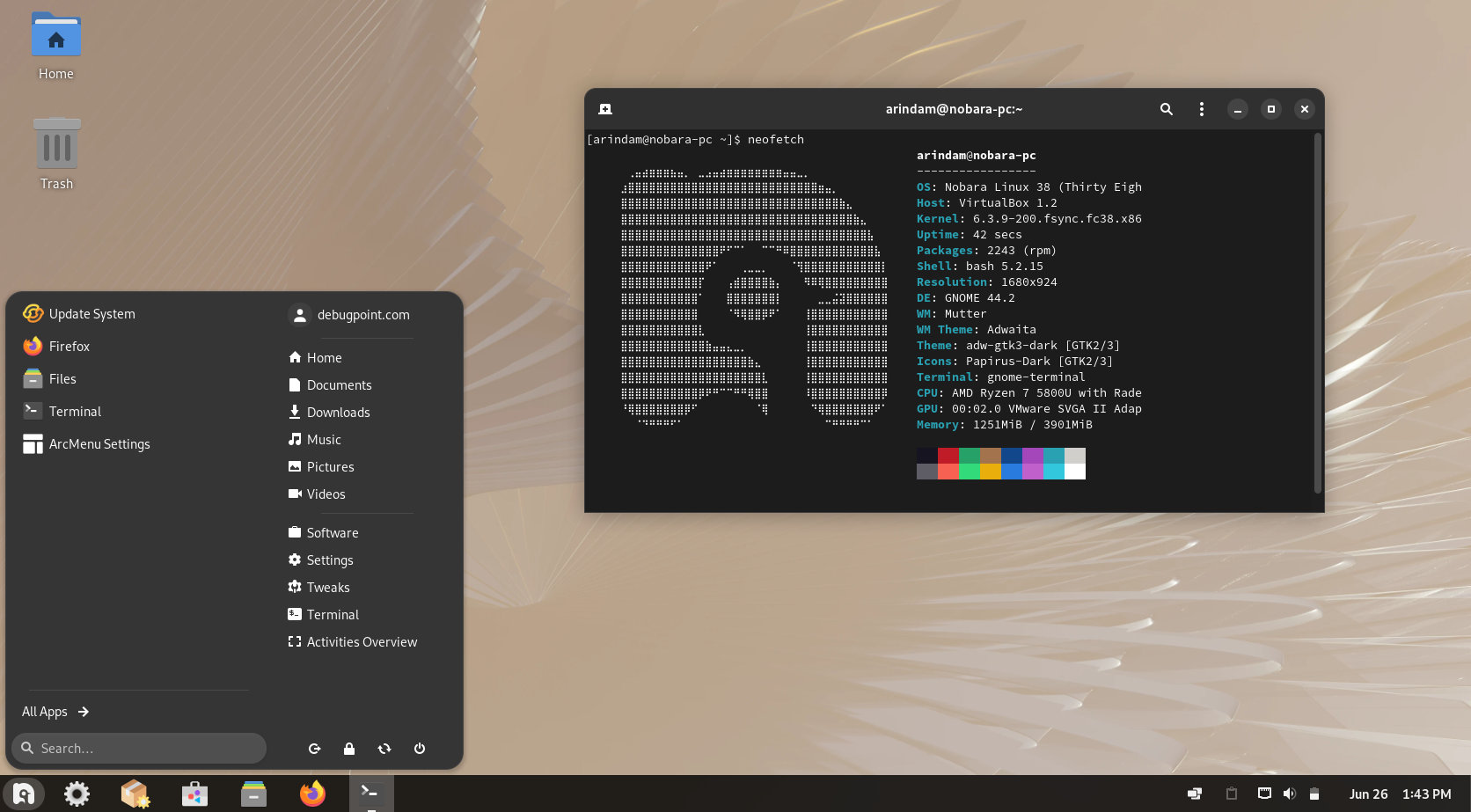

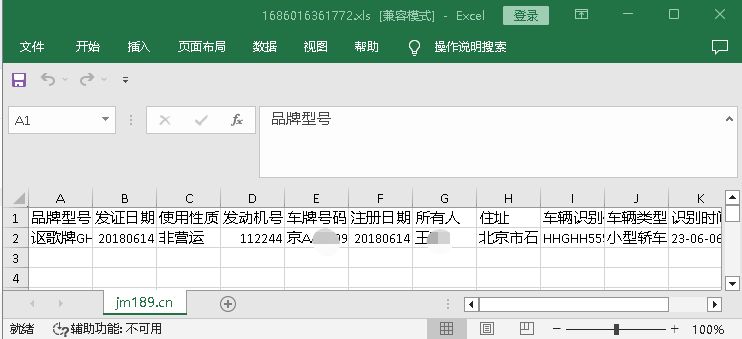

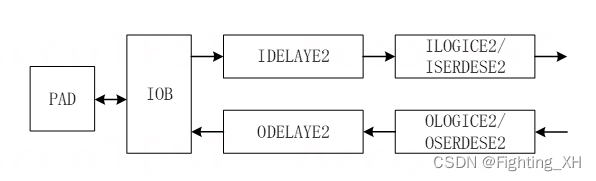

如下是7系列FPGA HP Bank I/O 资源:

其中ILOGIC是由许多的数据选择器和一个IDDR触发器构成。

在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3

IDELAY

简单介绍

输入信号延迟模块。每个I/O模块都包含了一个可编程的延迟模块IDELAYE,作用是把输入信号延时一段时间,然后将其直接转到器件逻辑。这样对于需要对齐的输入来说很有用。注意使用时候必须例化IDELAYCTRL。

四种工作模式:FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE模式

关于原语:其在7系列中称作IDELAYE2,Ultrascale器件中是IDELAYE3。

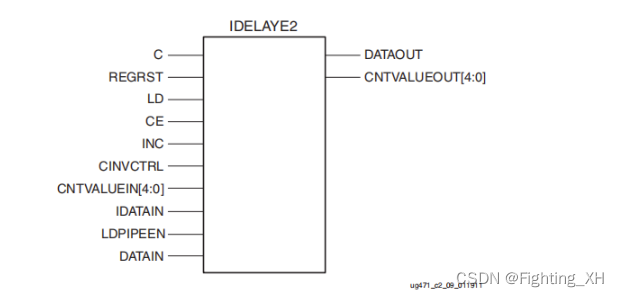

7系列 IDELAY2原语如下:

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.C(C), // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.DATAIN(DATAIN), // 1-bit input: Internal delay data input

.IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O

.INC(INC), // 1-bit input: Increment / Decrement tap delay input 增加或减少抽头数量

.LD(LD), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input

);

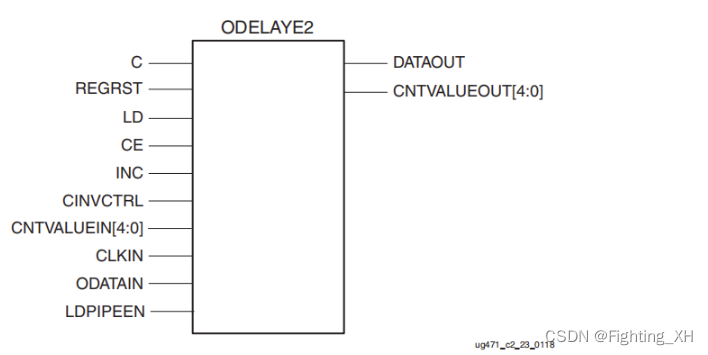

ODELAY

用作输出信号的延迟

HR BANK内没有ODELAY,HP BANK才有,被称为ODELAYE2。使用ODELAYE2时同样需要例化IDELAYCTRL.

原语如下:

ODELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("ODATAIN"), // Delay input (ODATAIN, CLKIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.ODELAY_TYPE("VAR_LOAD"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.ODELAY_VALUE(0), // Output delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

ODELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data/clock output

.C(CLK), // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input

.CLKIN(CLKIN), // 1-bit input: Clock delay input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.INC(1'b1), // 1-bit input: Increment / Decrement tap delay input

.LD(LD), // 1-bit input: Loads ODELAY_VALUE tap delay in VARIABLE mode, in VAR_LOAD or

// VAR_LOAD_PIPE mode, loads the value of CNTVALUEIN

.LDPIPEEN(LD), // 1-bit input: Enables the pipeline register to load data

.ODATAIN(D), // 1-bit input: Output delay data input

.REGRST(RST) // 1-bit input: Active-high reset tap-delay input

);

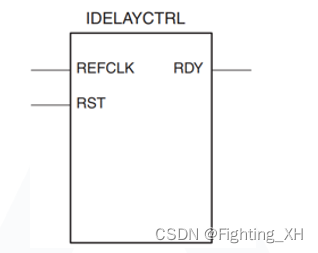

IDELAYCTRL

REFCLK:延迟校准的参考时钟

RST:高有效

RDY:高表示已校准

延迟控制模块,可将各个延迟线连续校准到其设定值,以减少工艺、电压和温度 (PVT) 变化的影响。

使用IDELAY和ODELAY的时候都要例化它。其原语如下:

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);