一. APB3概述

APB协议是AMBA总线协议系列的一部分,其接口简单、功耗较低,常用于连接低带宽的高性能外设,每次数据传输至少需要两个时钟周期,且无法同时进行读写操作。

APB作为系统中的从机,可以通过AHB、AHB-Lite、AXI、AXI4-Lite与系统总线相连。可以使用APB协议来访问外围设备的可编程控制寄存器。

相较于APB2,APB3新增了两个信号——PREADY、PSLVERR。

二. APB3接口信号

| 信号 | 信号源 | 信号描述 |

| PCLK | 时钟信号 | 时钟信号,上升沿有效 |

| PRESETn | 系统总线 | 复位信号,通常与系统总线复位链接,低电平有效 |

| PADDR | APB桥 | 地址总线,最高达32bit |

| PSELx | APB桥 | 表示从属设备数据传输的选择信号,高电平有效 |

| PENABLE | APB桥 | 使能信号,表示APB传输的第二个及随后的周期,高电平有效 |

| PWRITE | APB桥 | 读写信号,高电平为写,低电平为读 |

| PWDATA | APB桥 | 写入数据,最高达32bit |

| PRDATA | 从机接口 | 读取数据,最高达32bit |

| PREADY | 从机接口 | 准备信号,从机使用该信号延长APB的数据传输周期,高电平有效 |

| PSLVERR | 从机接口 | 传输失败指示信号,不强制要求,高电平有效 |

APB协议有两个独立的数据总线,一个用于读取数据,另一个用于写数据。总线最高达32位宽。因为总线没有各自的握手信号,所以不可能同时在两个总线上进行数据传输。

三. 操作状态

| IDLE | APB默认状态 |

| SETUP | 当需要进行数据传输时,对应设备的PSELx信号拉高,总线进入设置状态。 设置状态只会保持一个时钟周期 |

| ACCESS | PSELx信号拉高的下个时钟周期,PENABLE信号拉高,总线进入访问状态。 此时PADDR、PWRITE、PSELx、PWDATA信号必须保持稳定。 若PREADY信号保持为低,外围总线一直保持访问状态; 若PREADY信号为高,下个周期将退出访问状态; |

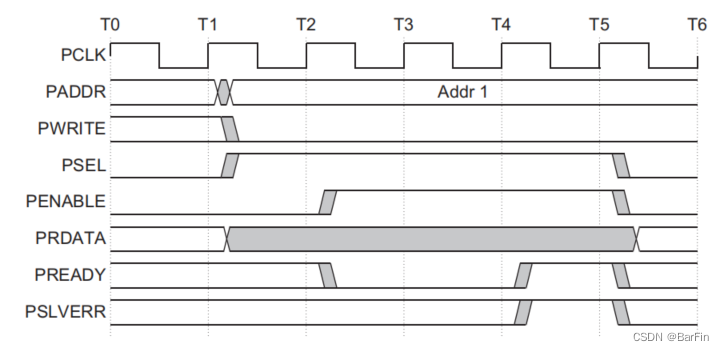

四. 写数据

时序说明:

(1)T0时刻,PSEL信号为低电平,APB总线处于IDLE状态;

(2)T1时刻,PSEL信号拉高,进入SETUP状态,PADDR、PWRITE、PWDATA准备就绪;

(3)T2时刻,PENABLE信号拉高,进入ACCESS状态,但由于此时PREADY信号为低,总线保持在ACCESS状态;

(4)T3时刻,PREADY信号拉高,标志着下个时钟上升沿到来之前,数据传输完成;此时PSLVERR信号为高,标志着该笔写入数据有误;

注:

- 数据传输完成后,PENABLE信号拉低,PSEL信号根据是否继续传输而定;

- 当PENABLE信号为低时,PREADY信号可以为任意值;

- 建议直到下次数据传输前,不更改PADDR和PWRITE信号的值,可以降低功耗;

- 当PSEL、PENABLE和PREADY均为高电平时,PSLVERR信号才有效;

五. 读数据

读数据的时序与写数据基本一致,区别仅为PRDATA无需再SETUP阶段准备就绪,不晚于PREADY状态有效即可;

六. PSLVERR映射

- AXI-APB

写错误会映射到BRESP[1],读错误会映射到RRESP[1]。

- AHB-APB

读写错误均会被映射到HRESP[0]。

APB协议下载地址:Documentation – Arm Developer