这里写自定义目录标题

- 背景

- ISE PR结果

- PlanAhead结果

- 使用ISE twx

- 使用PlanAhead综合、实现

- 问题

- 分析

- Timer Settings

- 结论?

背景

最近调试一个老型号FPGA,时序问题分析,方便以后参考。

ISE PR结果

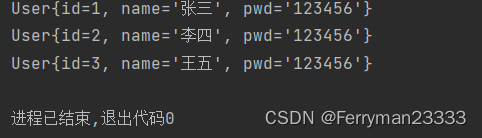

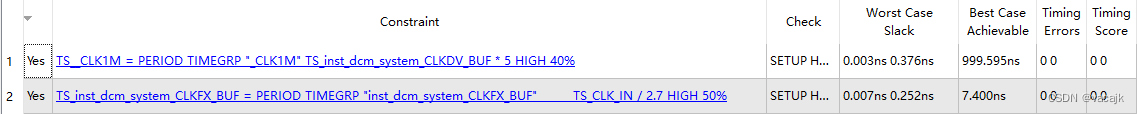

在下图可以看到All Constraints Met,表明时序满足

点击链接,进入Timing Constraints页面,可以看到Timing Score为0,表明没有时序问题(最差的一条slack为0.007ns)

PlanAhead结果

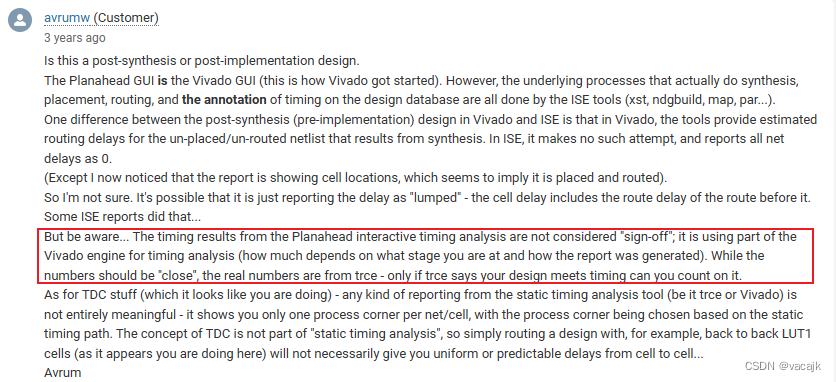

使用ISE twx

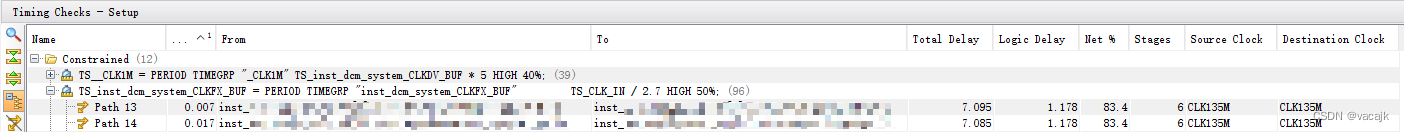

双击ISE内的Analyze Timing / Floorplan Design (PlanAhead)按钮,自动打开PlanAhead分析时序(其实用的就是ISE的PR twx文件)

下图可以看到slack一样,也是0.007

使用PlanAhead综合、实现

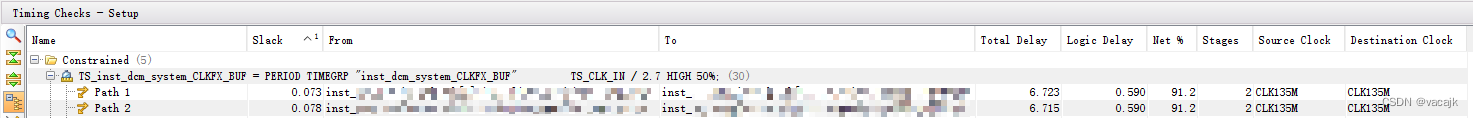

使用PlanAhead创建RTL工程,然后综合、实现(其实调用的还是ISE的综合、实现工具,只是操作方法跟Vivado类似)

下图可以看到,slack情况更好一些

说明工具差别大

问题

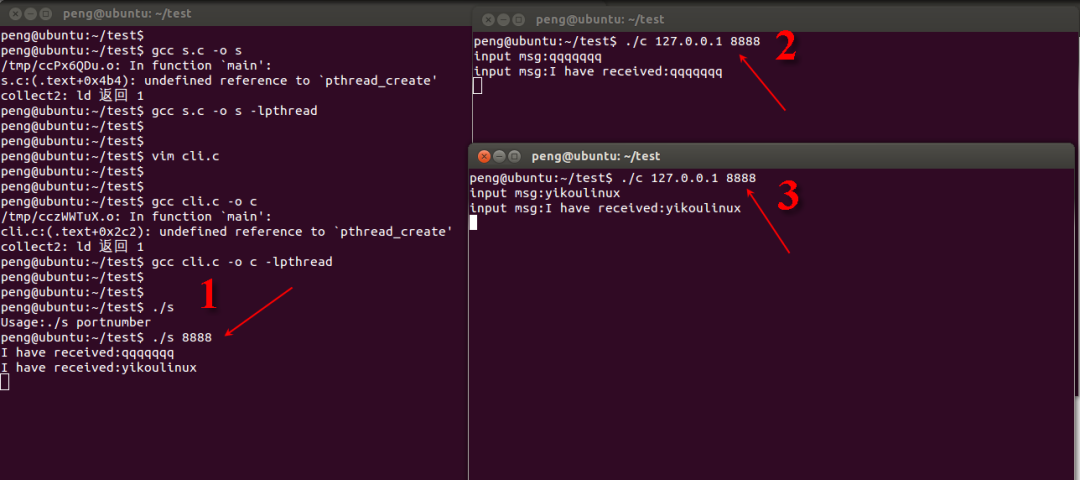

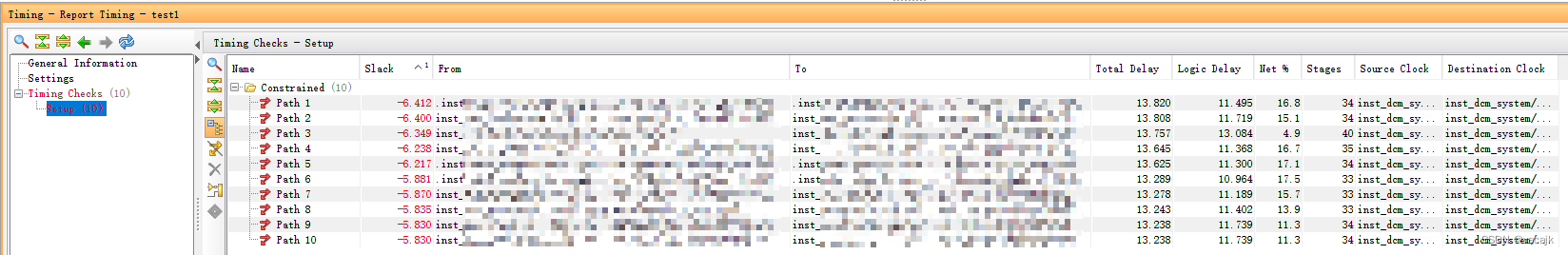

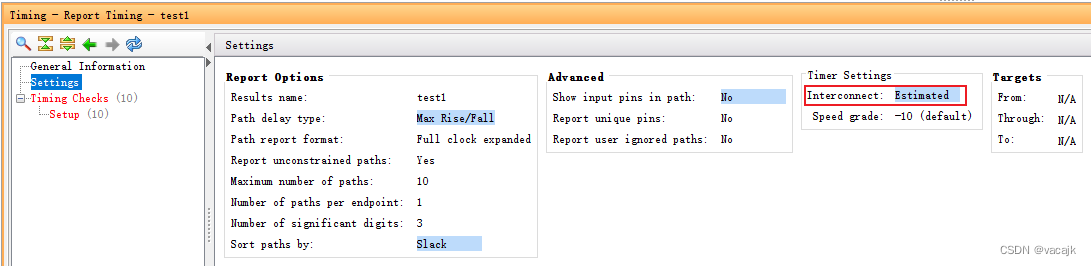

在PlanAhead中使用report_timing得到最差路径(命令:report_timing -name test1 -max_paths 10)

下图可以看到,有非常大的slack

这里非常不合理,有冲突:

- PR结果满足时序

- 使用report_timing又不满足时序

分析

Timer Settings

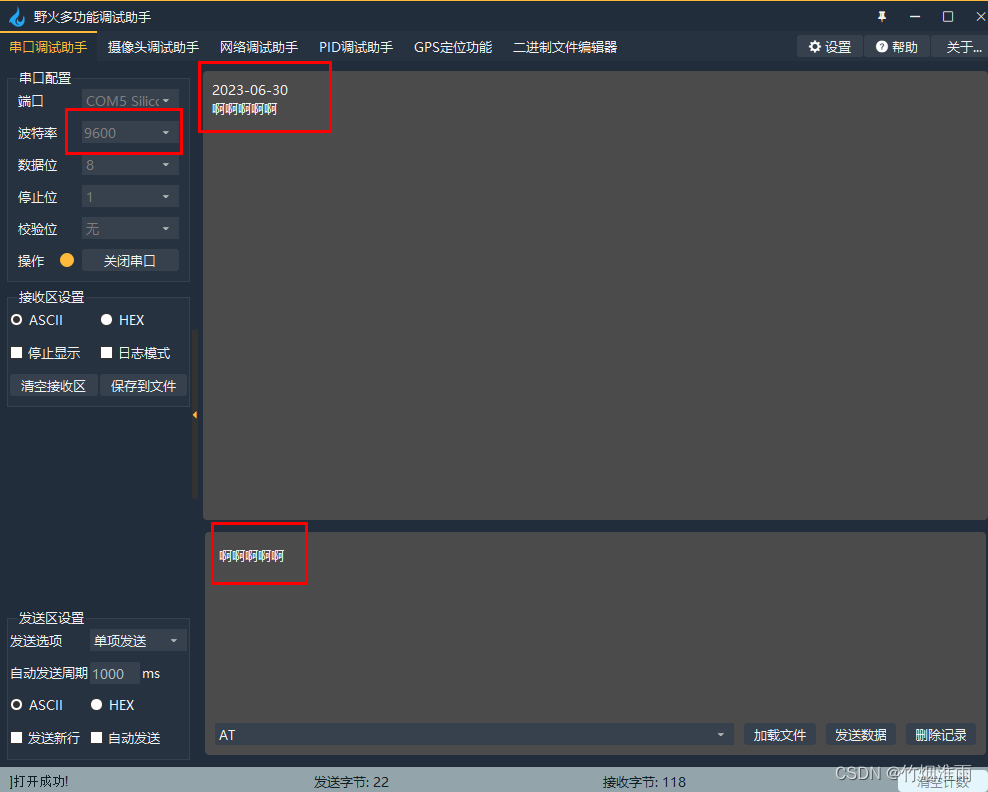

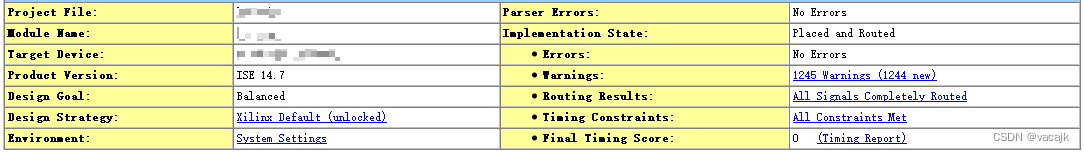

查了很多资料,最终发现在report_timing中的Timer Settings有问题,如下图:Interconnect的参数为:estimated

关键信息:

Planahead 14.7 - How to report the delay of a specific net

XILINX时序报告重要参数的含义

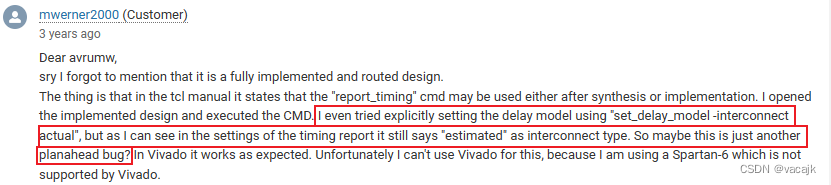

我也使用set_delay_model -interconnect actual; report_timing -name test1 -max_paths 10命令进行了尝试,依然没有使用真实的PR结果进行分析,报出的仍然是estimated结果。

结论?

- 在PlanAhead中使用report_timing不能作为最终的PR timing参考?

- 可能就是PlanAhead的bug?

- 只有ISE的trce分析结论才是准确的?

或者有哪位大侠可以指导一下,应该怎们才能让PlanAhead报出actual下的timing