一.SPI协议简介

SPI 协议是由摩托罗拉公司提出的通讯协议(Serial Peripheral Interface),即串行外围设备接口,允许芯片与外部设备以全双工、同步、串行方式通信。此接口可以被配置成主模式,并为外部从设备提供通信时钟(SCK)。接口还能以多主配置方式工作。它可用于多种用途,包括使用一条双向数据线的双线单工同步传输,还可使用CRC校验的可靠通信。

它被广泛地使用在 ADC、LCD 等设备与 MCU 间,要求通讯速率较高的场合。

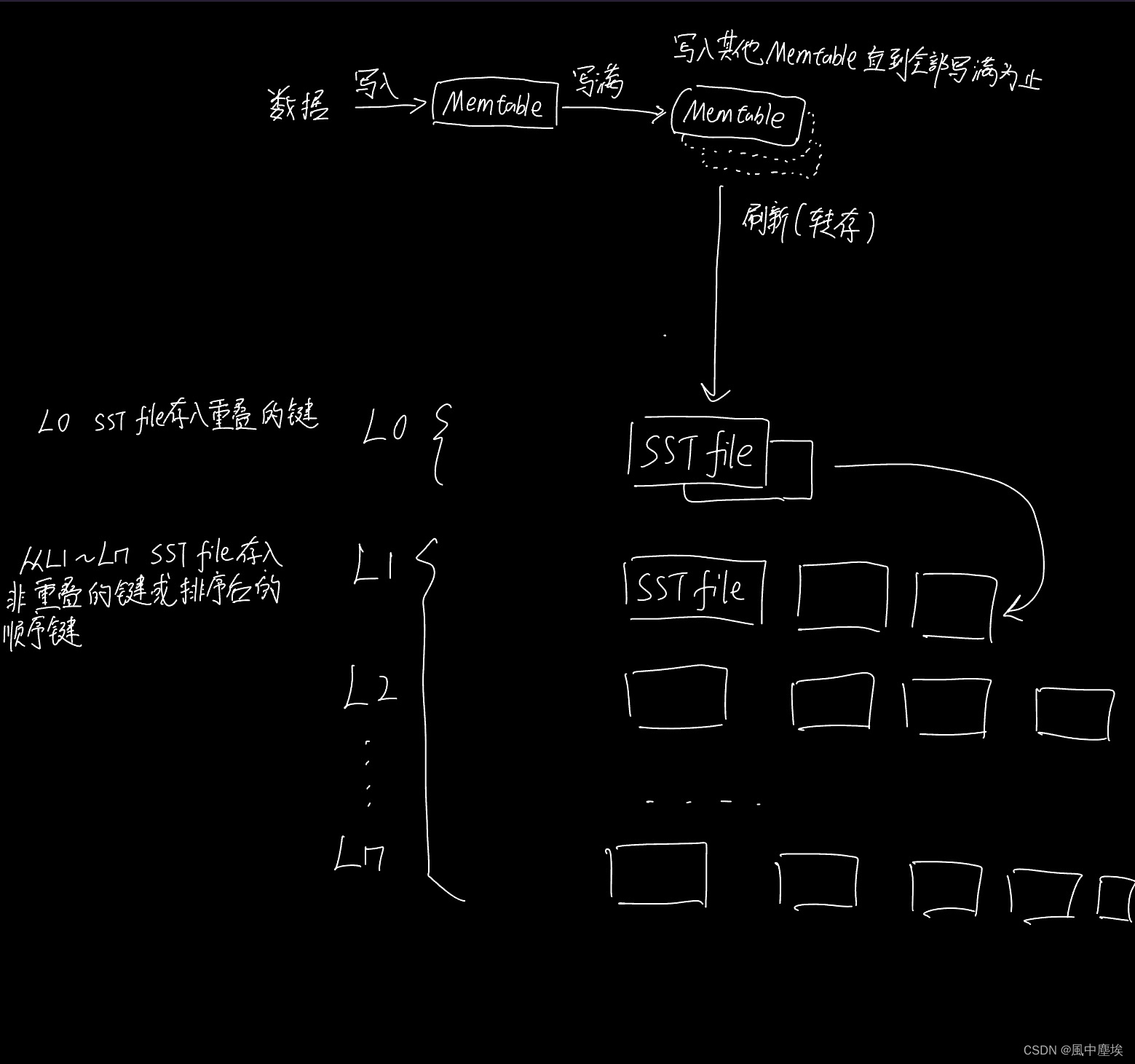

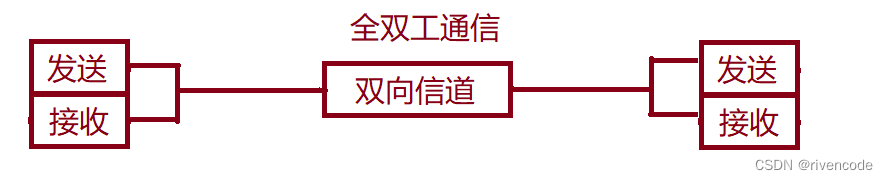

SPI一般采用双向全双工通信方式:

全双工通信:在同一时刻,两个设备之间可以同时收发数据,全双工方式无需进行方向的切换,这种方式要求通讯双方均有发送器和接收器,同时,需要2根数据线。

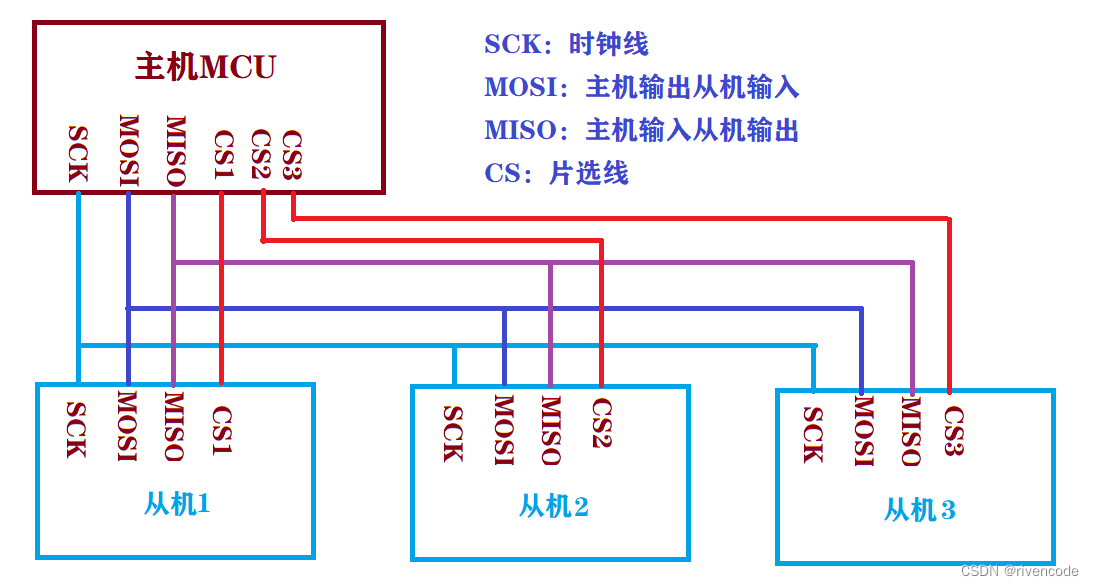

二.SPI物理层

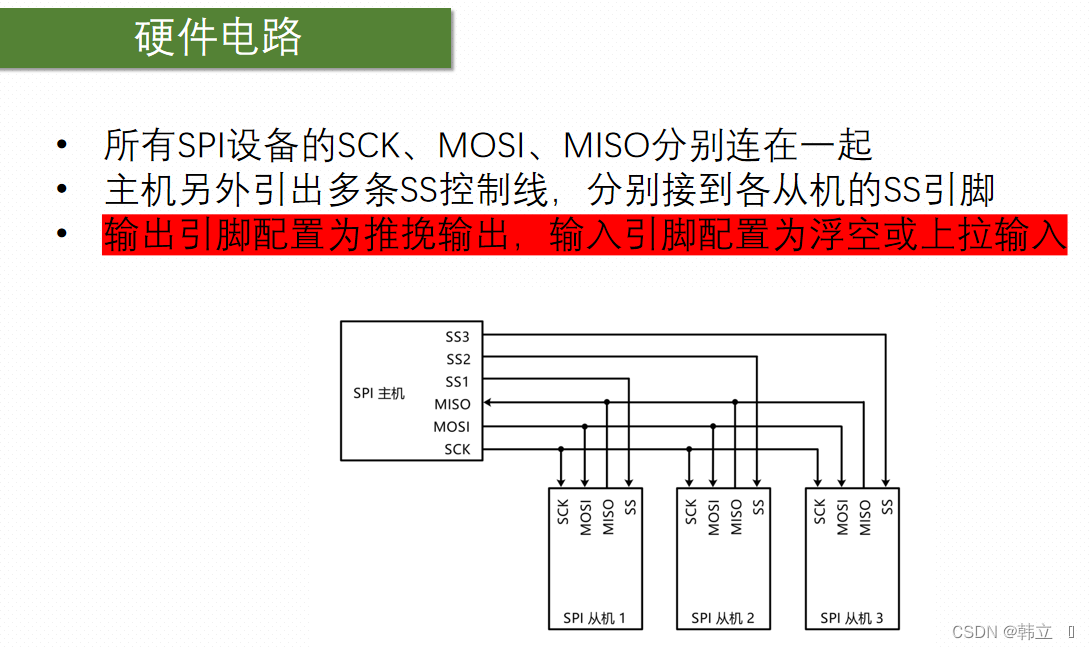

SPI 通讯设备之间的常用连接方式:

所有主设备或从设备的信号线 SCK、MOSI 及 MISO 同时并联到相同的 SPI 总线上,都共同只使用这 3 条总线;

SPI所有通信线都是单端信号,它们的高低电平都是相对GND的电压差,所以单端信号,所有设备还需要共地。

CS片选信号线

(Slave Select):从设备选择信号线,即为片选信号线,也称为 NSS、CS。当有多个 SPI 从设备与 SPI 主机相连时,而每个从设备都有独立的这一条NSS信号线,本信号线独占主机的一个引脚,即有多少个从设备,就有多少条片选信号线。当主机要选择从设备时,把该从设备的 NSS信号线设置为低电平,该从设备即被选中,主机开始与被选中的从设备进行 SPI 通讯,则其它未被选中(NSS引脚为高电平)的从设备会忽略总线上的数据传输

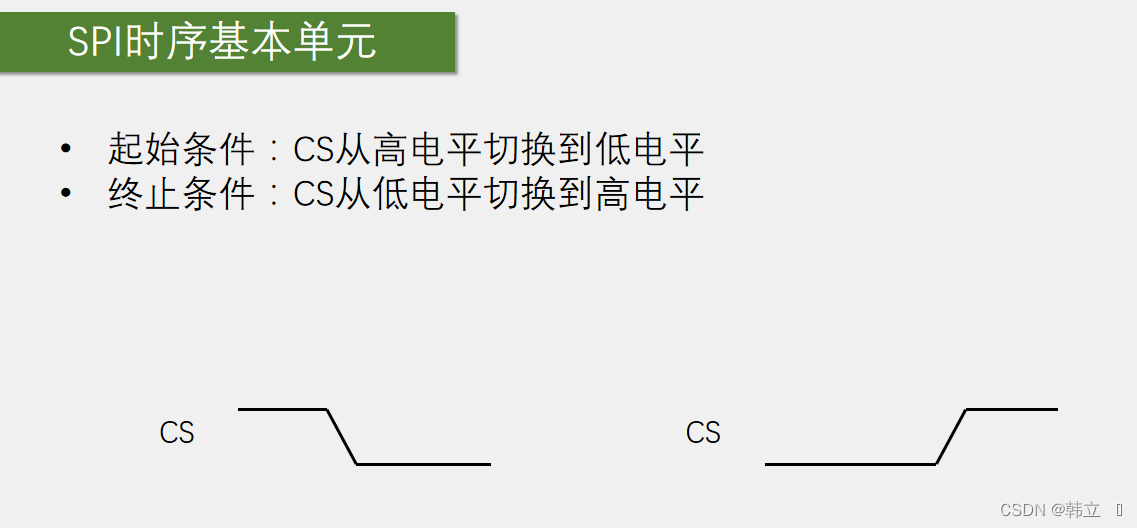

SPI 通讯以 CS 线置低电平为开始信号,以 CS 线被拉高作为结束信号。

SCK时钟信号线

SCK (Serial Clock):时钟信号线,用于通讯数据同步。只能由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不一样,STM32 的 SPI 时钟频率最大为fpclk/2,两个设备之间通讯时,通讯速率受限于低速设备。

MOSI主机发送从机接收数据线

MOSI (Master Output, Slave Input):主设备输出/从设备输入引脚。

主机向从机发送数据,从机接收主机发送的数据

MOSI主机接收从机发送数据线

MISO(Master Input,,Slave Output):主设备输入/从设备输出引脚。

从机向主机发送数据,主机接收从机发送的数据

三.SPI硬件初始化:

输出引脚(SCK,MOSI,CS):推挽输出,高低电平均有很强的驱动能力,这将使得SPI引脚信号的下降沿和上升沿非常迅速,不像I2C下降沿非常迅速,但是下降沿就非常缓慢。SPI信号变化快,自然它就能达到更高的传输速度。一般SPI信号都能轻松达到MHz的速度级别。I2C并不是不想使用更快的推挽输出,而是I2C要实现半双工,经常要切换输入输出,而且I2C又要实现多主机的时钟同步和总线仲裁,这些功能都不允许I2C使用推挽输出。(否则容易导致电源短路,I2C选择更多的功能,自然放弃更强的性能)

输入引脚(MISO):浮空或上拉输入

SPI有个缺点:如果三个从机始终都是推挽输出,主机一个是输入,势必会导致冲突。规定:当从机的SS引脚为高电平时,也就是从机未被选中,它的MISO引脚必须切换为高阻态,高阻态就相当于引脚断开,不输出任何电平。这样就可以防止一条线有多个输出,而导致的电平冲突的问题。在SS为低电平时,MISO才允许变为推挽输出。

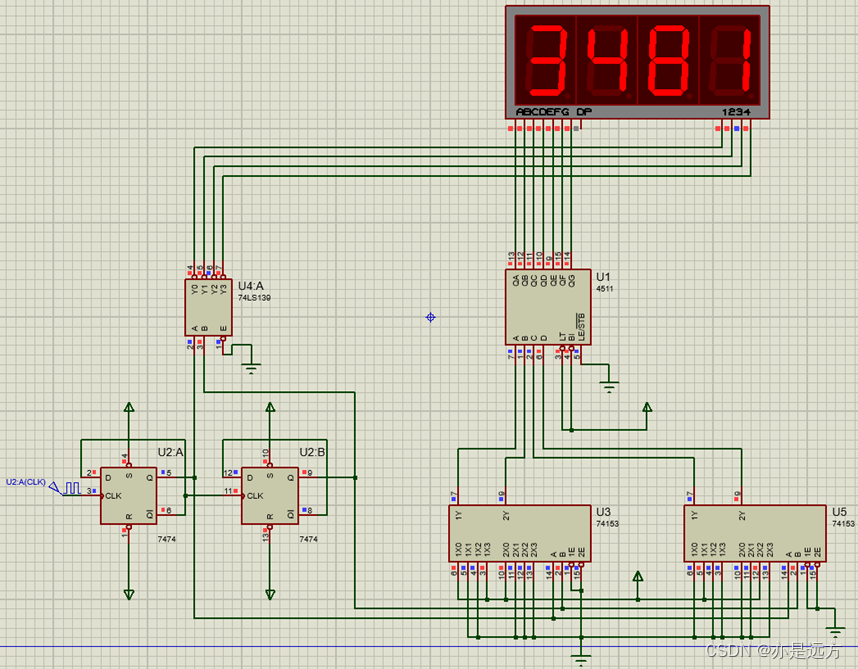

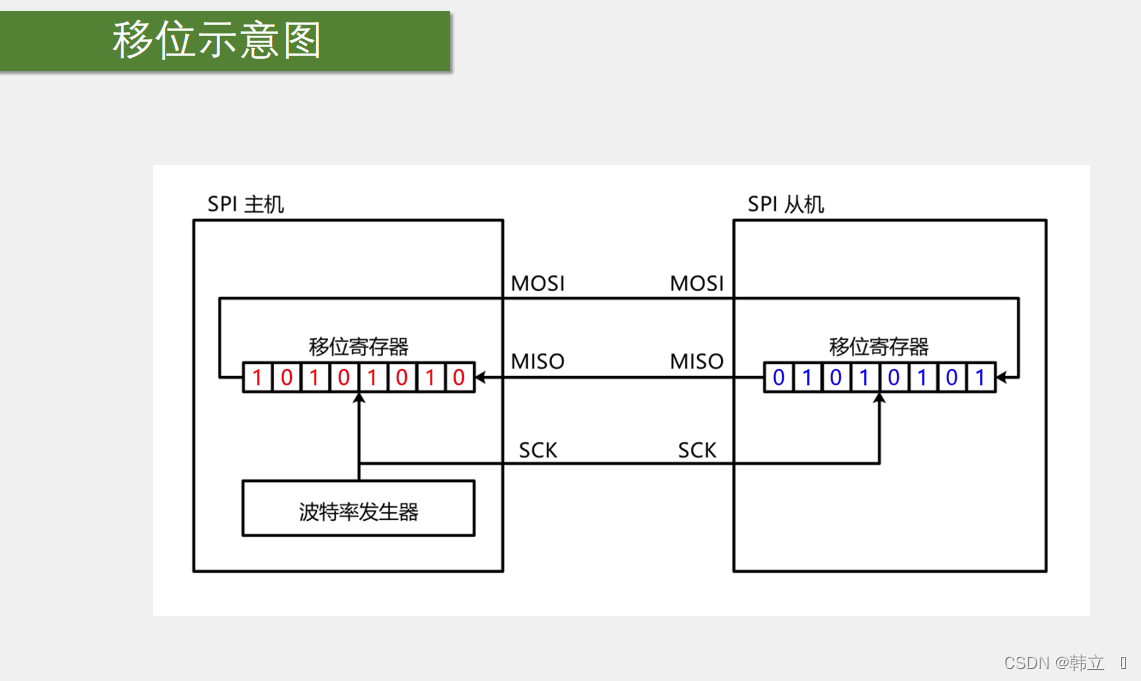

四:SPI移位交换数据核心示意图(交换一个字节)

波特率发生器时钟的上升沿,所有移位寄存器向左移动一位,移出去的位放到引脚上,波特率发生器的下降沿,引脚上的位,采样输入到一位寄存器的最低位。

假设主机有数据10101010要发送到从机。同时从机有个数据01010101要发送到主机。那我们可以驱动时钟, 先产生一个上升沿,此时所有的位向左移动一位。那移出去的数据就被放到通信线上,相当于放到了输出数据寄存器。MOSI数据是1,所以MOSI的电平就是高电平,MISO数据是0,所以MISO的电平就是低电平。这是第一个时钟上升沿执行的结果。把主机和从机中移位寄存器的最高位,分别放到MOSI和MISO的通信线上,这就是数据的输出。

五:SPI协议层

1:起始条件和终止条件

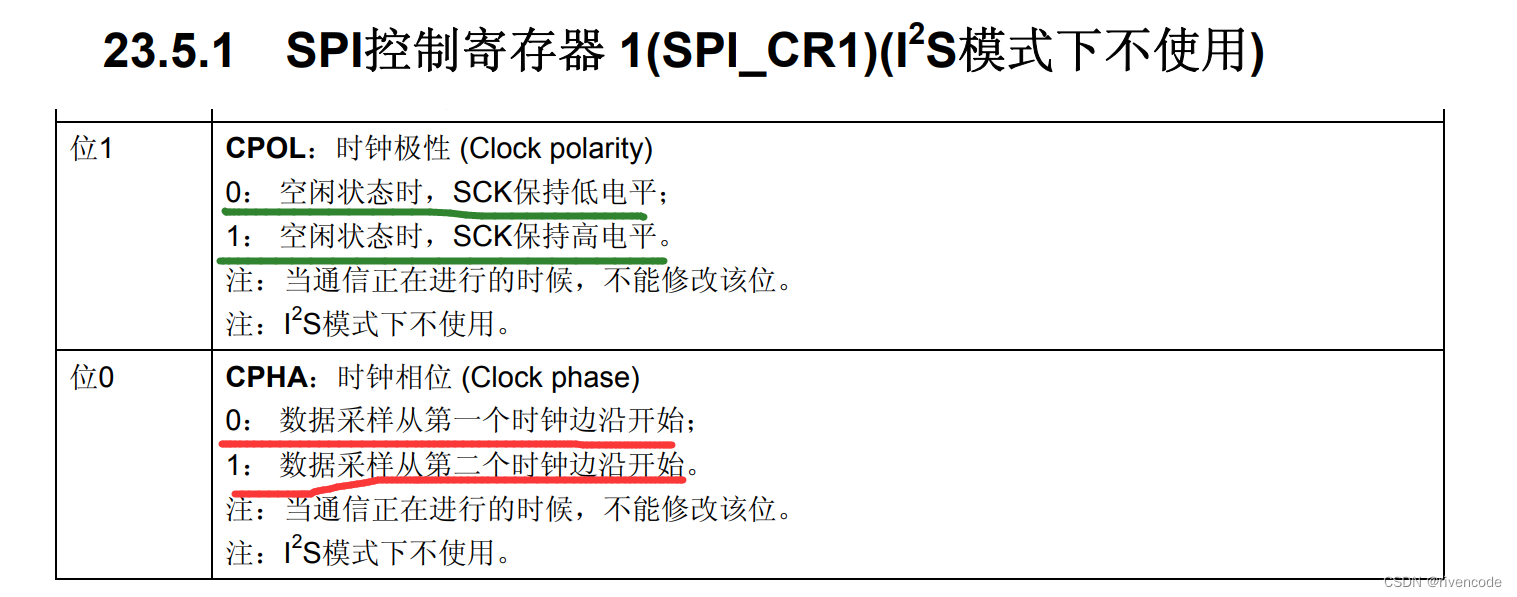

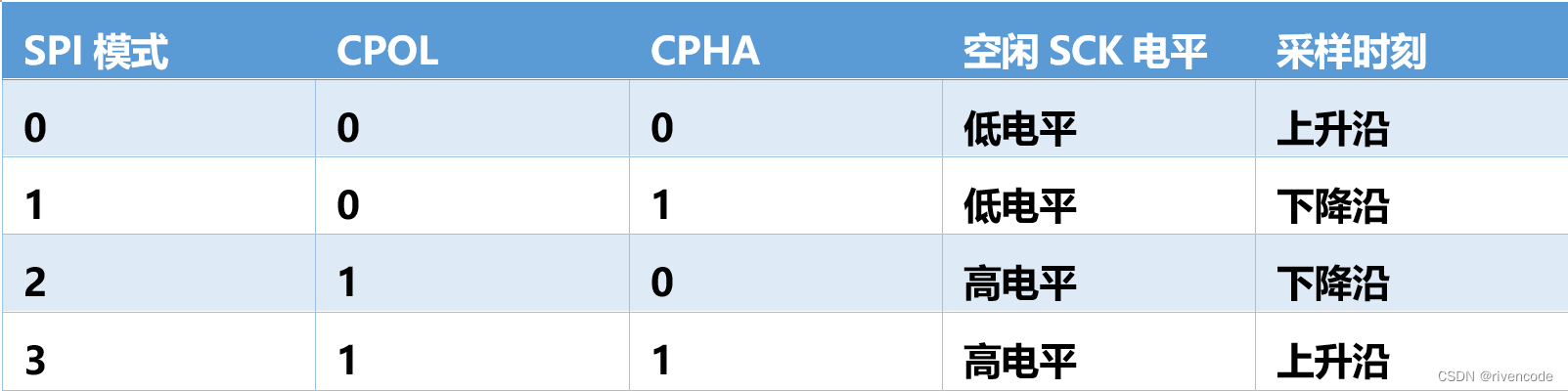

CPOL(Clock Polarity)时钟极性

CPHA(Clock Phase)时钟相位

以上两位组合后可有4种模式,实现的功能一样

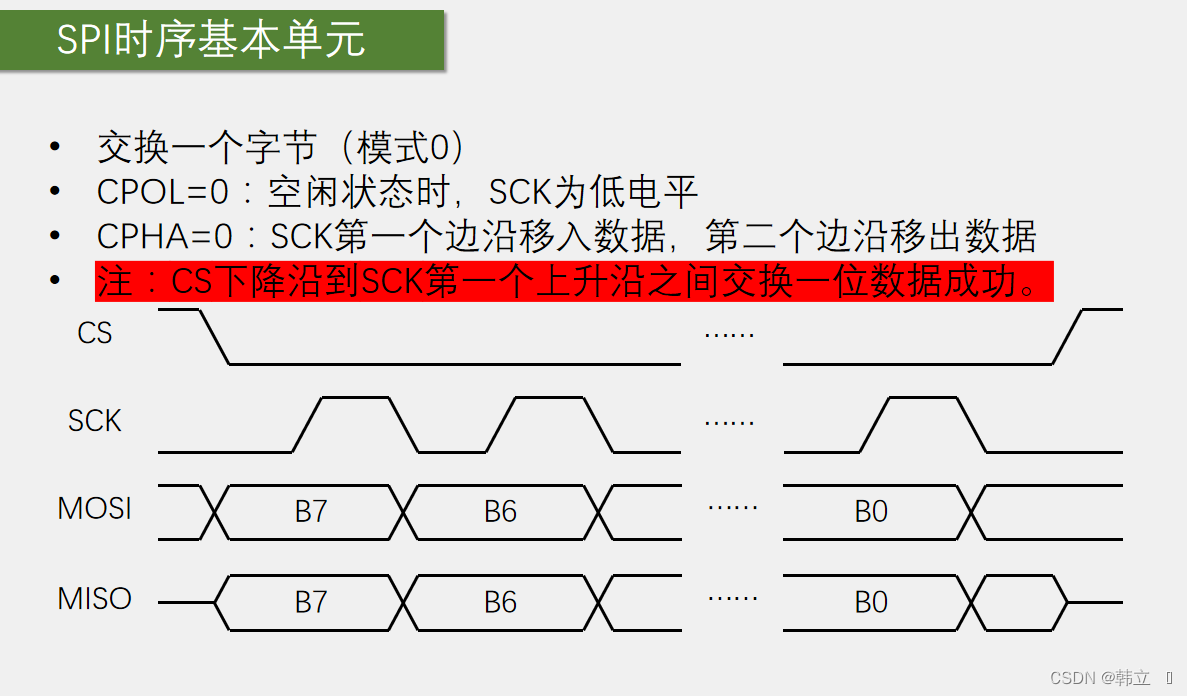

模式0(常用)

模式0的数据移出移入的时机会相位提前(上升沿读取数据,下降沿移出数据。在第0个边沿移出数据,在第1个边沿移入数据(采样数据))

模式1

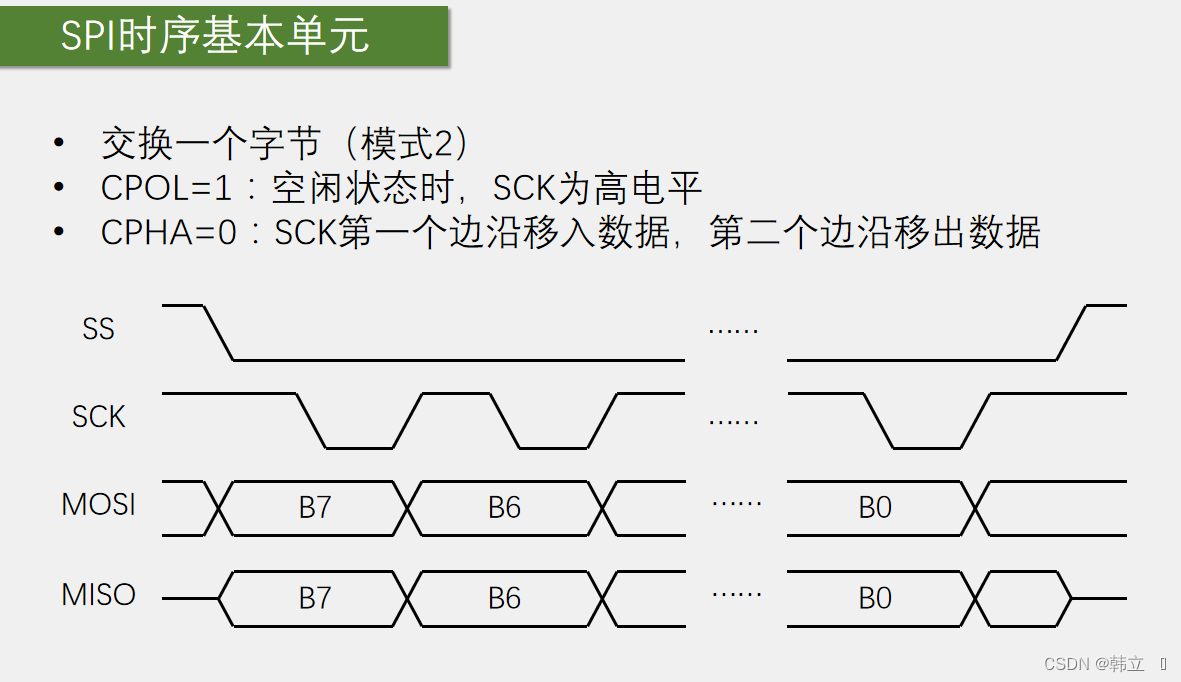

模式2

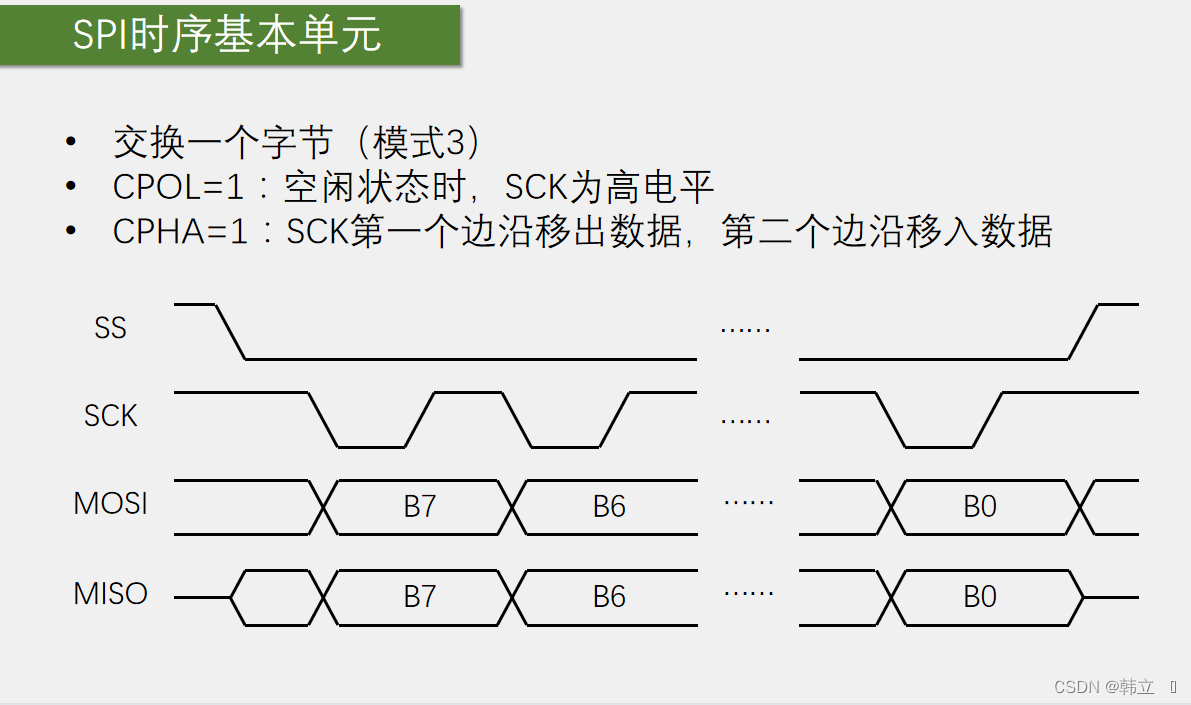

模式3

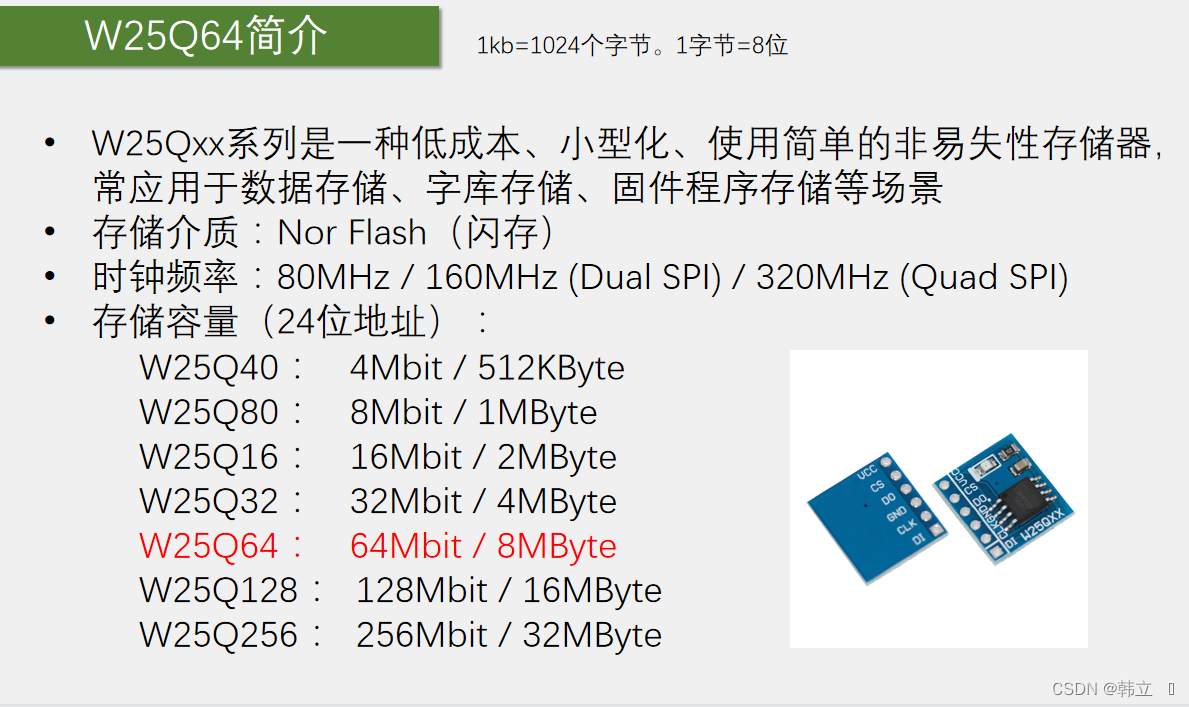

W2Q564芯片介绍:

存储器分为易失性存储器(RAM:内存)和非易失性存储器(ROM存储的数据是否是掉电不丢失)

易失性存储器一般包括SRAM、DRAM等

非易失性存储器一般包括E2PROM、Flash等

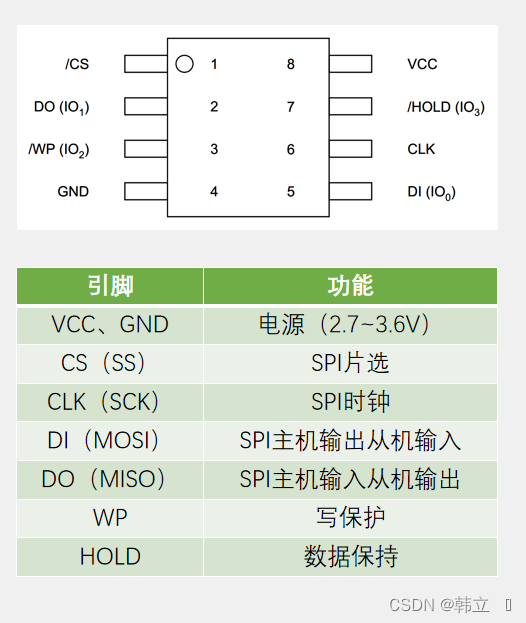

接口示意图和引脚功能:

W2Q564的存储原理图:

划分空间

首先,整个矩形空间里,是所有的存储器,存储器以字节为单位,每个字节都有唯一的地址,W25Q64的地址宽度是24位,3个字节,所以看到左下角,它的地址是00 00 00h,h代表16进制。之后的空间地址依次自增,指导最后的一个字节地址是7F FF FF h。为什么不是FF开头,因为24位地址,最大寻址范围是16MB。W25Q64只有8MB,只用到一半空间。

在整个空间里,我们以64kb为一个基本单元,把它划分为若干的块,有block1,2,3…

分的块数:8Mb / 64kb =( 8Mb / 1024 )/ 64kb = 128块

块内地址变化规律:在每一块内,它的地址变化范围就是低位的2个字节,每个块的起始地址是xx 00 00 结束是xx FF FF

块内地址:

起始:00 00 00 结束:00 FF FF

起始:1F 00 00 结束:1F FF FF

….

起始:7F 00 00 结束:7F FF FF

对每一块进行更细的划分,分为多个扇区Sector,在每个扇区以4kb为一个单元进行划分,16份。