目录

- 一、PCIE结构

- 1、层次结构

- 2、数据包

- TLP

- DLLP

- PCIE寄存器配置

- 1、基址寄存器的作用

- 2、基址寄存器的位置

- 三、PCIE读取数据

一、PCIE结构

1、层次结构

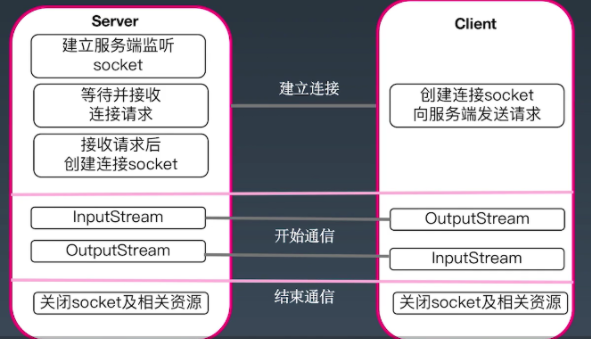

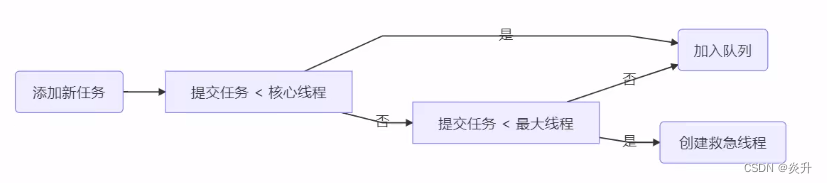

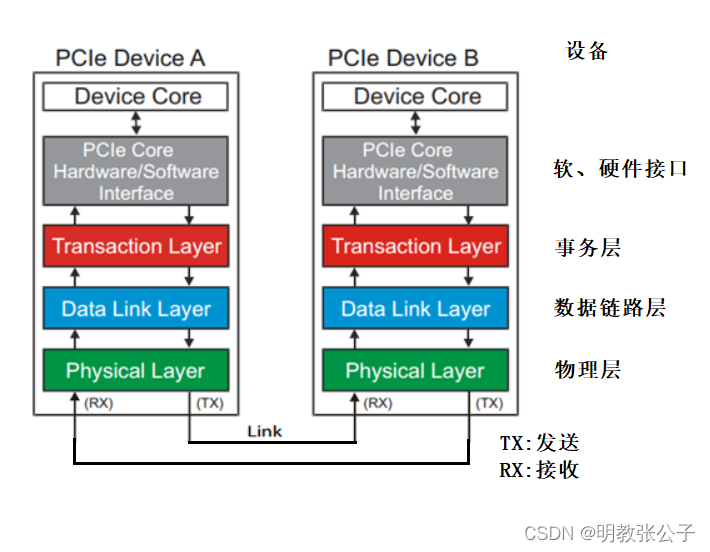

绝大多数的总线或者接口,都是采用分层实现的。PCIe也不例外,它的层次结构如下:

PCIe定义了下三层:

- 事务层(Transaction Layer)

- 数据链路层(Data Link Layer)

- 物理层(Physical Layer)

每层职能不同,且下层为上层服务。

分层设计优势:接口版本改动时,硬件设计改动的层数较少。

PCIe传输的数据从上到下,都是以packet的形式传输的,每个packet都是有其固定的格式的。

事务层的主要职责是创建(发送)或者解析(接收)TLP (Transaction Layer packet),流量控制,QoS,事务排序等。

数据链路层的主要职责是创建(发送)或者解析(接收)DLLP(Data Link Layer packet),Ack/Nak协议(链路层检错和纠错),流控,电源管理等。

物理层的主要职责是处理所有的Packet数据物理传输,发送端数据分发到各个Lane传输(stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Scramble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)去扰(De-scramble),以及8/10或者128/130编码解码,等等。

2、数据包

TLP

DLLP

PCIE寄存器配置

1、基址寄存器的作用

基址寄存器(Base Address Registers)就是 PCIe 协议提供的、用于向系统软件展示 PCIe 设备内部资源大小、资源类型和资源属性的机制。

每个 PCIe 设备内部都会有一部分资源需要提供给系统软件访问。与此同时,不同的 PCIe 设备可供系统软件访问的资源大小、资源类型也不一样。在计算机系统中,只有系统软件可以为 PCIe 设备内部的资源指定合适的地址,而 PCIe 设备能做的就是告诉系统软件该设备内部可访问的资源大小、资源类型和资源特性。

2、基址寄存器的位置

基址寄存器(Base Address Registers)位于 PCIe 设备配置空间(configuration space)的配置头(configuration header)中。PCIe 设备有两种类型的配置头,分别为 0 型配置头(Type 0 configuration header)和 1 型配置头(Type 1 configuration header)。在两种配置头中,基址寄存器的位置如下图所示:

从图中可以看出,0 型配置头(Type 0 configuration header)包含 6 个基址寄存器,而 1 型配置头(Type 1 configuration header)只包含 2 个基址寄存器。

PCIe 桥类型设备,即 PCIe Root Complex 和 PCIe Switch,包含 1 型配置头(Type 1 configuration header)。

PCIe 非桥类型设备,例如 PCIe Endpoint,包含 0 型配置头(Type 0 configuration header)。