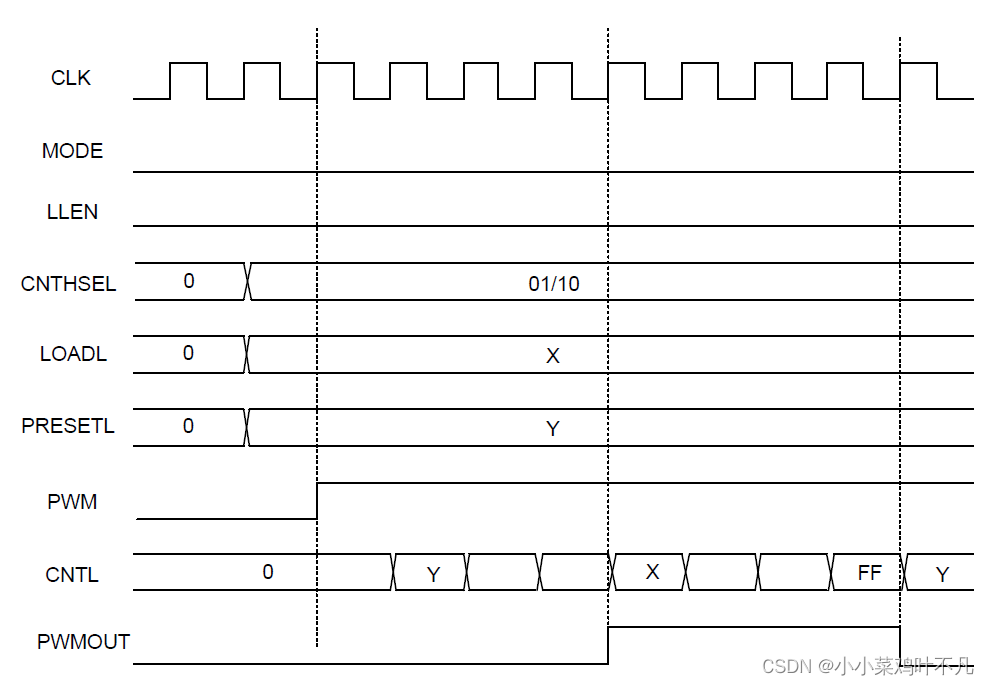

8bit PWM

PWM模式开启时,计数器与比较寄存器连续比较,当计数值小于比较寄存器,输出为低,当计数值大于等于比较寄存器,输出为高,并且保持到计数值等于重载寄存器,然后计数器回到0开始重新计数,并将输出恢复为低。

PWM周期由重载寄存器控制,占空比由比较寄存器控制。理论上要求比较寄存器值小于重载寄存器。如果比较寄存器大于等于重载寄存器,则输出没有高电平信号。示意图如下:

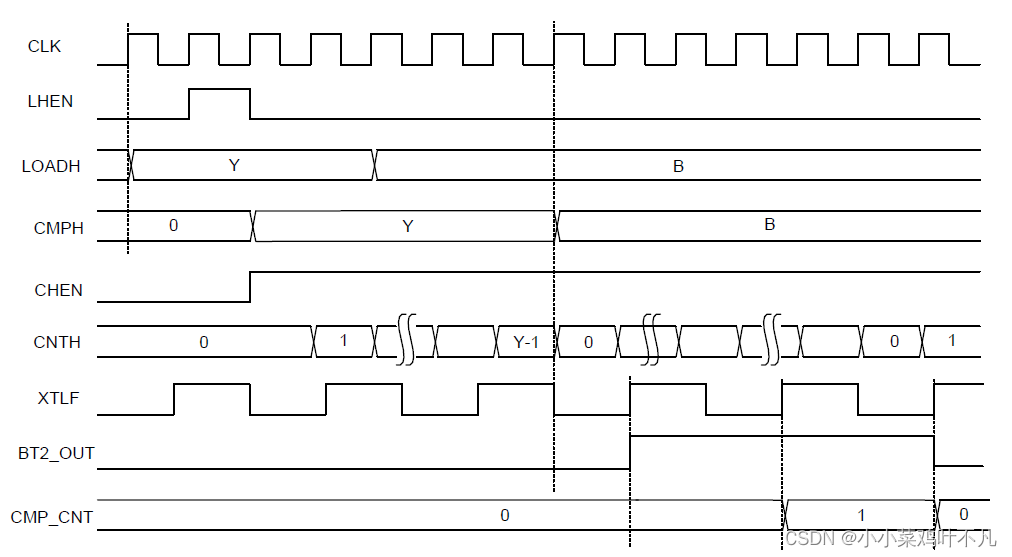

脉冲输出

当设置了BT_OUT输出脉冲宽度寄存器后,模块可以输出相应的脉冲宽度。当计数器匹配到来后的第一个32768 时钟上升沿开始触发脉冲输出, 计数时钟为32768Hz 。输出脉冲宽度=([OUTCNTH,OUTCNTL]+1)/32768秒。以高8BIT计数器匹配为例,[OUTCNTH,OUTCNTL]=1,波形如下:LOADH为高位加载寄存器;LHEN是高位加载使能寄存器,用来把高位加载寄存器的值加载进高位比较寄存器里;CMPH为高位比较寄存器;CHEN高位是计数器使能信号;CNTH是高位计数器;XTLF是32768HZ时钟信号;CMP_CNT是以32768HZ为计数周期的脉冲宽度内部计数器,当它计数到等于[OUTCNTH,OUTCNTL]的值时回到0;BT_OUT为输出脉冲信号。

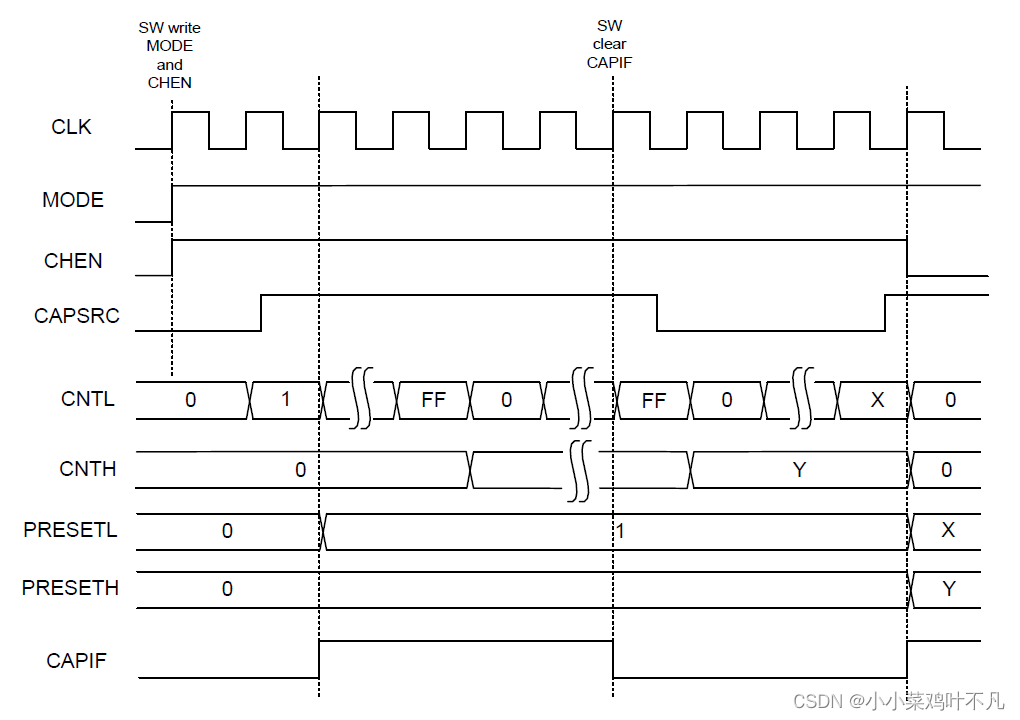

Toggle 输出

当设置了输出BT_OUT控制寄存器的OUTMOD位为1后,当比较匹配后模块可以输出与之前相反的电平(Toggle)。以高8位的计数器为例,示意波形如下图。

工作模式(3)

news2026/2/11 5:07:21

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/557499.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

【三维激光扫描】实验05:点云数据预处理操作

SiScan软件可以对三维激光扫描的点云数据进行一些列的预处理操作,如:粗差剔除、点云抽稀、点云分割、调整水平面、删除分割面等等。 粗差剔除剔除粗差点抽稀抽稀数据点云分割根据点云的三维特征进行分组调整水平面根据三个点来调整水平面分割面水平纠正根据分割面进行水平纠正…

小心你的 OpenAI Key 被盗!

公众号关注 “GitHubDaily” 设为 “星标”,每天带你逛 GitHub! 今年随着 ChatGPT 发布,其强悍的能力也让 GPT-3.5/4 成为炙手可热的大语言模型,使得不少 AI 应用接入了 OpenAI 接口。当用户使用这些应用时,经常需要填…

Python自动化办公对每个子文件夹的Excel表加个表头(Excel不同名)(上篇)

点击上方“Python爬虫与数据挖掘”,进行关注 回复“书籍”即可获赠Python从入门到进阶共10本电子书 今 日 鸡 汤 含情凝睇谢君王,一别音容两渺茫。 大家好,我是皮皮。 一、前言 上一篇文章,我们抛出了一个问题,这篇文章…

chatgpt赋能Python-python_fetchone

Python fetchone方法简介

在Python编程领域中,fetchone()是一个经常使用的方法。fetchone()方法用于从数据库中获取单个结果,并将结果存储在变量中。本文将介绍fetchone()方法的详细信息,并探讨如何在Python中使用该方法。

什么是fetchone方…

chatgpt赋能Python-python_chariot

Python Chariot:一款强大的Python IDE

Python Chariot是一款强大的Python IDE,它的特点是简单易用,功能齐全。该IDE适用于各种Python编程任务,无论是编写小型脚本还是大型项目。在本文中,我们将深入介绍Python Chario…

Windows本地快速搭建SFTP服务共享文件 - 外网访问【端口映射】

文章目录 1. 搭建SFTP服务器1.1 下载 freesshd服务器软件1.3 启动SFTP服务1.4 添加用户1.5 保存所有配置 2 安装SFTP客户端FileZilla测试2.1 配置一个本地SFTP站点2.2 内网连接测试成功 3 使用cpolar内网穿透3.1 创建SFTP隧道3.2 查看在线隧道列表 4. 使用SFTP客户端࿰…

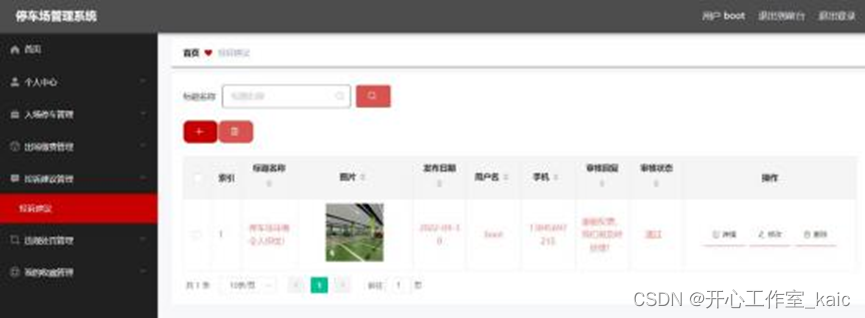

基于SpringBoot的停车位智能管理系统的设计与实现_kaic

摘 要 随着经济与交通事业的飞速发展,汽车的保有量呈现上升趋势,公共停车位 智能化在信息时代显得尤为重要。面对有限的公共停车位与上升的汽车保有量, 通过合理利用公共停车位来提高车位的利用率是大势所趋。 基于上述背景,本论…

为生信写的Python简明教程 | 视频4

开源生信 Python教程 生信专用简明 Python 文字和视频教程 源码在:https://github.com/Tong-Chen/Bioinfo_course_python 目录 背景介绍 编程开篇为什么学习Python如何安装Python如何运行Python命令和脚本使用什么编辑器写Python脚本Python程序事例Python基本语法 数…

基于 Log 的通用增量 Checkpoint 在美团的进展

摘要:本文整理自美团计算引擎工程师王非凡,在 Flink Forward Asia 2022 核心技术专场的分享。本篇内容主要分为四个部分: 1. Log based Checkpoint 基本原理介绍 2. 美团应用场景及测试效果 3. Changelog Restore 性能优化 4. Changelog 存储…

49天精通Java,第35天,Java初始化、构造器、对象创建的过程

目录 一、初始化与清理二、用构造器保证初始化1、无参构造器2、有参构造器 三、成员初始化1、显式初始化2、隐式初始化3、初始化块 四、对象创建的过程 大家好,我是哪吒。

🏆本文收录于,49天精通Java从入门到就业。

全网最细Java零基础手把…

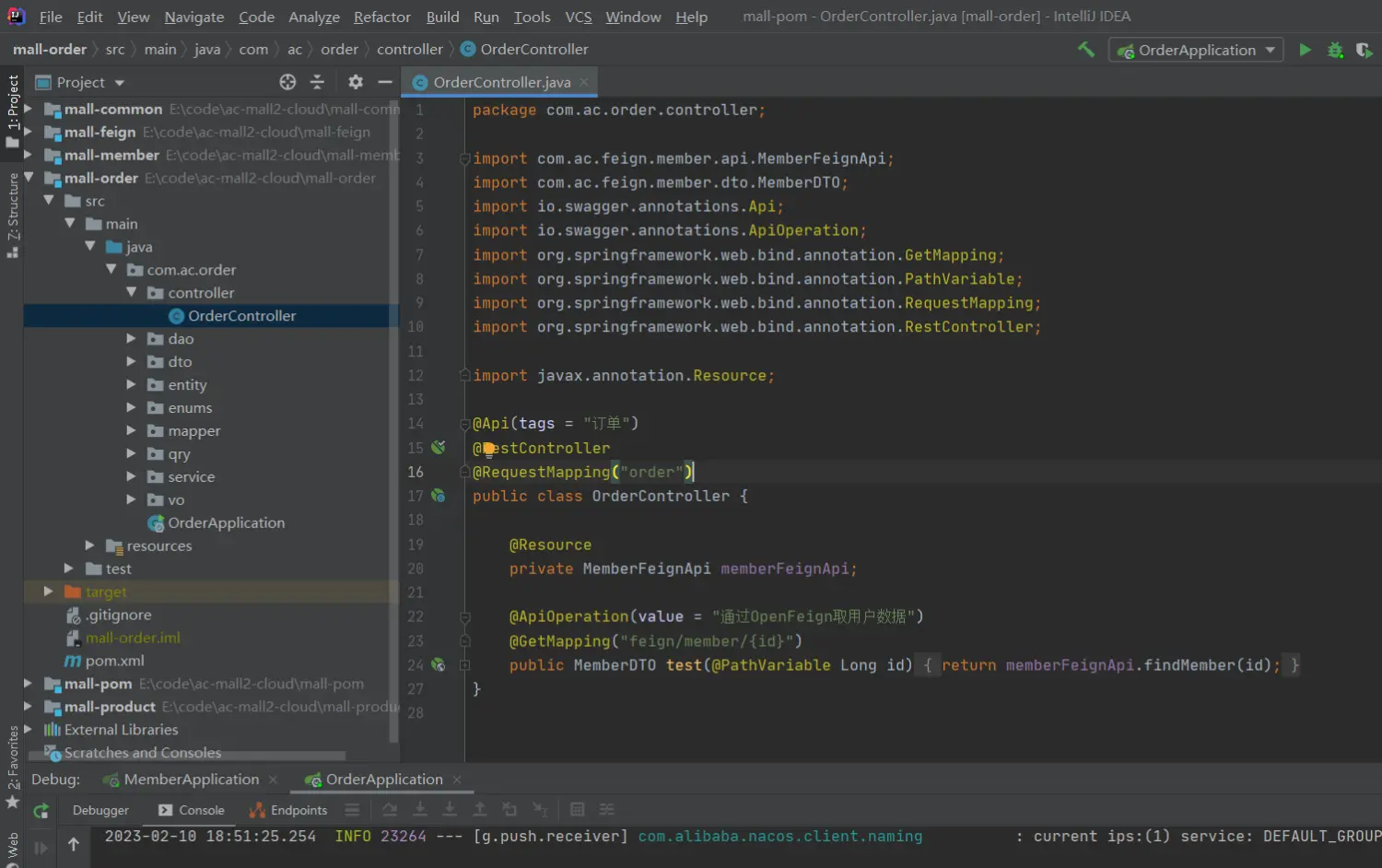

微服务开发系列 第三篇:OpenFeign

总概

A、技术栈

开发语言:Java 1.8数据库:MySQL、Redis、MongoDB、Elasticsearch微服务框架:Spring Cloud Alibaba微服务网关:Spring Cloud Gateway服务注册和配置中心:Nacos分布式事务:Seata链路追踪框架…

多维时序 | MATLAB实现GA-GRU遗传算法优化门控循环单元多变量时间序列预测

多维时序 | MATLAB实现GA-GRU遗传算法优化门控循环单元多变量时间序列预测 目录 多维时序 | MATLAB实现GA-GRU遗传算法优化门控循环单元多变量时间序列预测效果一览基本介绍程序设计参考资料 效果一览 基本介绍 多维时序 | MATLAB实现GA-GRU遗传算法优化门控循环单元多变量时间…

OSPF 邻居关系 附实验

实验目的

通过对 OSPF 邻居关系建立进行相关的实验,从中学习到如何调整 OSPF Hello 包间隔,Dead 间隔,以及影响 OSPF 邻居建立的因素,例如 RID,MTU,OSPF 认证。并且将总结 OSPF在不同网络类型上的不同行为…

FPGA纯verilog实现CameraLink视频接收和发送,附带工程源码和技术支持

目录 1、前言2、CameraLink协议基础3、目前我已有的CameraLink收发工程4、设计方案5、CameraLink解码模块详解6、CameraLink编码模块详解7、vivado工程详解8、上板调试验证9、福利:工程代码的获取 1、前言

FPGA实现CameraLink视频编解码目前有两种方案:…

用streamlit,几行代码就可以拥有漂亮图表!

大家注意:因为微信最近又改了推送机制,经常有小伙伴说错过了之前被删的文章,比如前阵子冒着风险写的爬虫,再比如一些限时福利,错过了就是错过了。 所以建议大家加个星标,就能第一时间收到推送。ὄ…

FastAPI 和 fastapi-amis-admin:强大而可扩展的后台管理解决方案!

大家好,我是安果! 我们都知道 Django 生态丰富,功能强大,适用于中、大型项目,并且自带了后台管理系统;而 FastAPI 更适用于构建高性能的 API,后台管理系统需要另外开发 本篇文章将介绍 FastAPI…

完犊子!原单位的离职证明丢了,下周要入职了,用AI做一个行不行?

弄丢了离职证明怎么办? 一位网友哀叹: 完犊子!原单位的离职证明丢了,下周要入职了,现在怎么办?用AI做一个行不行? 有相同经历的网友安慰他,离职证明没了没事,新公司会要求…

打卡智能中国(五):博士都去哪儿了?

《打卡智能中国》系列更新了几期,有读者表示,很爱看这类接地气的真实故事,也有读者反映,不是电工,就是文员、农民、治沙人,人工智能不是高精尖学科吗?那些学历很高的博士都去哪儿了?…