1.场景

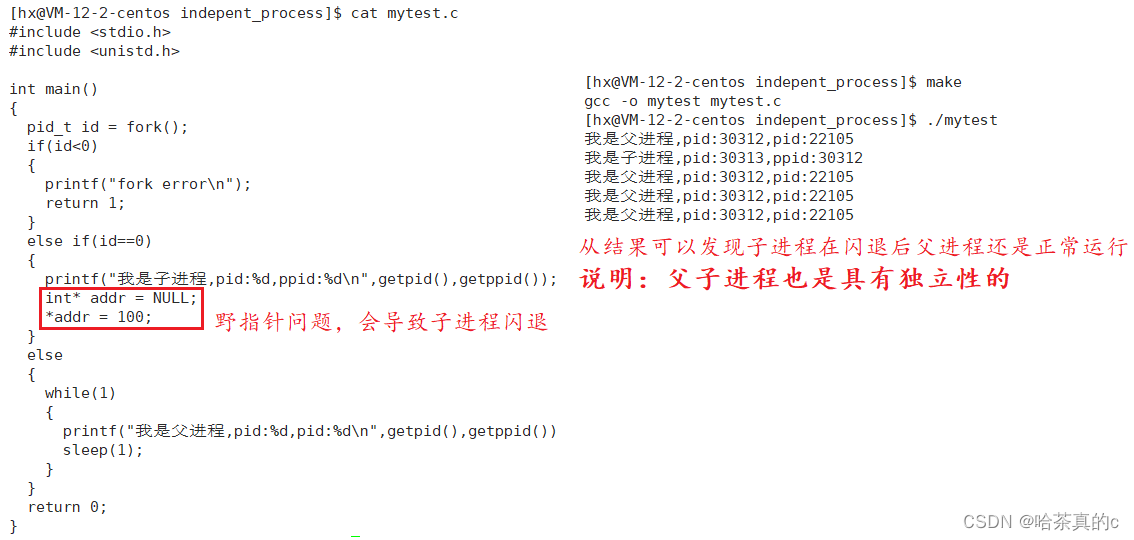

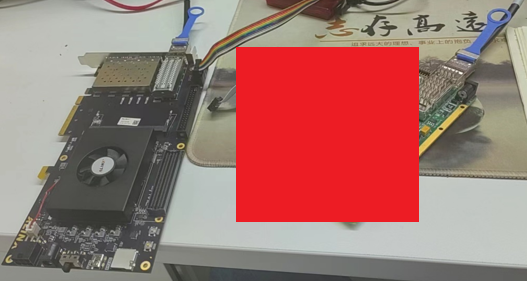

从发送端(一块硬件板卡)通过40G QSFP接光纤连接到接收端(另一块硬件板卡),实现从数据的发送与接收。连接如下,官方的example design即可实现这一功能,因此直接使用官方的代码即可。

2.硬件环境

1.使用两块板卡,一块是Alinx7k325t开发板,一块是自己的板卡,二者的FPGA芯片都是xc7k325tffg900-2

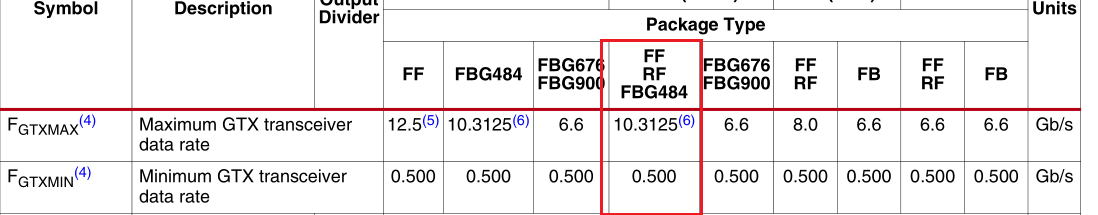

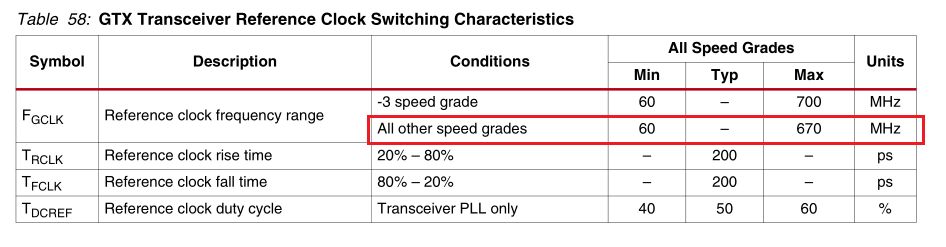

2.确认GTX收发器速度

截图出自《Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics》

3.参考时钟范围

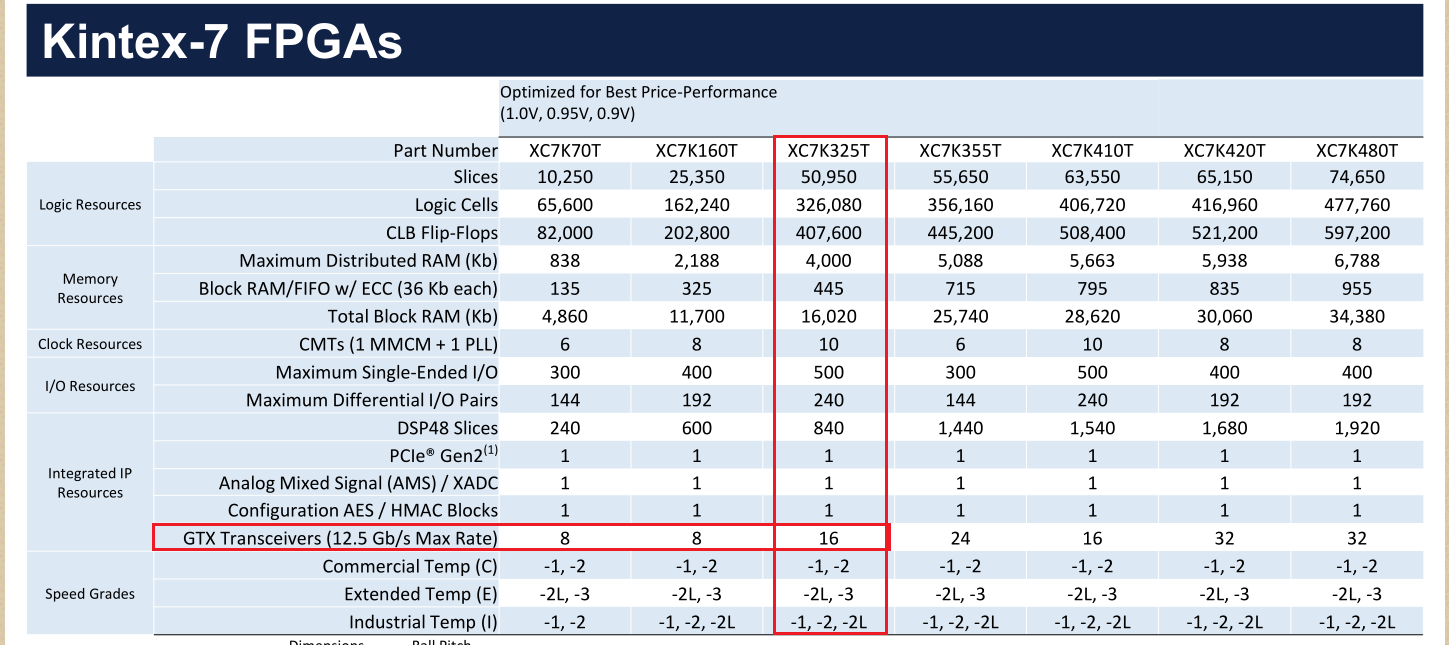

4.确认芯片GTX资源

截图出自《7 Series Product Selection Guide》

5. 确认开发板GT连接情况及参考时钟

截图出自开发板使用手册

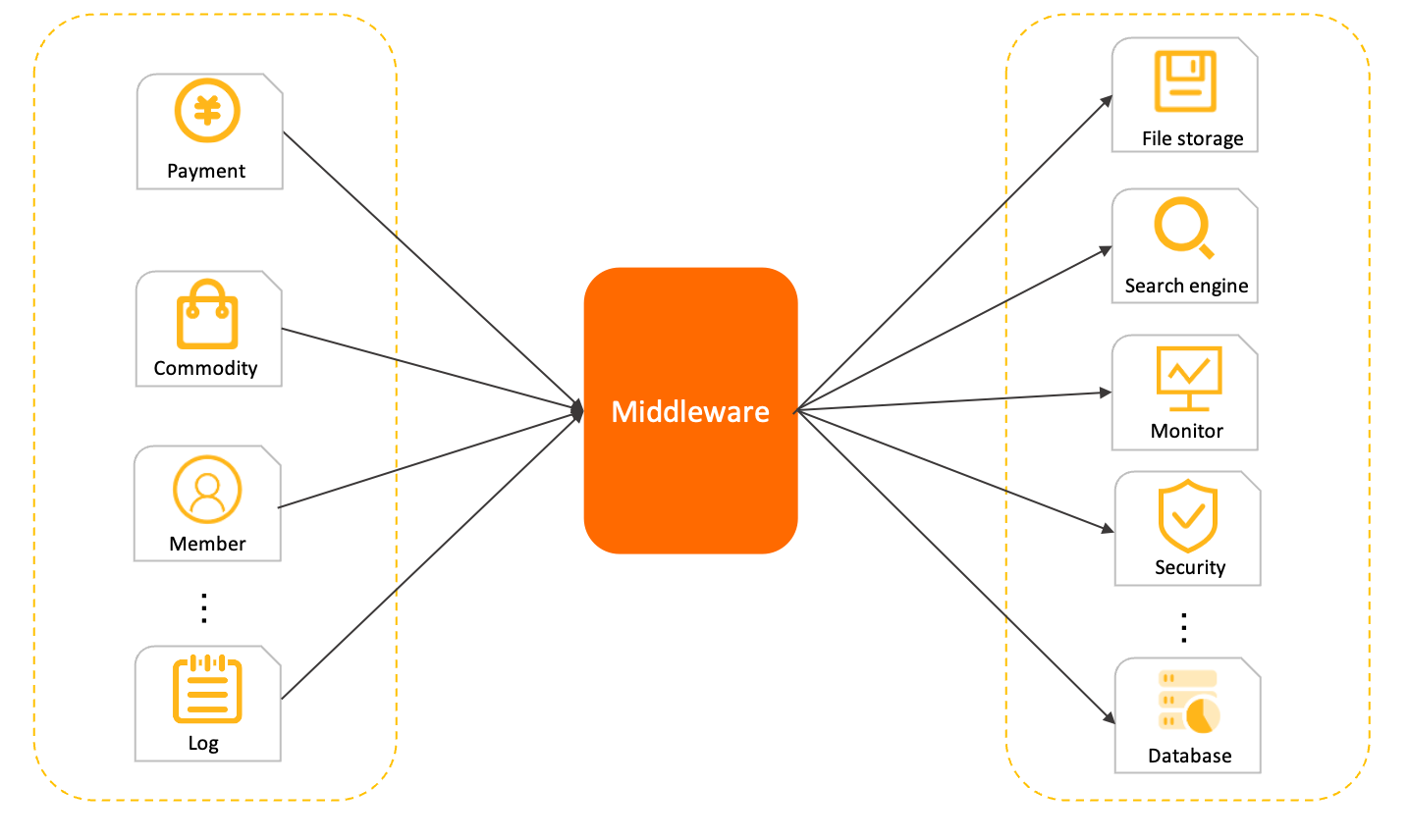

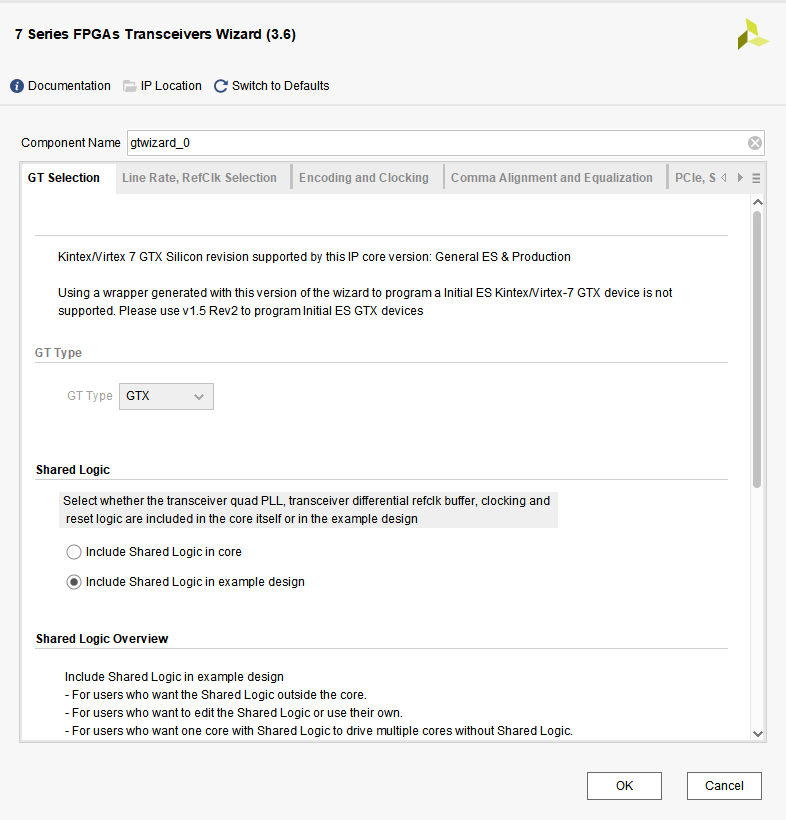

3 IP核配置

①图中share logic指共享逻辑是包含在内核本身还是示例设计( example design)中,把共享逻辑包含在内核本身的 IP 称为主核,内核中不包含共享逻辑的 IP 称为从核。从核与主核的区别是:我们可以在 Example Design 中修改共享逻辑。这里选择的是主核。此处共享逻辑指的是,IP涉及的多个时钟的来源都可以有几个地方,通过多路选择器选择,共享逻辑就包含了这些多路器的配置。

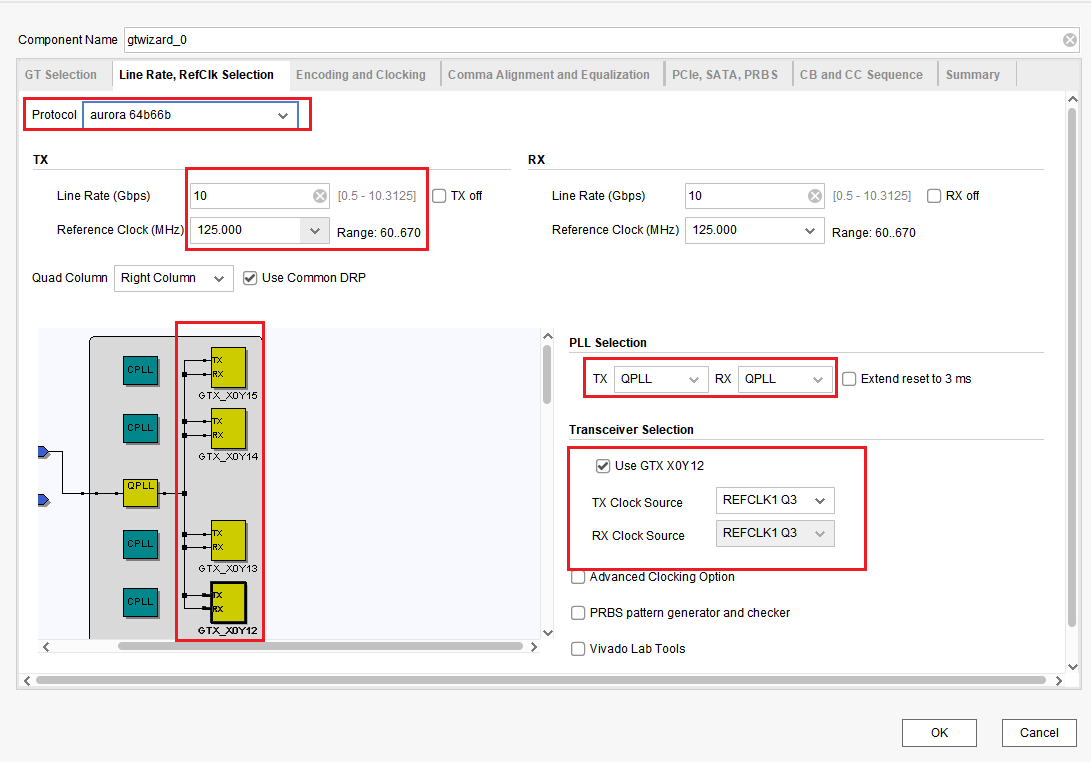

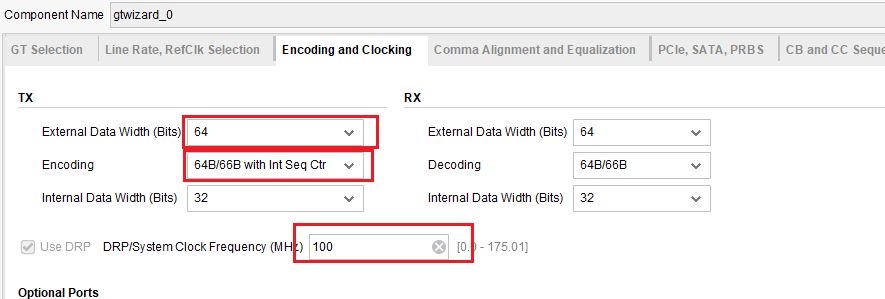

②K7的收发器为GTX,选择编码协议为aurora 64b66b。支持aurora 线速率选择在芯片支持范围内结合自身应用场景,此处选择10G;参考时钟的选择看具体的硬件设计,这里选择125; PLL不可选,只能是QPLL;X0Y14等代表收发器的位置,与原理图中的设计应该是一致的,这里使能四个收发器,总的速率为4*10G=40Gbps;Clock Source选择REFCLK1 Q3,这是与Quad3对应的。另外需要说明硬件板卡中GT连接在了Bank118就对应的是Quad3(结合硬件板卡的实际情况),Bank115对应Quad0。勾选这里的Use Common DRP,这样四个通道使用一个DRP接口。

③该页中主要关注以下配置,其余功能暂时不用,或默认或取消勾选。一是外部数据位宽,一是编码方式,还有DPR设置为100MHz(可直接连接外部时钟,也可以从时钟IP分频)。

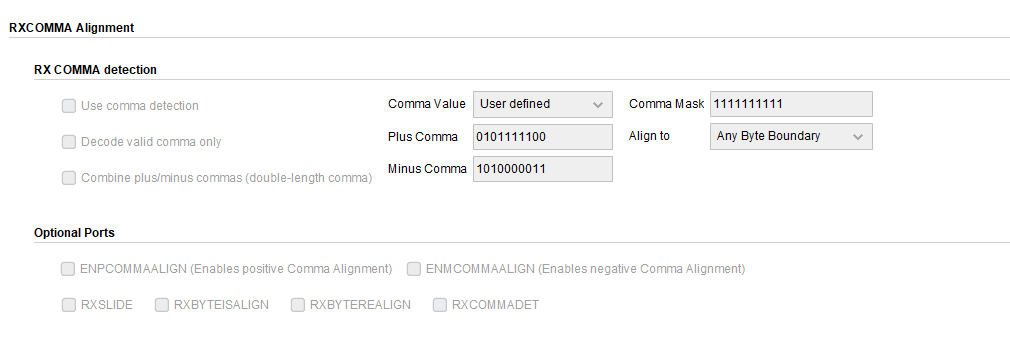

④该页保持默认配置,由于64/66B编码采用的是加扰的方式处理数据,所以在默认情况下,comma选项即为不可选,这是与加扰不同的处理方式。此页以后的内容全部保持默认。

4源码简介

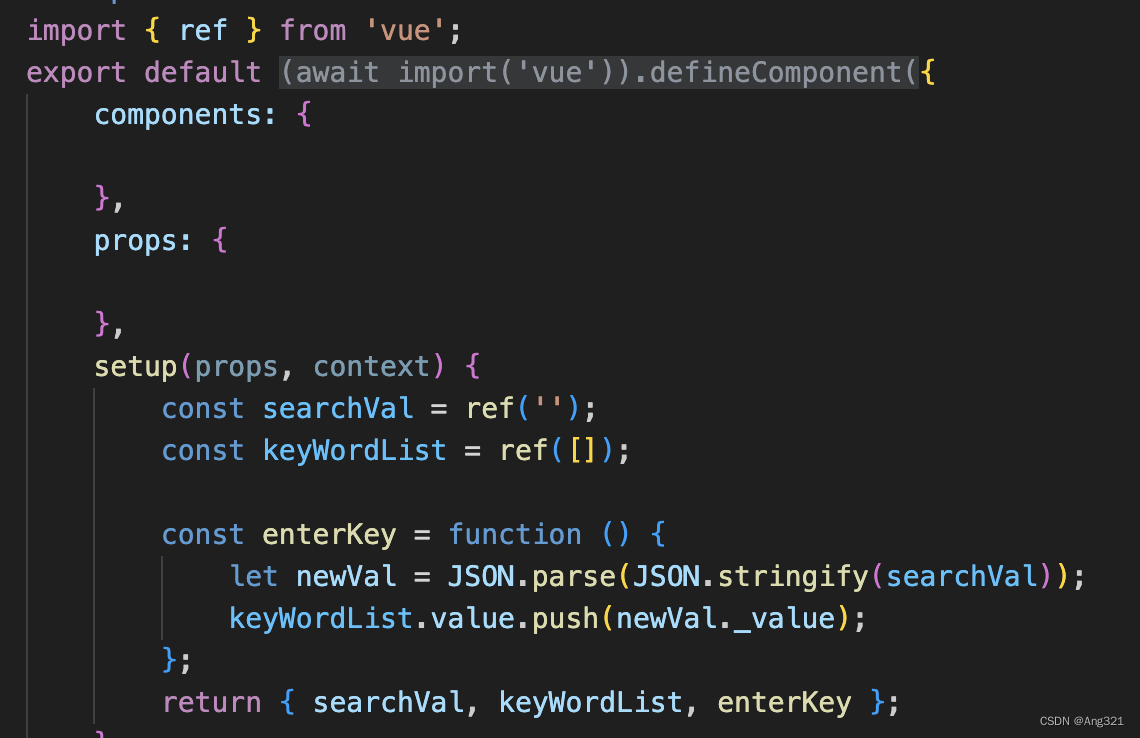

IP配置好之后,打开example design。可以清楚的看到40G光口通信与10G之间的区别便是40G就是10G x 4。各个通道并行运行,并且各控制信号全部独立工作,下面介绍example design的组成,便于基于此来传输自定义数据。

- gtwizard_0_support.v文件及其例化文件与其他基于GT串行收发器的应用一样,完成GT IP的例化,连接必要的用户接口信号包括发送端接口和接收端接口,选择各时钟来源,复位逻辑等。

- gtwizard_0_gt_frame_gen.v文件有四个,分别对应四个光纤收发通道,该文件根据TXDATAVALID_IN信号将ROM中递增的数据转移到发送信号上,并根据数据内容产生TXCTRL_OUT信号,用来指示同步字段的编码情况。

- gtwizard_0_scrambler.v文件用来依据DATA_VALID_IN信号将frame_gen文件生成的数据进行加扰处理,这是64B/66B编码方式要求的。加扰后的数据转发到support模块处理发送。

- gtwizard_0_block_sync_sm.v 64B/66B编码模式下特有的对齐模块。对接收的gt0_rxheader_i头进行查找,根据接收到的RXHEADER_IN信号生成RXGEARBOXSLIP_OUT进入IP核进行数据对齐。

- gtwizard_0_descrambler.v 根据block模块产生的BLOCKSYNC_OUT信号作为复位信号,将接收到的数据SCRAMBLED_DATA_IN依据数据有效信号DATA_VALID_IN进行解扰,生成的数据UNSCRAMBLED_DATA_OUT转发到check模块。

- gtwizard_0_gt_frame_check.v文件根据收到的解扰后的数据依据rom表中的数据进行查错。

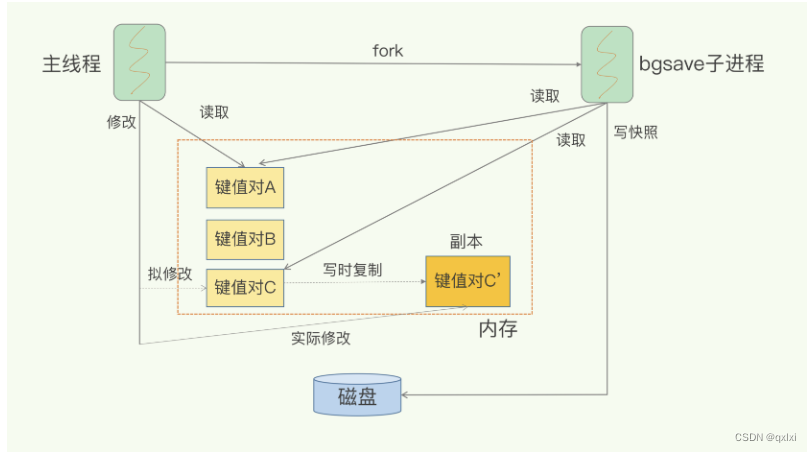

将support和GT IP核看成一个整体。数据的发送流程,根据gt3_txgearboxready_i信号的指示,产生发送数据有效信号,frame_gen模块依据该信号遍历ROM表的数据,并根据数据中的ctrl指示产生TXCTRL_OUT信号指示同步字节编码是“01”还是“10”,送到support模块。与此同时,加扰模块也根据数据有效信号对数据进行加扰,将产生的数据送到support模块完成数据发送流程。

数据的接收流程是:Block模块一直根据接收到的gt0_rxheader_i信号产生gt0_rxgearboxslip_i信号用于数据对齐,与此同时,解扰模块根据接收到的gt0_rxdatavalid_i及gt0_rxdata_i对数据解扰成gt0_unscrambled_data_i在传递到check模块进行检查便完成了数据接收的流程。

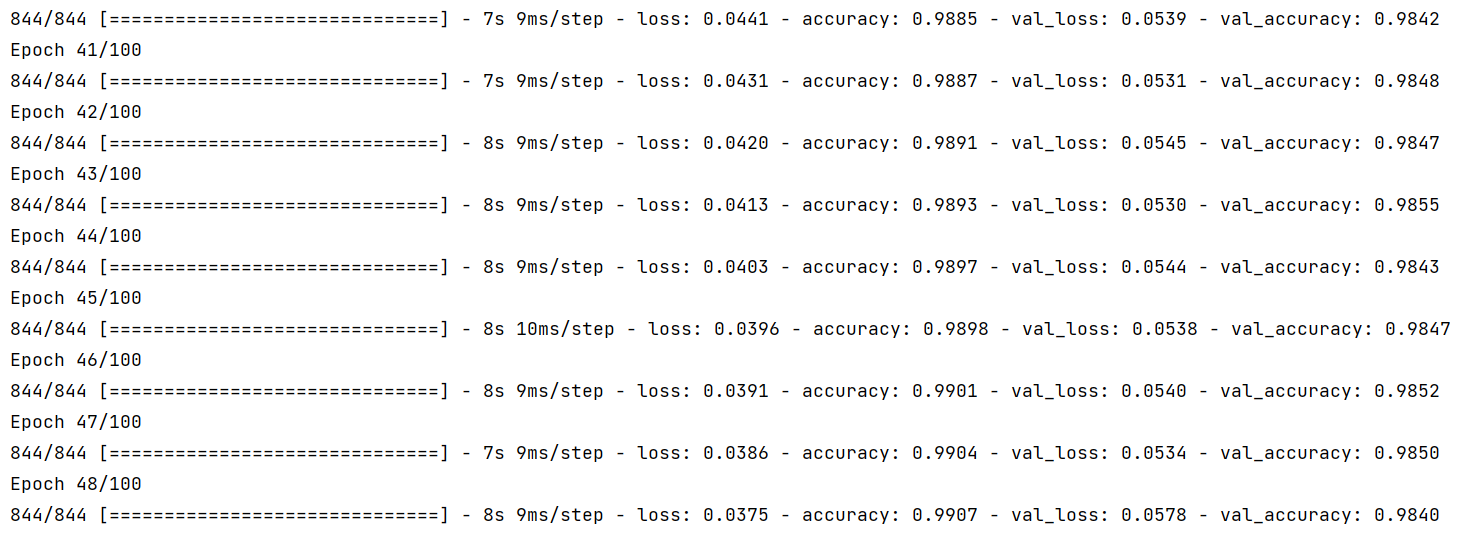

5代码修改与效果

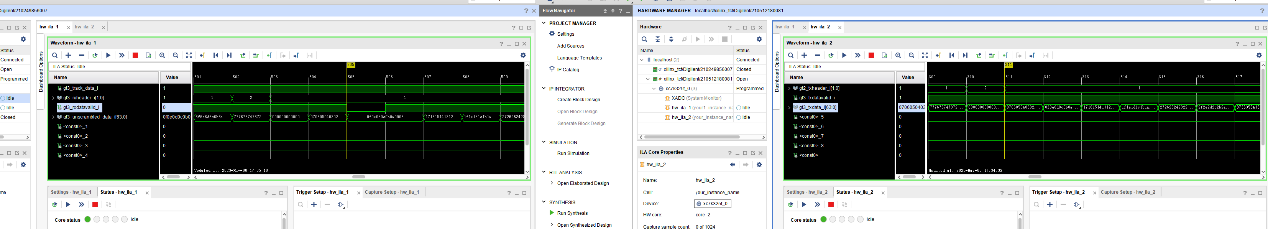

部分代码与硬件的组成有关,需要注意以下部分。①修改DRP_CLK_IN_P 来源,添加时钟生成IP,输入200差分,转成100单端,然后取消掉IBUFDS,只使用BUFG即可。②添加通道的ILA。③添加约束文件(数据发送端,开发板),修改Q3_CLK1_GTREFCLK_PAD_P_IN连接到C8, N连接到C7;修改DRP_CLK_IN_P连接到AE10 ,N连接到AF10。屏蔽掉信号 TRACK_DATA_OUT的输出。这个信号为高电平表示数据通道就绪,可以进行数据传输了。④数据接收端,自研板卡端,QSFP0_CLK_P –C8 QSFP0_CLK_N—C7 ;SYSCLK_P – AD12 SYSCLK_N—AD11 ;156.25MHz 参考时钟;GT也是用的Bank118的收发器。

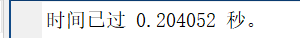

效果如下图所示。