学习路线

《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。不看书也能写出个三段式状态机就可以进入下一阶段了。

此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,

可以选Altera的cyclone IV系列,或者Xilinx的Spantan 6。

还没掌握HDL之前千万不要买开发板,因为你买回来也没用。这里你没必要每次编译通过就下载代码,咱们用modelsim仿真(此外还有QuestaSim、NC verilog、Diamond的Active-HDL、VCS、Debussy/Verdi等仿真工具),如果仿真都不能通过那就不用下载了,肯定不行的。

在这里先掌握简单的testbench就可以了。推荐的教材是《WRITING TESTBENCHES Functional Verification of HDL Models》。

作者:Potato爱学习

链接:https://www.zhihu.com/question/381684248/answer/2447062566

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

3 、 掌握设计方法和设计原则

你可能发现你综合出来的电路尽管没错,但有很多警告。这个时候,你得学会同步设计原则、优化电路,是速度优先还是面积优先,时钟树应该怎样设计,怎样同步两个异频时钟等等。

推荐的教材是《FPGA权威指南》、《IP核芯志-数字逻辑设计思想》、《Altera FPGA/CPLD设计》第二版的基础篇和高级篇两本。学会加快编译速度(增量式编译、LogicLock),静态时序分析(timequest),嵌入式逻辑分析仪(signaltap)就算是通关了。如果有不懂的地方可以暂时跳过,因为这部分还需要足量的实践,才能有较深刻的理解。

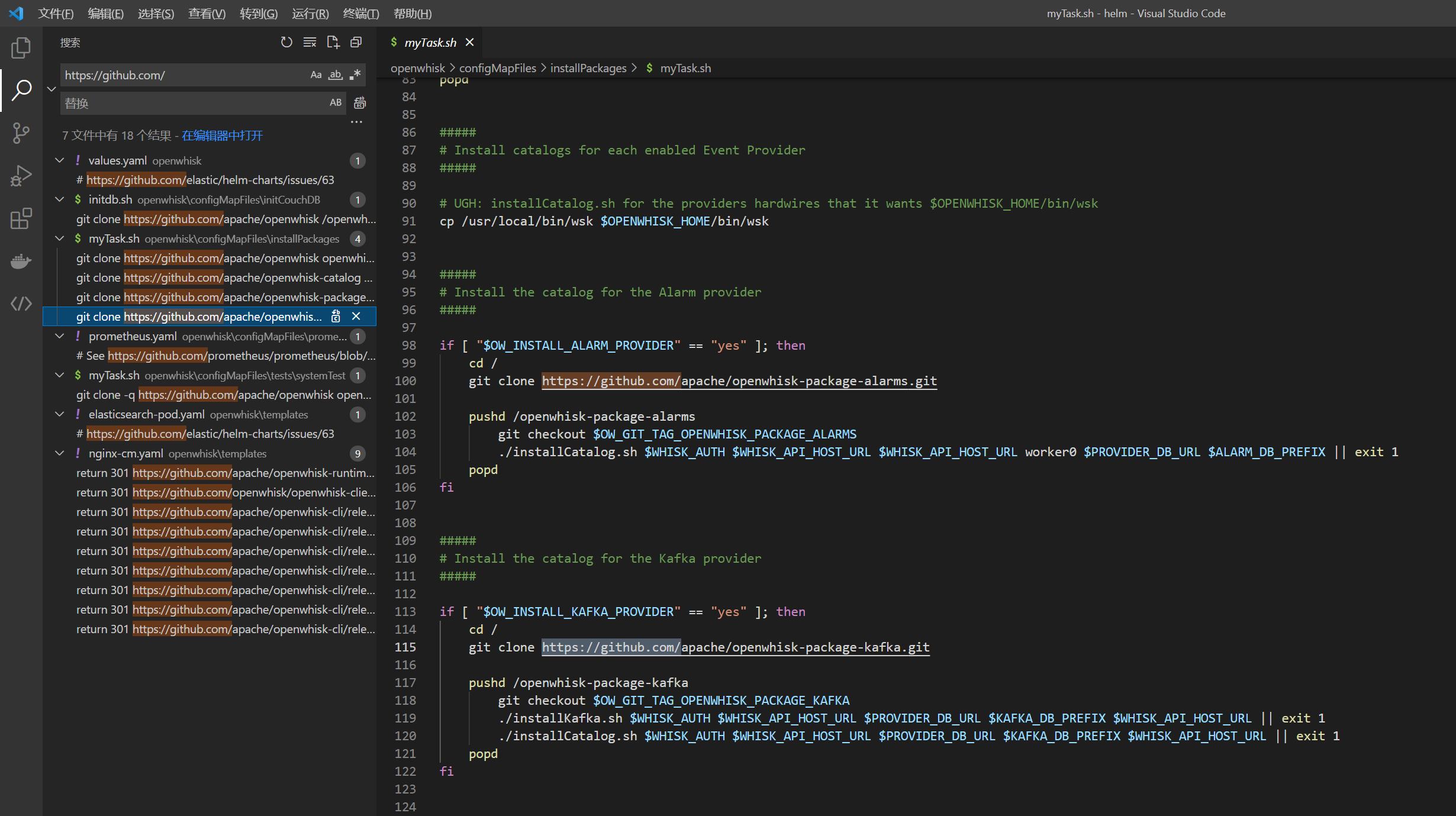

4、 学会提高开发效率

因为Quartus和ISE的编辑器功能太弱,影响了开发效率。所以建议使用Sublime text编辑器中代码片段的功能,以减少重复性劳动。Modelsim也是常用的仿真工具,学会TCL/TK以编写适合自己的DO文件,使得仿真变得自动化,推荐的教材是《TCL/TK入门经典》。

你可能会手动备份代码,但是专业人士都是用版本控制器的,所以,为了提高工作效率,必须掌握GIT。

文件比较器Beyond Compare也是个比较常用的工具。此外,你也可以使用System Verilog来替代testbench,这样效率会更高一些。如果你是做IC验证的,就必须掌握System Verilog和验证方法学(UVM)。推荐的教材是《Writing Testbenches using SystemVerilog》、《The UVM Primer》、《System Verilog1800-2012语法手册》。

掌握了TCL/TK之后,可以学习虚拟Jtag(ISE也有类似的工具)制作属于自己的调试工具,此外,有时间的话,最好再学个python。脚本,意味着一劳永逸。

作者:Potato爱学习

链接:https://www.zhihu.com/question/381684248/answer/2447062566

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

1、夏宇闻的verilog设计

2、其他资料多逛FPGA论坛,资源很丰富

作者:徐墨潇

链接:https://www.zhihu.com/question/409150023/answer/1364365658

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

市面上跟fpga相关岗位分为很多路线,很多和业务挂钩的知识点就不做分析了,主要聊聊通用的。

就我知道的而言有以下几种:

FPGA 逻辑工程师

简单的说就是会写 HDL代码的这种,比较初级,掌握几门工具,会写写hdl代码,但是想把代码写好,设计规范还是有非常多的设计技巧的。

学习路线:

systemverilog/verilog ->testbench ->总线规范->资源优化->工具的使用->约束技巧->Debug技巧->联调手段 等等基本就这些。

FPGA 高速接口工程师

在 逻辑工程师 的基础上需要熟悉 Serdes/Transceiver 的硬件知识,以及FPGA中的设计使用方法,以及调试技巧。最重要的就是要熟悉了解 所需要用到的 链路层/传输层的协议,常见的Ethernet/SATA/Hdmi/Mipi/Pcie 等等等等,有的会提供完整的IP,有的则需要自己设计协议。

学习路线:

逻辑工程师的所有 -> Serdes/Transceiver 的相关知识 -> 高速协议 ->异常分析

FPGA 算法工程师

图像/音视频处理算法,深度学习算法,视频流压缩算法等等等等,涉及到非标硬件加速的各类型算法,都有fpga的参与。

学习路线:

算法理论-> matlab -> python ->c/c++ ->HDL移植

FPGA 嵌入式工程师

以前的普通软核,类似单片机,到现在的集成硬核 arm啥的,这部分知识点非常广。

学习路线:

c/c++ 编程 -> rtos编程-> linux编程-> 嵌入式软件方案涉及等等

芯片验证工程师

大部分IC涉及厂商有一个团队会前期在fpga上对芯片进行功能验证。

这部分知识点我不熟悉了,猜想主要和移植,仿真有关系吧。

明德扬系统学习

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-OZ7H0ElF-1669871952109)(https://raw.githubusercontent.com/zianmen/typora_img/master/images202211221502582.png)]

FPGA的线下培训哪家做的比较好?

一叶知秋

至芯总体来说价格偏贵,对于没收入的在校生或毕业生,确实吃不消。明德扬相对来说价钱低,可以考虑下,看性价比。v3好像是以前至芯的,现在分了,应该跟至芯差不多。

发布于 2018-05-07 11:00

后综合的工作,基本:时钟部分,时钟树生成,跨时钟域的版图优化;功耗设计,像电源布局,功耗分析,低功耗设计,power gating & clock gating;PR画版图,版图lvs检查,drc检查,gds生成;配合前端做时序分析,post pr时序分析,pr时序修正,PR NETLIST生成给前端仿真;其它工作,dft设计,信号完整性分析等等。

AMD,海康,中兴,小米,芯动,艾为,普冉半导体,信芯微等公司offer的

大厂offer:海思,AMD,汇顶,展讯,联发科,中兴微电子,芯原,全志,海康,晶晨,乐鑫,瑞芯微,国科微,ARM China, …

Verilog语言(比如Michael, D.Cilette的《Verilog HDL高级数字设计》或夏宇闻老师的《Verilog数字系统设计教程》);

还需要理解On-Chip-Bus的基本知识与一个数字系统的基本结构,建议学习理解:AMBA总线,含:APB/AHB/AXI。由于ARM在数字IP领域的领导低位,AMBA总线事实上已经成为数字IC的通用总线结构,必学。

这个推荐哪本书呢

2021-08-30

回复2

SiliconThink

作者

主要看ARM出的协议。B站有大致讲解:

《On-Chip-Bus》:DDR/Cache原理,APB/AHB/AXI,bus效率分析与提升。

bilibili.com/video/BV1p

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-YX93Z6vI-1669871952110)(https://raw.githubusercontent.com/zianmen/typora_img/master/images202211301032067.png)]

作者:温戈

链接:https://www.zhihu.com/question/283162522/answer/1727111241

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

薪资

从薪资来看,IC设计和验证基本相同。

其实这一点从各公司开出的薪资就可以看出来。尤其对于大公司,给设计,验证开出的工资是一致的。

工作内容

虽然同属IC前端的职位,但是工作内容差别还是挺大的。

IC设计的主要职责如下:

- 根据功能制定设计方案,制定微架构,编写详细技术文档。

- 使用Verilog进行RTL逻辑设计,实现模块功能。

- 进行逻辑综合、时序分析,完成时序收敛。

- 中小规模的芯片可能还会参与DFT的工作。

- 参与芯片系统调试,后仿真、FPGA验证等工作。

IC验证的主要职责如下:

- 阅读design spec,编写verification spec,制定test plan。

- 搭建验证环境 (C/C++,systemC,systemverilog)。

- 创建test cases。

- 监测regression和提升coverage

- support 其他工程师。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-5IDBVkby-1669871952111)(https://picx.zhimg.com/80/v2-a6893ca74aef54f3472f7fcf6da59f06_720w.webp?source=1940ef5c)]

职位容量

通常,验证的职位与设计的职位大约在2:1,甚至更高。所以验证的职位更多,需求量更大,这也是验证职位的优势。

选择了验证还能做设计吗?

由于验证的岗位较多,上手程度对应届毕业生也更友好一些,很多人会选择做验证的职位。基本只要学会Verilog、SV,C++,以及懂一点UVM的思想就可以参与简单的验证工作了。但是很多人做了一段时间,却想做设计,那还可以吗?

我的回答是可以,但是要记住两点,第一是要趁早,尽量在毕业前几年完成职位的转变。第二是大公司更容易些,有的部门会提供轮岗的机会,一定要抓住。

设计转验证也是同样的道理。

综上,设计和验证在思想和方法上还是有挺大差别的,但在职业发展和薪资上基本一致。各位可以根据自己的兴趣爱好来选择相应的职位。

作者:温戈

链接:https://www.zhihu.com/question/283162522/answer/1727111241

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

其次,是技能要求。

IC设计岗:

① 熟悉Verilog/VHDL/SystemVerilog;

② 熟悉FPGA或ASIC相关开发工具;

③ 熟悉Ethernet, TCP/IP等网络相关协议;

④ 熟悉PCIe,Virtio,RDMA等相关协议。

IC验证岗:

① 熟悉SystemVerilog/C语言,并有实际使用经验;

② 熟悉UVM验证方法学。

作者:IC修真院

链接:https://www.zhihu.com/question/283162522/answer/2168787009

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

作者:SiliconThink

链接:https://www.zhihu.com/question/283162522/answer/2161545842

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

数字IP设计:

根据公司项目需求,开发设计新的数字IP。主要有:算法加速器类(比如图像处理,神经网络加速器,蓝牙/wifi基带数字信号处理),接口总线类(比如UART/IIC/SPI接口, AHB/AXI bus interconnector,MIPI/USB/PCIE接口,DMA控制器,DDR控制器),CPU/GPU类(比如RISC-V)等。

根据公司规模与策略,有些公司对于通用的大型IP采用的是第三方license的方式,比如:CPU/GPU,AHB/AXI bus interconnector,高速接口(DDR PHY, USB PHY, PCIE)。根据公司的核心业务,内部只会开发一些特定功能的数字IP。超大公司为了提升系统性能,对这些通用的大型IP也会自己设计、优化(比如HiSilicon)。

因为设计的东西在公司内部是从无到有,所以数字IP设计岗,对工程师的如下能力有要求:

\1) 从算法/协议到数字IP设计架构的能力,考虑IP设计的PPA;

\2) 接受新知识(算法,协议理解)的能力,自学能力;

\3) FPGA设计使用(一般都要到fpga跑emulation);

SOC设计:

根据公司项目需求,定义一颗芯片需要的功能(IP)模块,CPU选用,系统结构(BUS结构),软硬件交互方式,规划芯片的DFT/CLK&Reset/Power Domain(UPF)/Working Mode(Normal/Standby/Sleep/Deep Sleep)等内容。然后再根据芯片Spec.与系统规划把各个数字/模拟IP有机的结合起来,实现系统功能。

所以需要熟悉CPU性能与使用方法(boot, cache, 多核结构),BUS结构与性能提升,软硬件协同配合。对工程师的如下能力有要求:

\1) 系统级理解分析能力;

\2) 从功能需求到设计规划、实现的能力;

\3) CPU,AHB/AXI片上总线结构与性能优化;

\4) FPGA设计使用(一般都要到fpga跑emulation);

数字验证:

根据IP/芯片的Spec.,建立测试环境,规划测试case(pattern),验证IP/芯片的功能是否正确。在大公司,目前一般采用systemverilog语言结合UVM验证方法学来做仿真验证。验证几乎不存在PPA的考虑,只要考察验证的完备性。所以其更像软件开发工程,对工程师能力有如下要求:

\1) 面向对象的软件开发思维(类似C++);

\2) 测试点拆分,规划能力;

\3) 细致,不放过任何一个测试点(连配置寄存器空间都有专门测试);

如果从unit test, integration test, system test都采用[UVM方法学](https://www.zhihu.com/search?q=UVM方法学&search_source=Entity&hybrid_search_source=Entity&hybrid_search_extra={“sourceType”%3A"answer"%2C"sourc# 学习路线

《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。不看书也能写出个三段式状态机就可以进入下一阶段了。

此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-r8kTZvUe-1669871953160)(https://raw.githubusercontent.com/zianmen/typora_img/master/images202211221442873.png)]

可以选Altera的cyclone IV系列,或者Xilinx的Spantan 6。

还没掌握HDL之前千万不要买开发板,因为你买回来也没用。这里你没必要每次编译通过就下载代码,咱们用modelsim仿真(此外还有QuestaSim、NC verilog、Diamond的Active-HDL、VCS、Debussy/Verdi等仿真工具),如果仿真都不能通过那就不用下载了,肯定不行的。

在这里先掌握简单的testbench就可以了。推荐的教材是《WRITING TESTBENCHES Functional Verification of HDL Models》。

作者:Potato爱学习

链接:https://www.zhihu.com/question/381684248/answer/2447062566

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

3 、 掌握设计方法和设计原则

你可能发现你综合出来的电路尽管没错,但有很多警告。这个时候,你得学会同步设计原则、优化电路,是速度优先还是面积优先,时钟树应该怎样设计,怎样同步两个异频时钟等等。

推荐的教材是《FPGA权威指南》、《IP核芯志-数字逻辑设计思想》、《Altera FPGA/CPLD设计》第二版的基础篇和高级篇两本。学会加快编译速度(增量式编译、LogicLock),静态时序分析(timequest),嵌入式逻辑分析仪(signaltap)就算是通关了。如果有不懂的地方可以暂时跳过,因为这部分还需要足量的实践,才能有较深刻的理解。

4、 学会提高开发效率

因为Quartus和ISE的编辑器功能太弱,影响了开发效率。所以建议使用Sublime text编辑器中代码片段的功能,以减少重复性劳动。Modelsim也是常用的仿真工具,学会TCL/TK以编写适合自己的DO文件,使得仿真变得自动化,推荐的教材是《TCL/TK入门经典》。

你可能会手动备份代码,但是专业人士都是用版本控制器的,所以,为了提高工作效率,必须掌握GIT。

文件比较器Beyond Compare也是个比较常用的工具。此外,你也可以使用System Verilog来替代testbench,这样效率会更高一些。如果你是做IC验证的,就必须掌握System Verilog和验证方法学(UVM)。推荐的教材是《Writing Testbenches using SystemVerilog》、《The UVM Primer》、《System Verilog1800-2012语法手册》。

掌握了TCL/TK之后,可以学习虚拟Jtag(ISE也有类似的工具)制作属于自己的调试工具,此外,有时间的话,最好再学个python。脚本,意味着一劳永逸。

作者:Potato爱学习

链接:https://www.zhihu.com/question/381684248/answer/2447062566

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

1、夏宇闻的verilog设计

2、其他资料多逛FPGA论坛,资源很丰富

作者:徐墨潇

链接:https://www.zhihu.com/question/409150023/answer/1364365658

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

市面上跟fpga相关岗位分为很多路线,很多和业务挂钩的知识点就不做分析了,主要聊聊通用的。

就我知道的而言有以下几种:

FPGA 逻辑工程师

简单的说就是会写 HDL代码的这种,比较初级,掌握几门工具,会写写hdl代码,但是想把代码写好,设计规范还是有非常多的设计技巧的。

学习路线:

systemverilog/verilog ->testbench ->总线规范->资源优化->工具的使用->约束技巧->Debug技巧->联调手段 等等基本就这些。

FPGA 高速接口工程师

在 逻辑工程师 的基础上需要熟悉 Serdes/Transceiver 的硬件知识,以及FPGA中的设计使用方法,以及调试技巧。最重要的就是要熟悉了解 所需要用到的 链路层/传输层的协议,常见的Ethernet/SATA/Hdmi/Mipi/Pcie 等等等等,有的会提供完整的IP,有的则需要自己设计协议。

学习路线:

逻辑工程师的所有 -> Serdes/Transceiver 的相关知识 -> 高速协议 ->异常分析

FPGA 算法工程师

图像/音视频处理算法,深度学习算法,视频流压缩算法等等等等,涉及到非标硬件加速的各类型算法,都有fpga的参与。

学习路线:

算法理论-> matlab -> python ->c/c++ ->HDL移植

FPGA 嵌入式工程师

以前的普通软核,类似单片机,到现在的集成硬核 arm啥的,这部分知识点非常广。

学习路线:

c/c++ 编程 -> rtos编程-> linux编程-> 嵌入式软件方案涉及等等

芯片验证工程师

大部分IC涉及厂商有一个团队会前期在fpga上对芯片进行功能验证。

这部分知识点我不熟悉了,猜想主要和移植,仿真有关系吧。

明德扬系统学习

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-bbVhrcKP-1669871953161)(https://raw.githubusercontent.com/zianmen/typora_img/master/images202211221516416.png)]

FPGA的线下培训哪家做的比较好?

一叶知秋

至芯总体来说价格偏贵,对于没收入的在校生或毕业生,确实吃不消。明德扬相对来说价钱低,可以考虑下,看性价比。v3好像是以前至芯的,现在分了,应该跟至芯差不多。

发布于 2018-05-07 11:00

后综合的工作,基本:时钟部分,时钟树生成,跨时钟域的版图优化;功耗设计,像电源布局,功耗分析,低功耗设计,power gating & clock gating;PR画版图,版图lvs检查,drc检查,gds生成;配合前端做时序分析,post pr时序分析,pr时序修正,PR NETLIST生成给前端仿真;其它工作,dft设计,信号完整性分析等等。

AMD,海康,中兴,小米,芯动,艾为,普冉半导体,信芯微等公司offer的

大厂offer:海思,AMD,汇顶,展讯,联发科,中兴微电子,芯原,全志,海康,晶晨,乐鑫,瑞芯微,国科微,ARM China, …

Verilog语言(比如Michael, D.Cilette的《Verilog HDL高级数字设计》或夏宇闻老师的《Verilog数字系统设计教程》);

还需要理解On-Chip-Bus的基本知识与一个数字系统的基本结构,建议学习理解:AMBA总线,含:APB/AHB/AXI。由于ARM在数字IP领域的领导低位,AMBA总线事实上已经成为数字IC的通用总线结构,必学。

这个推荐哪本书呢

2021-08-30

回复2

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-xe8q5BcW-1669871953161)(https://pic1.zhimg.com/v2-5a9fe31cbffaa3c8ee64c00db41a482d_l.jpg?source=06d4cd63)]

SiliconThink

作者

主要看ARM出的协议。B站有大致讲解:

《On-Chip-Bus》:DDR/Cache原理,APB/AHB/AXI,bus效率分析与提升。

bilibili.com/video/BV1p

作者:温戈

链接:https://www.zhihu.com/question/283162522/answer/1727111241

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

薪资

从薪资来看,IC设计和验证基本相同。

其实这一点从各公司开出的薪资就可以看出来。尤其对于大公司,给设计,验证开出的工资是一致的。

工作内容

虽然同属IC前端的职位,但是工作内容差别还是挺大的。

IC设计的主要职责如下:

- 根据功能制定设计方案,制定微架构,编写详细技术文档。

- 使用Verilog进行RTL逻辑设计,实现模块功能。

- 进行逻辑综合、时序分析,完成时序收敛。

- 中小规模的芯片可能还会参与DFT的工作。

- 参与芯片系统调试,后仿真、FPGA验证等工作。

IC验证的主要职责如下:

- 阅读design spec,编写verification spec,制定test plan。

- 搭建验证环境 (C/C++,systemC,systemverilog)。

- 创建test cases。

- 监测regression和提升coverage

- support 其他工程师。

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-H7963Roy-1669871953162)(https://picx.zhimg.com/80/v2-a6893ca74aef54f3472f7fcf6da59f06_720w.webp?source=1940ef5c)]

职位容量

通常,验证的职位与设计的职位大约在2:1,甚至更高。所以验证的职位更多,需求量更大,这也是验证职位的优势。

选择了验证还能做设计吗?

由于验证的岗位较多,上手程度对应届毕业生也更友好一些,很多人会选择做验证的职位。基本只要学会Verilog、SV,C++,以及懂一点UVM的思想就可以参与简单的验证工作了。但是很多人做了一段时间,却想做设计,那还可以吗?

我的回答是可以,但是要记住两点,第一是要趁早,尽量在毕业前几年完成职位的转变。第二是大公司更容易些,有的部门会提供轮岗的机会,一定要抓住。

设计转验证也是同样的道理。

综上,设计和验证在思想和方法上还是有挺大差别的,但在职业发展和薪资上基本一致。各位可以根据自己的兴趣爱好来选择相应的职位。

作者:温戈

链接:https://www.zhihu.com/question/283162522/answer/1727111241

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

其次,是技能要求。

IC设计岗:

① 熟悉Verilog/VHDL/SystemVerilog;

② 熟悉FPGA或ASIC相关开发工具;

③ 熟悉Ethernet, TCP/IP等网络相关协议;

④ 熟悉PCIe,Virtio,RDMA等相关协议。

IC验证岗:

① 熟悉SystemVerilog/C语言,并有实际使用经验;

② 熟悉UVM验证方法学。

作者:IC修真院

链接:https://www.zhihu.com/question/283162522/answer/2168787009

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

作者:SiliconThink

链接:https://www.zhihu.com/question/283162522/answer/2161545842

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

数字IP设计:

根据公司项目需求,开发设计新的数字IP。主要有:算法加速器类(比如图像处理,神经网络加速器,蓝牙/wifi基带数字信号处理),接口总线类(比如UART/IIC/SPI接口, AHB/AXI bus interconnector,MIPI/USB/PCIE接口,DMA控制器,DDR控制器),CPU/GPU类(比如RISC-V)等。

根据公司规模与策略,有些公司对于通用的大型IP采用的是第三方license的方式,比如:CPU/GPU,AHB/AXI bus interconnector,高速接口(DDR PHY, USB PHY, PCIE)。根据公司的核心业务,内部只会开发一些特定功能的数字IP。超大公司为了提升系统性能,对这些通用的大型IP也会自己设计、优化(比如HiSilicon)。

因为设计的东西在公司内部是从无到有,所以数字IP设计岗,对工程师的如下能力有要求:

\1) 从算法/协议到数字IP设计架构的能力,考虑IP设计的PPA;

\2) 接受新知识(算法,协议理解)的能力,自学能力;

\3) FPGA设计使用(一般都要到fpga跑emulation);

SOC设计:

根据公司项目需求,定义一颗芯片需要的功能(IP)模块,CPU选用,系统结构(BUS结构),软硬件交互方式,规划芯片的DFT/CLK&Reset/Power Domain(UPF)/Working Mode(Normal/Standby/Sleep/Deep Sleep)等内容。然后再根据芯片Spec.与系统规划把各个数字/模拟IP有机的结合起来,实现系统功能。

所以需要熟悉CPU性能与使用方法(boot, cache, 多核结构),BUS结构与性能提升,软硬件协同配合。对工程师的如下能力有要求:

\1) 系统级理解分析能力;

\2) 从功能需求到设计规划、实现的能力;

\3) CPU,AHB/AXI片上总线结构与性能优化;

\4) FPGA设计使用(一般都要到fpga跑emulation);

数字验证:

根据IP/芯片的Spec.,建立测试环境,规划测试case(pattern),验证IP/芯片的功能是否正确。在大公司,目前一般采用systemverilog语言结合UVM验证方法学来做仿真验证。验证几乎不存在PPA的考虑,只要考察验证的完备性。所以其更像软件开发工程,对工程师能力有如下要求:

\1) 面向对象的软件开发思维(类似C++);

\2) 测试点拆分,规划能力;

\3) 细致,不放过任何一个测试点(连配置寄存器空间都有专门测试);

如果从unit test, integration test, system test都采用UVM方法学来做验证,一般设计/验证人员的配比需要1:1,甚至到1:1.5(1个设计,搭配1.5个验证),这种开销只有大公司能承受的起(HiSilicon,比特大陆,中兴,展锐,汇顶)。那一众中小公司(比如全志,瑞芯微,Verisilicon,国科微,…),unit test, integration test还多是采用传统的用verilog语言搭建仿真环境,进行RTL仿真测试的方法。这类工作,一般是数字IP设计工程师兼职完成。只有更复杂的[system test](https://www.zhihu.com/search?q=system test&search_source=Entity&hybrid_search_source=Entity&hybrid_search_extra={“sourceType”%3A"answer"%2C"sourceId"%3A2161545842})可能采用UVM来验证。

另:验证岗位也需要了解一些设计的知识。尤其校招时,验证方向的笔试、面试也会有设计相关的题目。有些大厂(联发科,芯原),校招时,设计,验证是不区分的。进去培训后,再分岗位。

最后,辟谣一下:业内的验证需求比设计大(验证:设计到 2:1,甚至3:1),是这样吗?

但是目前实际情况是:国内验证:设计能到1:1的公司,不超10家。

是公司(比如联发科,海思,展锐,Verisilicon,汇顶等)招不到验证的人,还是公司就不想配比达到1:1?

主要是研发的工资很大,人力成本太贵。今年校招,二三线城市都是25W起步;一线城市30W~35W起步。所以公司人力成本压力很大。

eId"%3A2161545842})来做验证,一般设计/验证人员的配比需要1:1,甚至到1:1.5(1个设计,搭配1.5个验证),这种开销只有大公司能承受的起(HiSilicon,比特大陆,中兴,展锐,汇顶)。那一众中小公司(比如全志,瑞芯微,Verisilicon,国科微,…),unit test, integration test还多是采用传统的用verilog语言搭建仿真环境,进行RTL仿真测试的方法。这类工作,一般是数字IP设计工程师兼职完成。只有更复杂的[system test](https://www.zhihu.com/search?q=system test&search_source=Entity&hybrid_search_source=Entity&hybrid_search_extra={“sourceType”%3A"answer"%2C"sourceId"%3A2161545842})可能采用UVM来验证。

另:验证岗位也需要了解一些设计的知识。尤其校招时,验证方向的笔试、面试也会有设计相关的题目。有些大厂(联发科,芯原),校招时,设计,验证是不区分的。进去培训后,再分岗位。

最后,辟谣一下:业内的验证需求比设计大(验证:设计到 2:1,甚至3:1),是这样吗?

但是目前实际情况是:国内验证:设计能到1:1的公司,不超10家。

是公司(比如联发科,海思,展锐,Verisilicon,汇顶等)招不到验证的人,还是公司就不想配比达到1:1?

主要是研发的工资很大,人力成本太贵。今年校招,二三线城市都是25W起步;一线城市30W~35W起步。所以公司人力成本压力很大。

![[iOS]App Store Connect添加银行卡时的CNAPS代码查询](https://img-blog.csdnimg.cn/1e172f7d45294b6286f492423bb802ef.png)