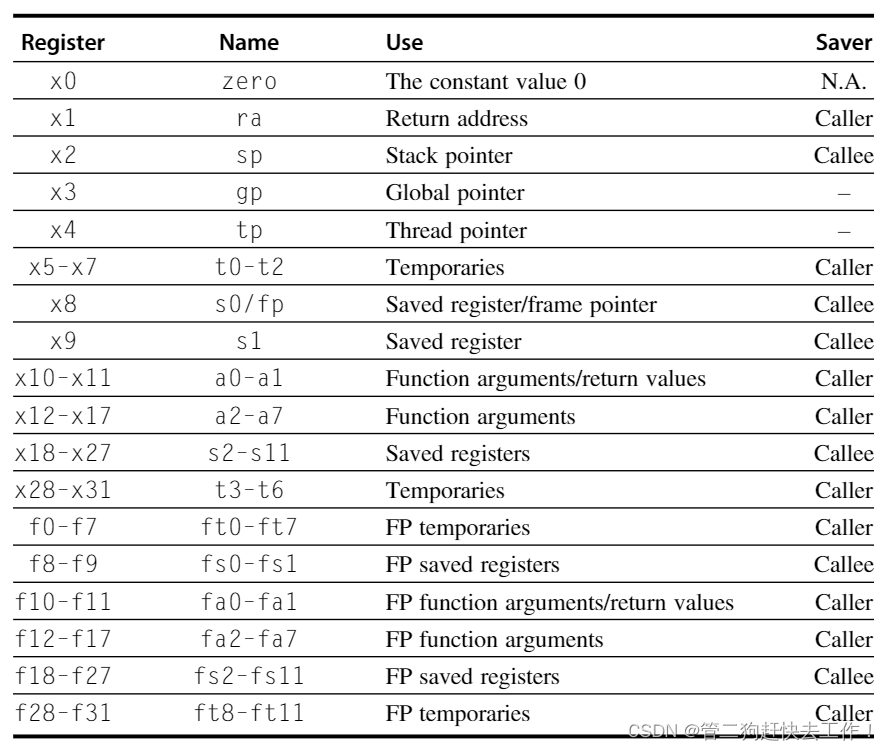

ra : 返回地址寄存器,用来保存函数或宏的返回地址 。

sp : 栈指针寄存器,用来指向栈顶的内存地址 。

gp : 全局指针寄存器,用来指向全局变量的内存地址 。

tp : 线程指针寄存器,用来指向线程局部变量的内存地址 。

t0 - t6 : 临时寄存器,用来保存临时数据或函数调用的返回值 。

s0 - s11 : 保存寄存器,用来保存函数或宏调用前后不变的数据 。

a0 - a7 : 参数寄存器,用来传递函数或宏的参数 。

ISA(指令集架构) :今天几乎所有的 ISA 都被归类为通用寄存器架构,其中操作数是寄存器或内存位置。 80x86 有 16 个通用寄存器和 16 个可以保存浮点数据的寄存器,而 RISC-V 有 32 个通用寄存器和 32 个浮点寄存器。

内存寻址:几乎所有台式机和服务器,包括 80x86、ARMv8 和 RISC-V,都使用字节寻址来访问内存操作数。 一些体系结构,如 ARMv8,80x86 和 RISC-V 不需要对齐,但如果操作数对齐,访问通常会更快。

内存寻址对不对齐是指数据在内存中的位置是否与处理器的内存访问粒度相匹配。内存访问粒度是指处理器一次能够读写的内存字节数,比如2字节、4字节、8字节等。数据在内存中的位置可以用一个地址来表示,地址是一个二进制数,可以被处理器的内存访问粒度整除或不能整除。如果能整除,就称为对齐的地址;如果不能整除,就称为不对齐的地址。

举个例子,假设处理器的内存访问粒度是4字节,那么地址0x00000000、0x00000004、0x00000008等都是对齐的地址,因为它们都能被4整除;而地址0x00000001、0x00000003、0x00000005等都是不对齐的地址,因为它们都不能被4整除。

内存寻址对不对齐会影响处理器访问数据的效率和正确性。如果数据在内存中是对齐的,那么处理器可以一次读写一个或多个数据,比如一个4字节的整数或两个2字节的短整数;如果数据在内存中是不对齐的,那么处理器可能需要多次读写才能获取一个或多个数据,比如一个跨越两个4字节边界的8字节浮点数。

寻址模式:除了指定寄存器和常量操作数之外,寻址模式还指定内存对象的地址。 RISC-V 寻址模式有寄存器、立即数(用于常量)和位移,其中将常量偏移量添加到寄存器以形成内存地址。 80x86 支持这三种模式,外加三种位移变体:无寄存器(绝对)、两个寄存器(基于位移索引)和两个寄存器,其中一个寄存器乘以操作数的大小(以字节为单位)(基于缩放索引和位移) ). 它更像后三种模式,减去位移字段,加上寄存器间接、索引和基于缩放索引。 ARMv8 具有三种 RISC-V 寻址模式加上 PC 相对寻址、两个寄存器的总和以及两个寄存器的总和(其中一个寄存器乘以操作数的字节大小)。 它还具有自动递增和自动递减寻址,其中计算出的地址替换了用于形成地址的其中一个寄存器的内容。

操作数的类型和大小:与大多数 ISA 一样,80x86、ARMv8 和 RISC-V 支持 8 位(ASCII 字符)、16 位(Unicode 字符或半字)、32 位(整数或字)的操作数大小, 64 位(双字或长整数),以及 32 位(单精度)和 64 位(双精度)的 IEEE 754 浮点数。 80x86 还支持 80 位浮点(扩展双精度)。

运算:运算的一般类别是数据传输、算术逻辑、控制和浮点数。 RISC-V 是一种简单易流水化的指令集架构,是 2017 年使用的 RISC 架构的代表。

控制流指令:几乎所有 ISA都支持条件分支、无条件跳转、过程调用和返回。 这三个都使用 PC 相对寻址,其中分支地址由添加到 PC 的地址字段指定。 有一些小差异。 RISC-V 条件分支(BE、BNE 等)测试寄存器的内容,而 80x86 和 ARMv8 分支测试条件代码位设置为算术/逻辑运算的副作用。 ARMv8 和 RISC-V 过程调用将返回地址放在寄存器中,而 80x86 调用 (CALLF) 将返回地址放在内存中的堆栈中。

![[架构之路-190]-《软考-系统分析师》-4-据通信与计算机网络-5-图解CRC计算方法与步骤](https://img-blog.csdnimg.cn/6da120259ec7433581c7e7a634f21c8f.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBAcXFfNTI1MTQ3NTA=,size_20,color_FFFFFF,t_70,g_se,x_16#pic_center)