前言

随着芯片面临着应用场景丰富多变、集成功能模块越来越多、片内通信及模块间接口越来越复杂、设计规模越来越大以及PPA要求越来越高的需求,芯片设计方法面临越来越大的挑战。架构的合理性、完备性和一致性很大程度上决定了芯片设计的成败。基于同样的IP及工艺制程,不同架构实现相同功能所需的资源开销及性能差距很大。因此,芯片设计的第一环节——系统架构设计及其仿真优化,变得越来越重要,是后续一切硬件、软件开发的基础。

由于传统方法逐渐无法处理迅速发展的集成了大量功能的系统算法内容,ESL设计在近几年快速普及。ESL设计,即电子系统级(Electronic System Level)设计方法学,是一种抽象程度高于RTL(Register Transfer Level,寄存器传输级)设计的芯片设计与验证方法。在芯片设计过程中,工程师需要设计的内容通常包括芯片性能模型、芯片功耗模型、芯片功能模型,在此过程中以及芯片验证过程中,均可以利用ESL设计来实现。ESL设计可以为芯片设计工程师提供开发、优化、验证芯片架构与嵌入软件的方法,以及提供验证服务。

ESL设计的作用

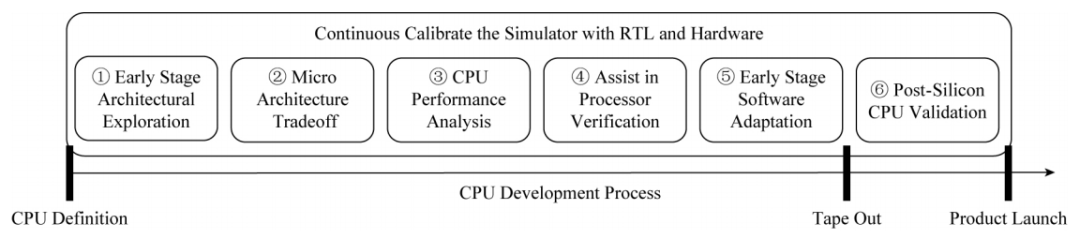

从仿真目的来说,ESL设计可以分为芯片架构仿真,芯片co-sim验证,芯片软硬件联调:芯片架构仿真包括芯片的性能仿真与功耗仿真;芯片co-sim验证包括子系统级联合仿真验证与模块级联合仿真验证;芯片软硬件联调目的是与RTL开发解耦,快速完成软硬件联合调试。 例如在架构性能仿真场景下,需要根据架构设计需求,在给定应用场景或benchmark情况下,将对性能有影响的组件构建在一起模拟实际运行场景,以动态运行的方式获取感兴趣的性能数据,以完成架构设计的寻优、调优或确认。 下图展示了仿真器在CPU开发过程中的作用[1]:

由图可知:

在芯片开发早期,基于仿真器可以进行微结构探索和粗粒度微结构定义,此时仿真器的开发抽象层次较高;

随着处理器设计的不断推进和仿真器的不断完善,基于仿真器可以持续对芯片为芯片微结构进行评估、修改和取舍;

当仿真器趋于成熟,可以对微结构、多核互联系统、一致性协议等进行详细性能分析,基于分析结果对微结构进行微调;

在对处理器逻辑设计进行验证的阶段,仿真器可以作为参考模型辅助进行验证,可以快速定位逻辑设计错误;

在未流片之前基于仿真器就可以开展系统软件开发和适配工作,这样可以在芯片流片结束后以最快速度启动系统软件。

ESL仿真器的基本组成

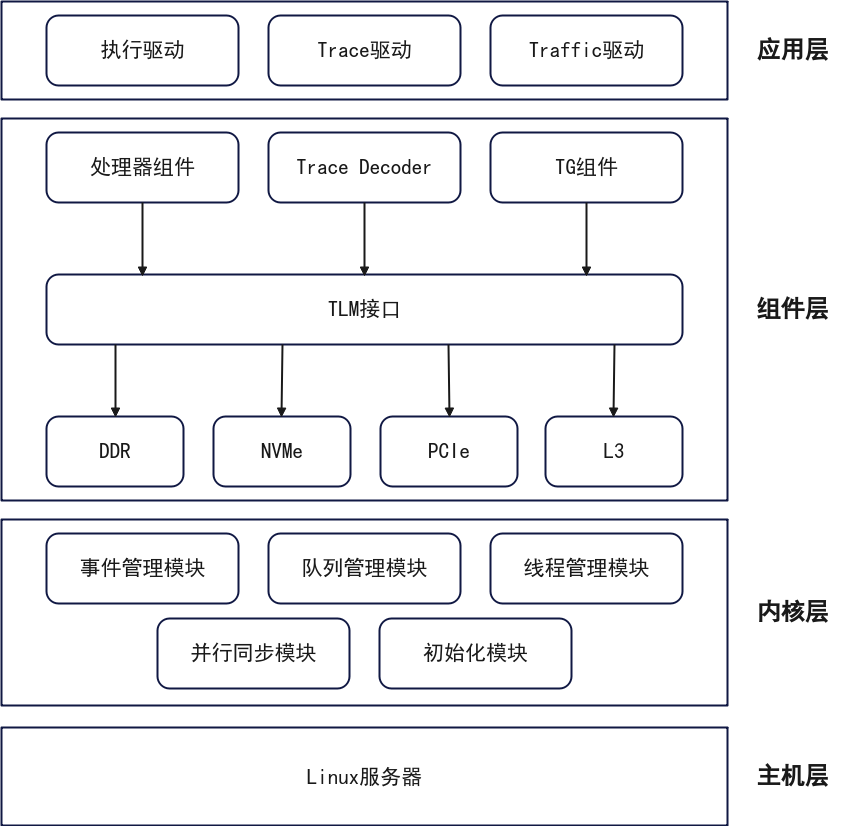

完整的ESL仿真器由4个层次构成:应用层、组件层、内核层和主机层。其中组件层和内核层构成仿真器的主体,应用层为仿真器提供输入,而主机层承载了仿真器的运行,如图所示:

ESL模拟器基本组成

应用层:负责芯片工作时的场景构建,用来产生仿真器的输入或仿真激励,包含三种应用模式:

执行驱动:运行业务软件,生成流量驱动。与目标系统程序的运行方式类似,都是执行编译好的可执行二进制代码;

Trace驱动:解析其他平台生成的处理器核Trace轨迹,生成流量驱动。用trace代替实际CPU模型,将每条指令顺序执行所产生的所有信息作为仿真器的输入;

Traffic驱动:根据分解的业务动作配置表及驱动关系,生成流量驱动。给目标架构注入流量,实施载体为Traffic Generator(TG)。

组件层:基于开源软件或工具生成的第三方IP或厂商提供的多精度模型搭建生成的待测芯片架构,使用TLM接口通信。组件层一般包括处理器组件、TG组件、接口转换组件、互联组件、DDR组件和Cache组件等。

内核层:以事件队列为核心,控制仿真事件的正确调度、仿真时间的正确推进,控制整体仿真进程,支持组合目标硬件系统,支持串行、并行仿真和仿真加速手段。

主机层:Linux多核工作站,承载架构仿真任务。

ESL设计与实现

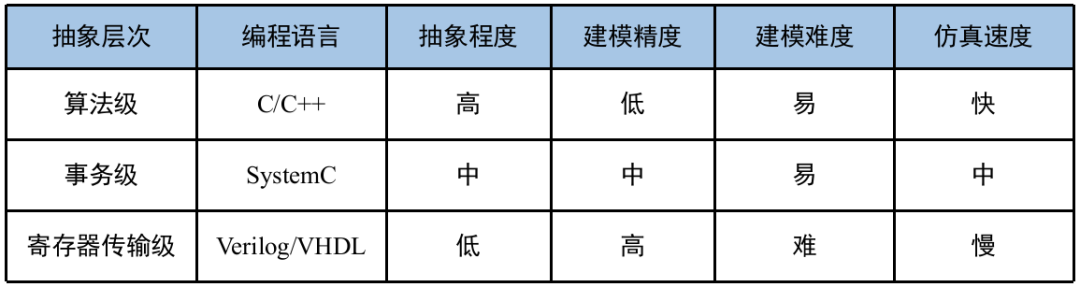

系统级设计中,首先要解决的问题是如何描述系统也就是所谓的系统建模。系统建模的抽象层次可以分为三类:

算法级建模(ALF,Algorithm Function):功能模型,没有时序概念,与体系架构及具体实现关系不大,没有办法进行进一步的性能分析。

寄存器传输级建模(RTL,Register Transfer Level):关注电路在寄存器、连线层次上的细节,模型建立和仿真都需要很长时间。

事务级建模(TLM,Transaction Level Modeling):介于ALF和RTL之间,可以为算法选择、软硬件划分、协同仿真的接口建模提供折中的评价方法。

三者的关系如图所示:

ESL建模抽象层次对比

ESL建模抽象层次对比

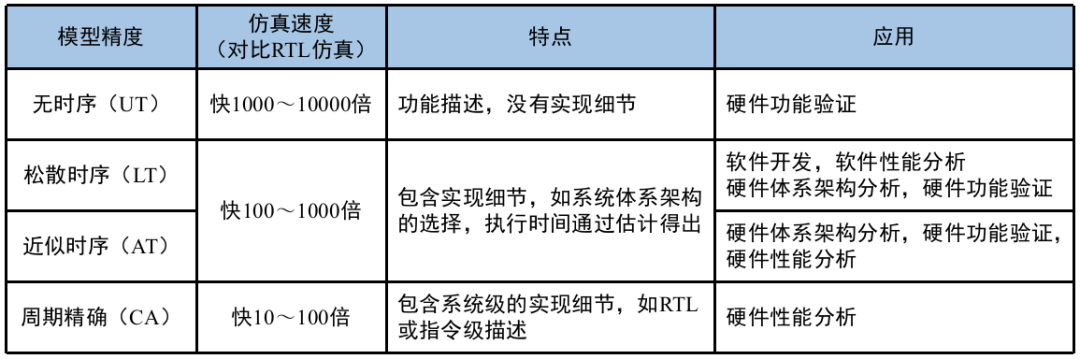

ESL设计的核心是事务级建模,这里的事务是指模块之间的数据和事件的交互。事务级建模的核心概念是在一个系统建模的过程中将运算功能和通信功能分开,模块之间的通信通过函数调用来实现。与RTL级模型相比较,TLM可以减少事件和信息的处理,而且事务级模型所需的程序代码更少,执行速度更快。 根据系统描述精度的不同,OSCI(The Open SystemC Initiative)提出的TLM1.0和TLM2.0标准对事务级建模进行进一步细分,如图所示:

ESL建模精度对比

可以看出,没有时序信息的事务级模型的建模和仿真速度最快,精确到周期的事务级相对较慢,但如需进行硬件体系架构分析或硬件性能分析往往需要近似时序或周期精确的建模精度。

在ESL实现上,为了达到最优的性能,开发者需要利用硬件亲和的编程语言如:SystemC和C++来进行开发。这是因为:SystemC和C++的使用使得ESL框架可以高效调用硬件的底层API,从而最大限度发挥硬件性能。同时,现代操作系统(如Linux和Windows)提供丰富的基于SystemC和C++的编程接口(如文件系统,网络编程,多线程管理等),通过直接调用操作系统API,可以降低框架运行的开销。

从精度的角度分析,10~20%的精度损失换来的仿真速度的1000倍提升以及架构迭代速度的10倍提升,被认为是可以承担的代价。同时从易用性角度分析,Python等高级语言具备以C和C++为核心的低层次编程接口,通过Python丰富的库函数,可以快速搭建系统架构与性能分析(Profiling)平台。为了实现处理器的敏捷开发,UC Berkeley还开发了高度参数化的硬件构建语言Chisel,可以直接使用面向对象的设计方法学描述处理器功能,通过编写一次硬件代码可以生成包含C++周期精确仿真器、FPGA Verilog和ASIC Verilog这三个目标,使得处理器设计效率提升一个数量级。

开源ESL仿真器

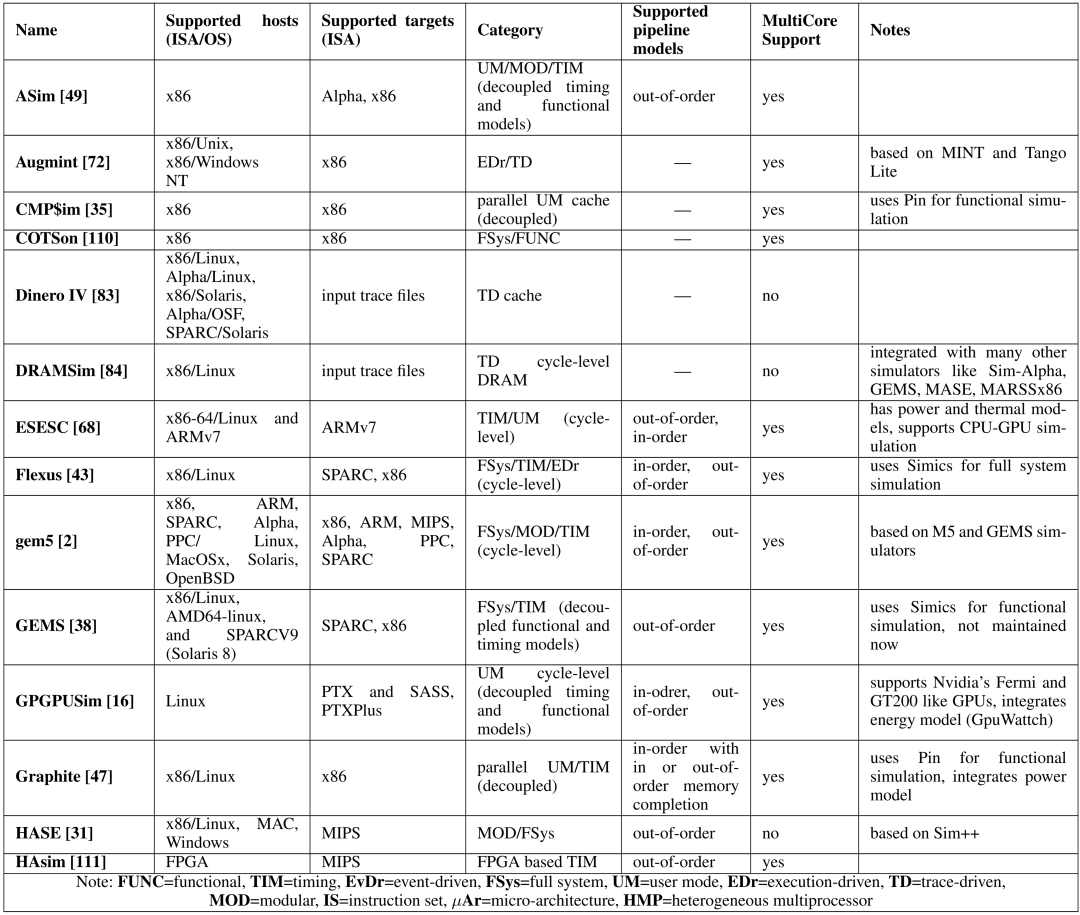

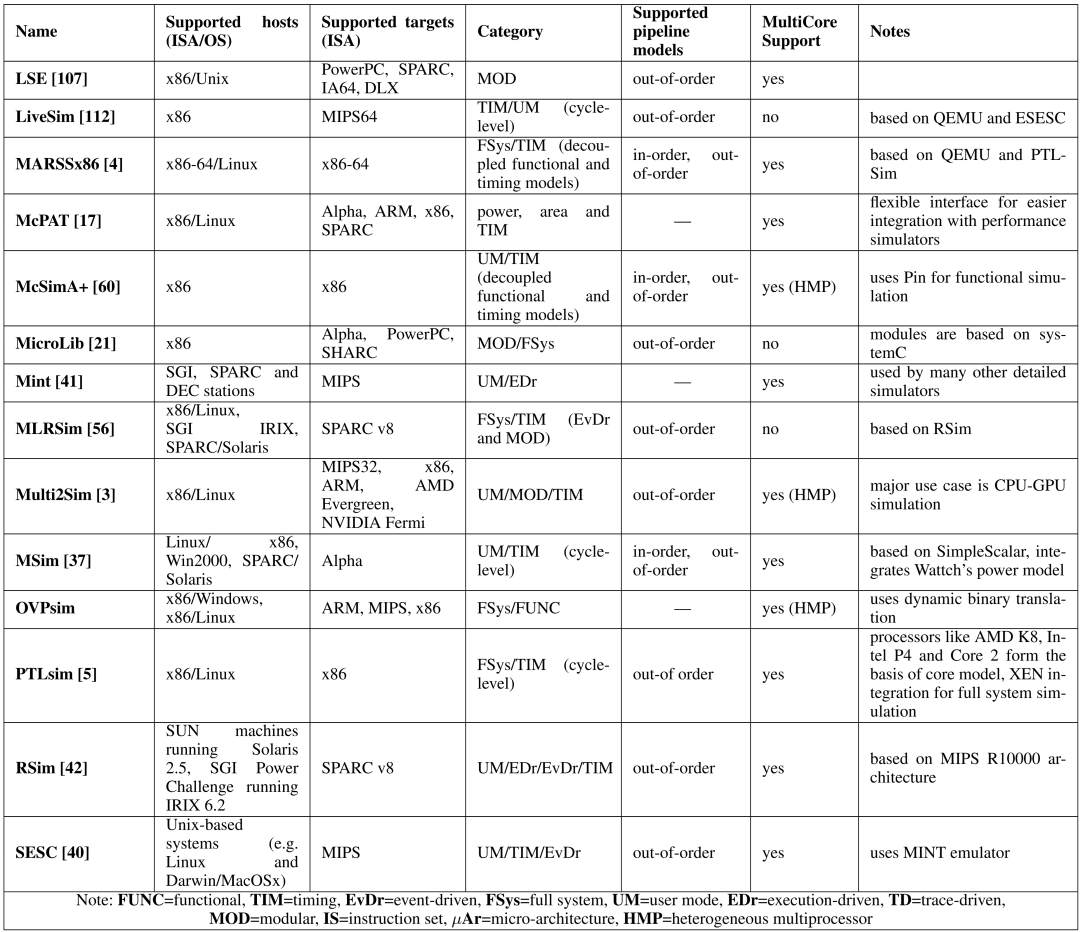

目前开源的ESL仿真器种类较多,不同的开源仿真器具有不同特点,因此开发人员可以根据所研究的内容选择合适的开源仿真器平台进行实验,为系统架构研究提供了很高的灵活性,有助于快速实现原型系统。同时,开源仿真器的社区一般比较活跃,生态环境好,在原型系统实现过程中,遇到问题可以很快找到解决方案,从而快速构建实验用的原型系统。

但使用开源模拟器也存在一定的局限性,各厂商的微架构一般与开源模拟器的微架构差别较大,因此修改模拟器的代价较大。例如GEM5模拟器中乱序执行流水线的设计主要参考的是Alpha21264处理器,基于此进行微架构修改的工程量较大,实现架构搭建及性能分析所需的人力及时间要高于商用工具。此外,由于模拟器开发是一项较大的软件工程,而软件工程的框架一旦确定,修改起来也会比较棘手。

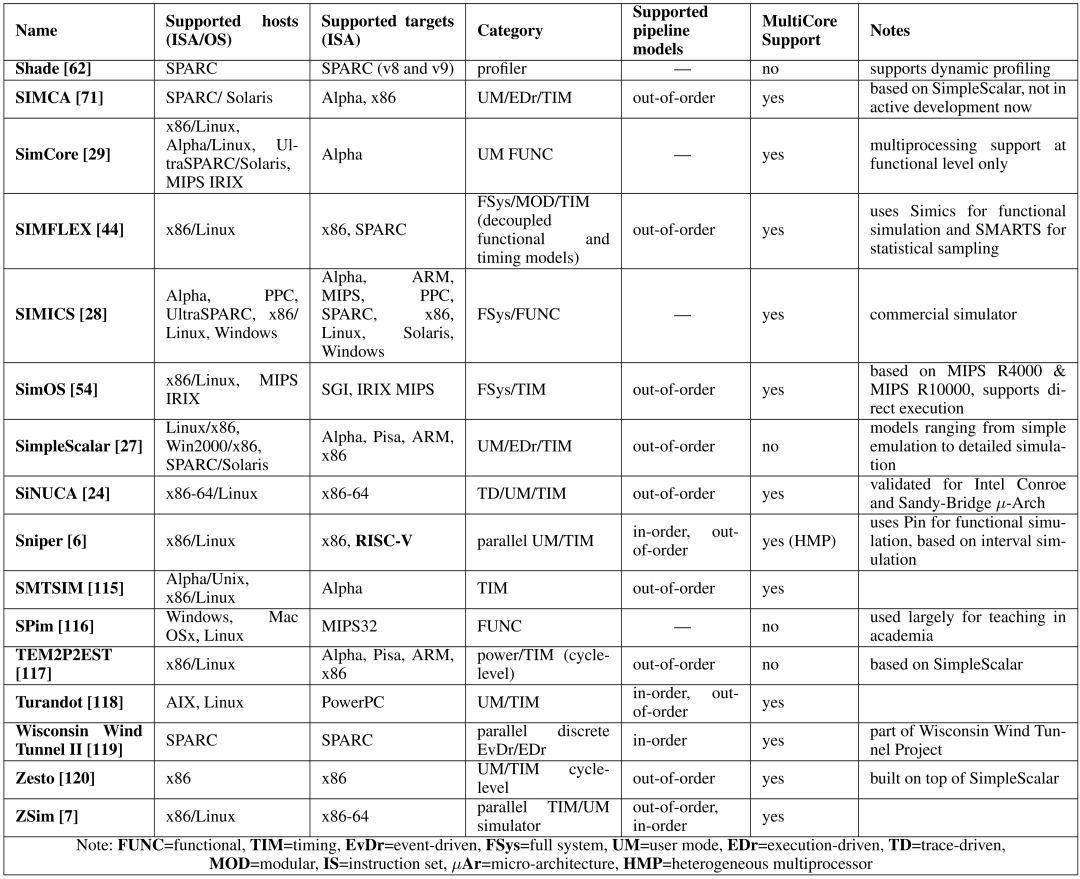

下表整理了常见的开源计算机架构/微架构仿真器[2]。

总结

ESL设计对于简化芯片设计流程,提高芯片设计效率起到了重要作用。本文从芯片设计实例出发,简要介绍了ESL设计的定位与实现方式,总结了开源ESL仿真器供读者参考。

最后,欢迎大家关注我们团队的Adlik深度学习推理工具链开源项目,Adlik社区期待你的加入。

参考文献

[1] 张乾龙, 侯锐, 杨思博, 赵博彦, 张立新. 体系结构模拟器在处理器设计过程中的作用[J]. 计算机研究与发展, 2019, 56(12): 2702-2719.

[2] Akram A, Sawalha L. A survey of computer architecture simulation techniques and tools[J]. Ieee Access, 2019, 7: 78120-78145.

![[EIS 2019]EzPOP](https://img-blog.csdnimg.cn/a3a869af51d4464f9ea835df3eaefaea.png)