学习目标:

学习静态随机存取存储器(SRAM)的基本原理、结构和工作方式,理解其与动态随机存取存储器(DRAM)的区别和优缺点,掌握SRAM的性能参数和应用领域,了解SRAM的发展历程和未来趋势。同时,学习SRAM的设计方法和优化技术,包括电路设计、布局布线、时序分析、功耗优化等方面,熟悉SRAM的测试方法和可靠性评估方法,能够使用常见的SRAM设计工具和仿真软件进行SRAM的设计和验证。

学习步骤:

-

了解静态随机存取存储器(SRAM)的基本概念、结构和工作原理,以及其与动态随机存取存储器(DRAM)的区别和优缺点。

-

了解SRAM的存储单元(cell)的基本结构,包括传输门(transfer gate)、存储节点(storage node)、读写线(bit line)、字线(word line)等。

-

学习SRAM的写入和读取操作,包括写入时的地址选择、数据输入和存储单元状态改变,读取时的地址选择、数据输出和存储单元状态读取。

-

理解SRAM的时序要求,包括存储单元的写入和读取时间、字线的激活时间、预充电时间等。

-

了解SRAM的常见应用场景,如高速缓存、寄存器等,并学习如何根据应用场景选择适合的SRAM芯片。

-

学习SRAM的性能指标,如容量、速度、功耗、可靠性等,以及如何评估和比较不同的SRAM芯片。

-

实践操作,进行SRAM的设计、仿真、布局和验证,加深对SRAM的理解和应用能力。

-

阅读相关的学术论文、技术手册、数据手册等,了解SRAM的最新发展和未来趋势,保持对SRAM领域的更新和深入认识。

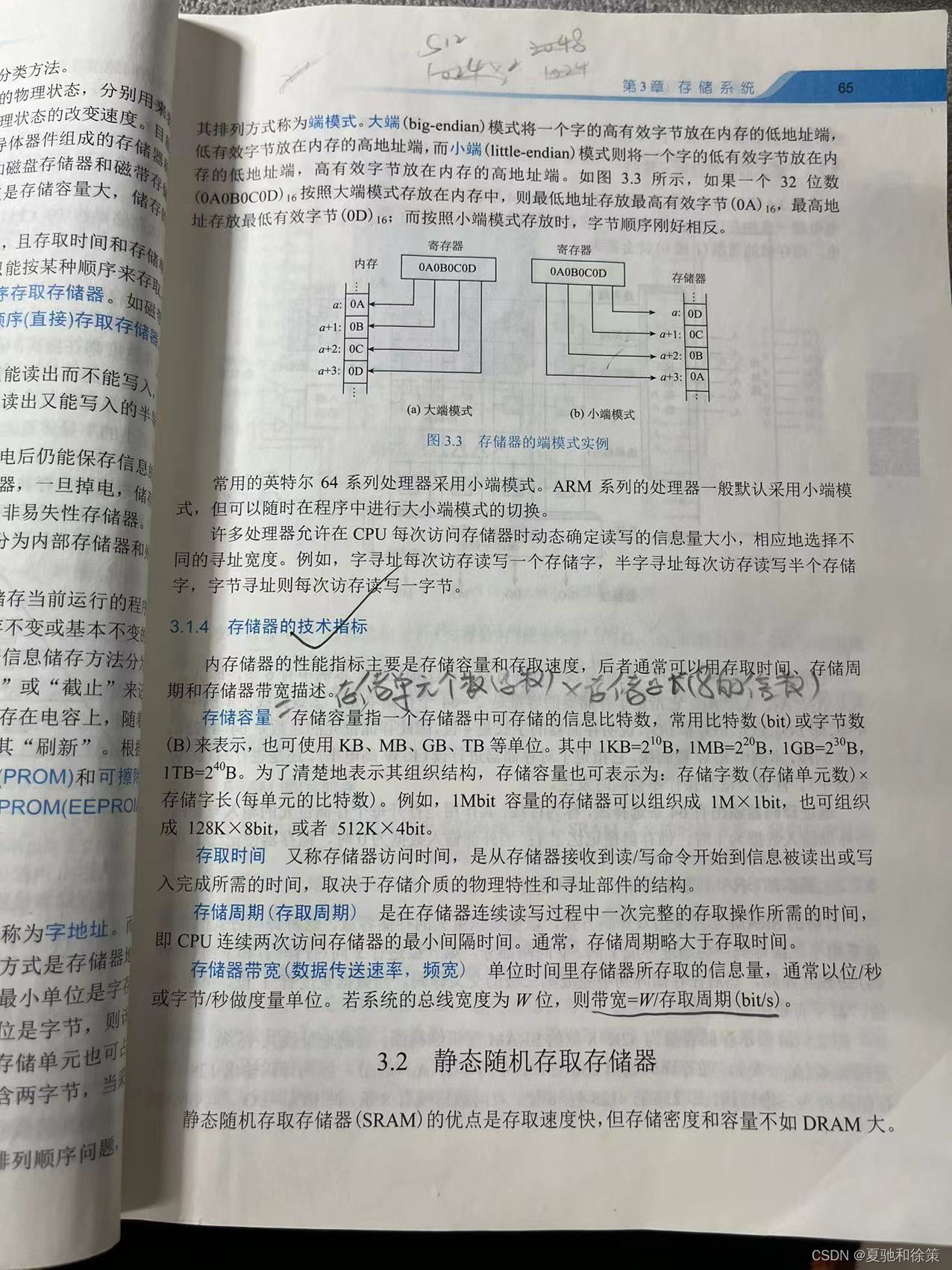

3.2.1 基本的静态存储元阵列

静态存储元阵列是构成静态随机存取存储器(SRAM)的基本单元,它通常由存储单元和访问电路组成。每个存储单元通常由一个存储电容和一个存储晶体管组成,这些存储单元被组织成一行或一列,构成一个存储单元阵列。

静态存储元阵列的访问电路包括读取和写入电路,用于控制存储单元的读取和写入操作。读取电路通常包括一个预读电路和一个比较电路。预读电路将要读取的数据预读到一个数据线上,并将其与存储单元中存储的数据进行比较。比较电路产生一个输出信号,指示读取的数据是否与存储单元中存储的数据相等。写入电路通常包括一个写入控制电路和一个写入数据选择电路,用于将数据写入存储单元中。

静态存储元阵列通常被组织成多个存储块,每个存储块包括多个存储单元阵列和一些控制电路,用于实现存储器的读取、写入和其他操作。存储块之间通常通过一些连接电路进行连接,形成一个完整的存储器。常见的静态随机存取存储器包括SRAM芯片和SRAM模块等。

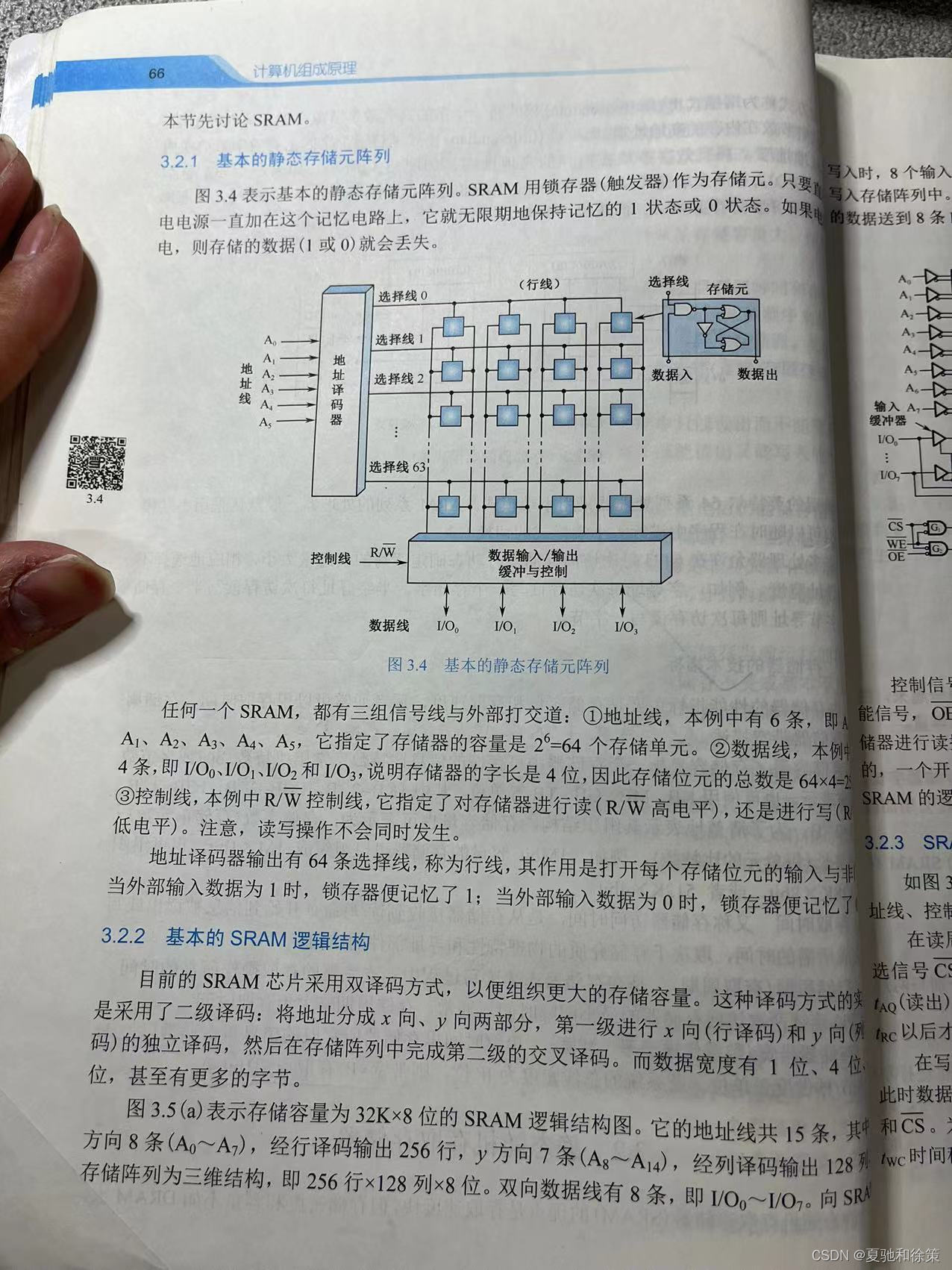

3.2.2 基本SRAM逻辑结构

我的理解:

SRAM是一种静态随机存取存储器,由于其高速读写和易于实现的特点,被广泛应用于各种计算机系统中。SRAM存储器通常由多个存储单元组成,每个存储单元可以存储一个二进制位。

SRAM的基本逻辑结构包括两个部分:存储单元阵列和控制电路。存储单元阵列是由多个存储单元组成的矩阵,每个存储单元都有一个地址,可以通过地址线来访问。控制电路主要负责对存储单元阵列进行读写操作,包括地址译码、数据输入输出、读写控制等。

具体来说,一个SRAM存储器通常包括以下几个部分:

-

存储单元阵列:由多个存储单元组成的矩阵,每个存储单元可以存储一个二进制位。存储单元通常是由一个存储器单元和一个读/写门组成。存储器单元负责存储数据,读/写门负责控制数据的读写。

-

地址译码电路:用于将CPU发出的逻辑地址转换成SRAM中对应的物理地址。地址译码电路通常由多个逻辑门和寄存器组成,可以实现不同的寻址模式和存储器容量。

-

数据输入/输出电路:用于将CPU发出的读写数据传输到存储单元阵列中,或将存储单元阵列中的数据传输到CPU。数据输入/输出电路通常由多个三态缓冲器和选择器组成,可以实现高速数据传输和多路选择功能。

-

读写控制电路:用于控制存储单元阵列的读写操作。读写控制电路通常包括读/写使能信号、时序控制信号、读/写选择信号等,可以实现不同的读写操作和存储器容量。

总之,SRAM的逻辑结构包括存储单元阵列、地址译码电路、数据输入/输出电路和读写控制电路等部分,这些部分协同工作,实现了高速、可靠的数据存储和读写功能。

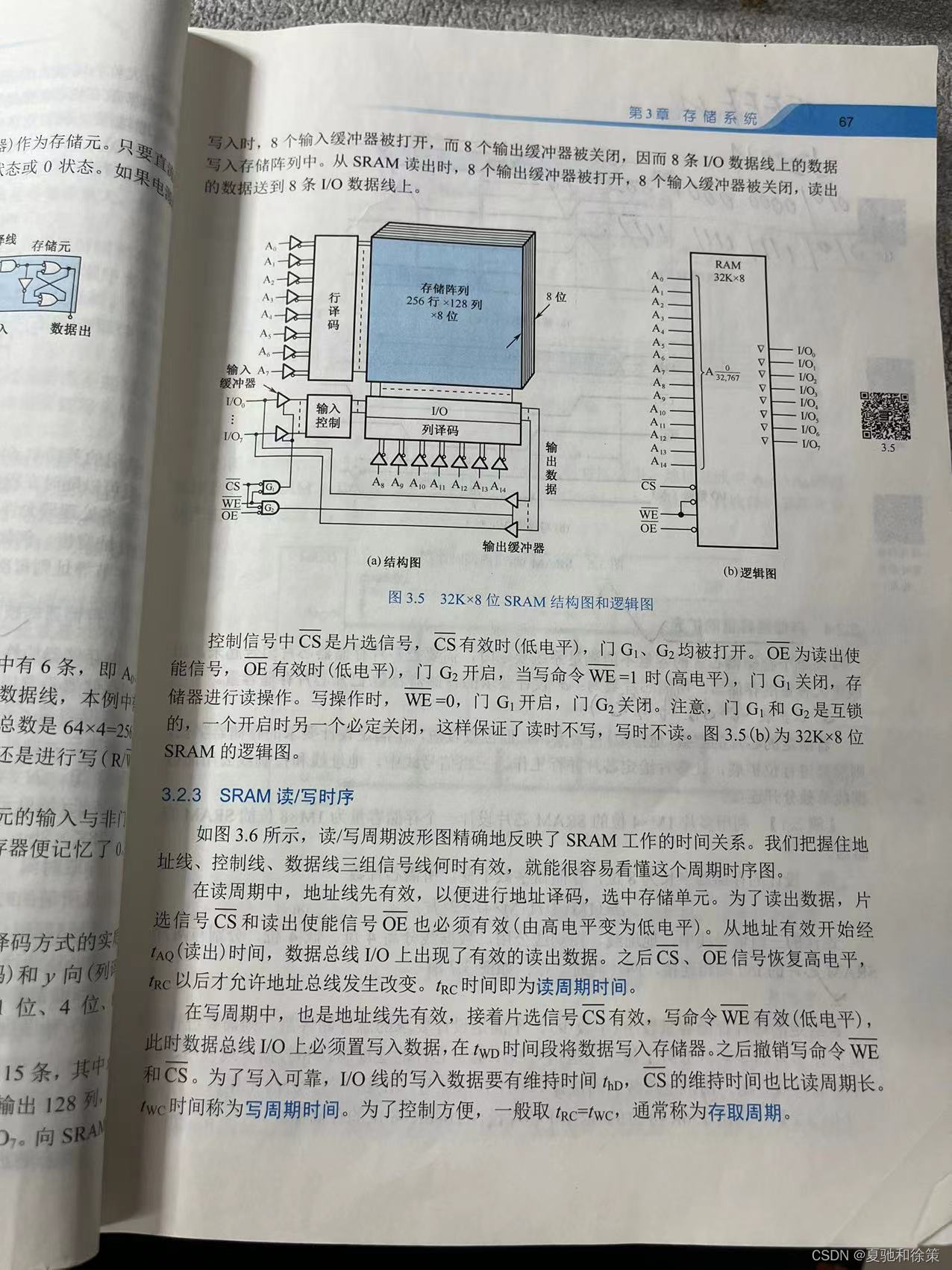

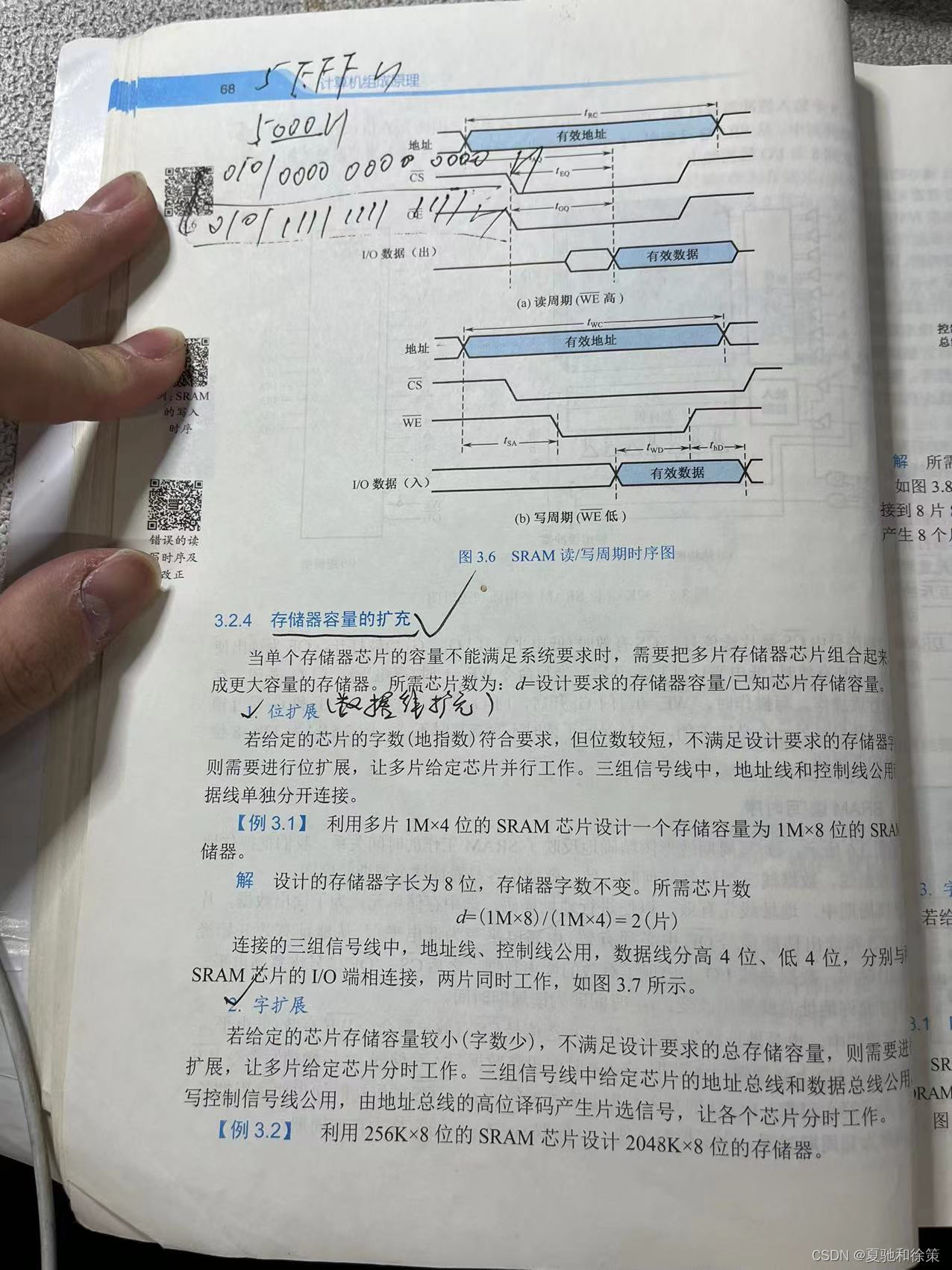

3.2.3 SRAM读/写时序

SRAM(静态随机存取存储器)读/写时序是指在进行读/写操作时,各个信号的变化顺序和时间间隔的规定。下面是常见的 SRAM 读/写时序:

读操作:

- 地址输入:首先CPU将地址信息送到地址总线上,通过地址译码电路选择要读取的SRAM芯片。

- 读信号输入:CPU向SRAM输入读信号(例如 RD# 信号),使 SRAM 进入读状态。

- 存储器响应:SRAM 将存储器中对应地址的数据放置在数据总线上,等待CPU的读取。

- 数据输出:CPU接收到存储器的响应后,从数据总线上读取数据。

写操作:

- 地址输入:首先CPU将地址信息送到地址总线上,通过地址译码电路选择要写入的SRAM芯片。

- 写信号输入:CPU向SRAM输入写信号(例如 WR# 信号),使 SRAM 进入写状态。

- 数据输入:CPU将要写入的数据放置在数据总线上,等待写入。

- 写入确认:SRAM 接收到写信号后,确认可以写入,将数据从数据总线上读取并写入存储器中。

需要注意的是,在 SRAM 的读写操作中,由于 SRAM 的响应速度非常快,因此信号的时序和时间间隔非常重要,一旦出现不符合要求的情况,就可能导致读写操作失败或者产生错误。

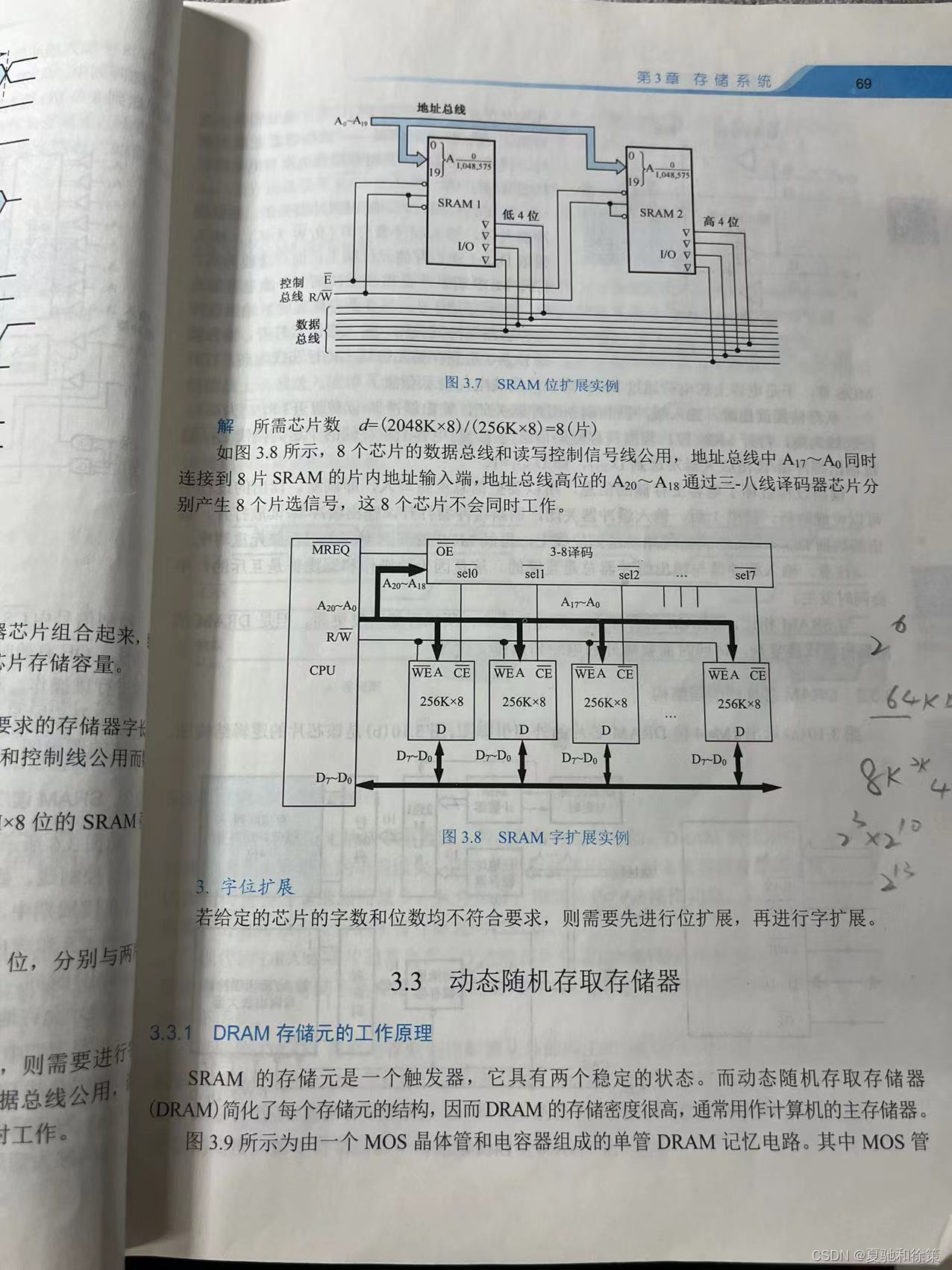

3.2.4 存储器容量的扩充

存储器容量的扩充是指通过一定的方法增加存储器的容量,以满足更大存储需求的过程。在计算机系统中,存储器的容量往往是一个重要的性能指标,因此存储器容量的扩充也是一项非常重要的技术。

存储器容量的扩充主要有以下几种方法:

-

单体存储芯片容量扩充:单体存储芯片容量扩充是指通过改进存储芯片的工艺技术,增加单个存储芯片的容量。这种方法可以在不改变系统设计的情况下,增加存储器的容量。

-

存储芯片数量扩充:存储芯片数量扩充是指通过增加存储芯片的数量,以增加存储器的容量。这种方法需要对系统进行重新设计,增加存储芯片的数量可能会引起数据线的延长、芯片选择信号的复杂等问题。

-

存储器芯片组扩充:存储器芯片组扩充是指在原有的存储器基础上增加新的存储器芯片组。这种方法需要重新设计系统,并增加一些控制电路,以确保新的存储器芯片组能够正常工作。

-

存储器级联扩充:存储器级联扩充是指通过将多个存储器级联起来,以增加存储器的容量。这种方法可以在不改变系统设计的情况下,增加存储器的容量。但是级联会增加存储器的访问延迟和功耗。

以上几种方法可以单独使用,也可以结合使用,具体的扩充方法需要根据具体的应用情况来确定。

总结:

静态随机存取存储器(SRAM)是计算机存储器中的一种,具有快速读/写速度和易于实现的优点。以下是SRAM的重点、难点和易错点总结:

重点:

- SRAM的逻辑结构和基本存储元阵列。

- SRAM的读/写时序,包括地址信号和控制信号的设置和时序关系。

- SRAM的容量扩充方法和技术,包括级联和交织等方式。

难点:

- SRAM的读/写时序比较复杂,需要理解控制信号的作用和时序关系,同时需要考虑时序误差对读/写操作的影响。

- SRAM的容量扩充需要考虑多个存储器的地址映射和数据传输,容易出现地址冲突和数据丢失等问题。

易错点:

- 地址信号的设置错误,容易导致读/写错误。

- 控制信号的设置不当,容易导致时序错误和读/写错误。

- 容量扩充时没有考虑地址映射和数据传输的问题,容易导致地址冲突和数据丢失等问题。

为了避免以上问题,学习SRAM时应该注重理解逻辑结构、时序和容量扩充方法,多做实验并注意调试过程中的细节问题。

![Linux [常见指令 (1)]](https://img-blog.csdnimg.cn/1341528feb884ded9fc920b6f47ce390.png)