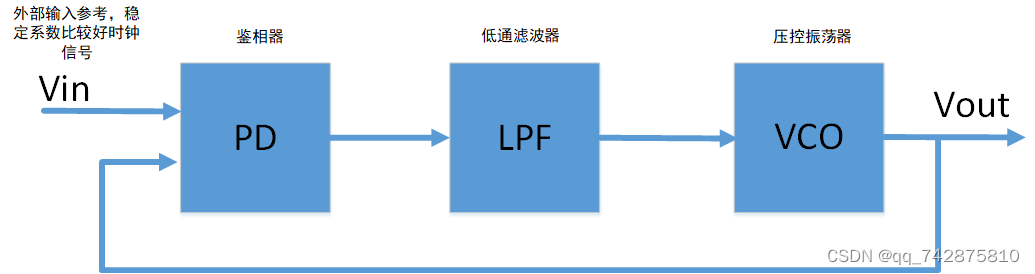

锁相环是一个能够比较输入与输出信号相位差的反馈系统,利用外部输入的参考信号控制环路内部的振荡信号的频率和相位,使振荡信号同步至参考信号。

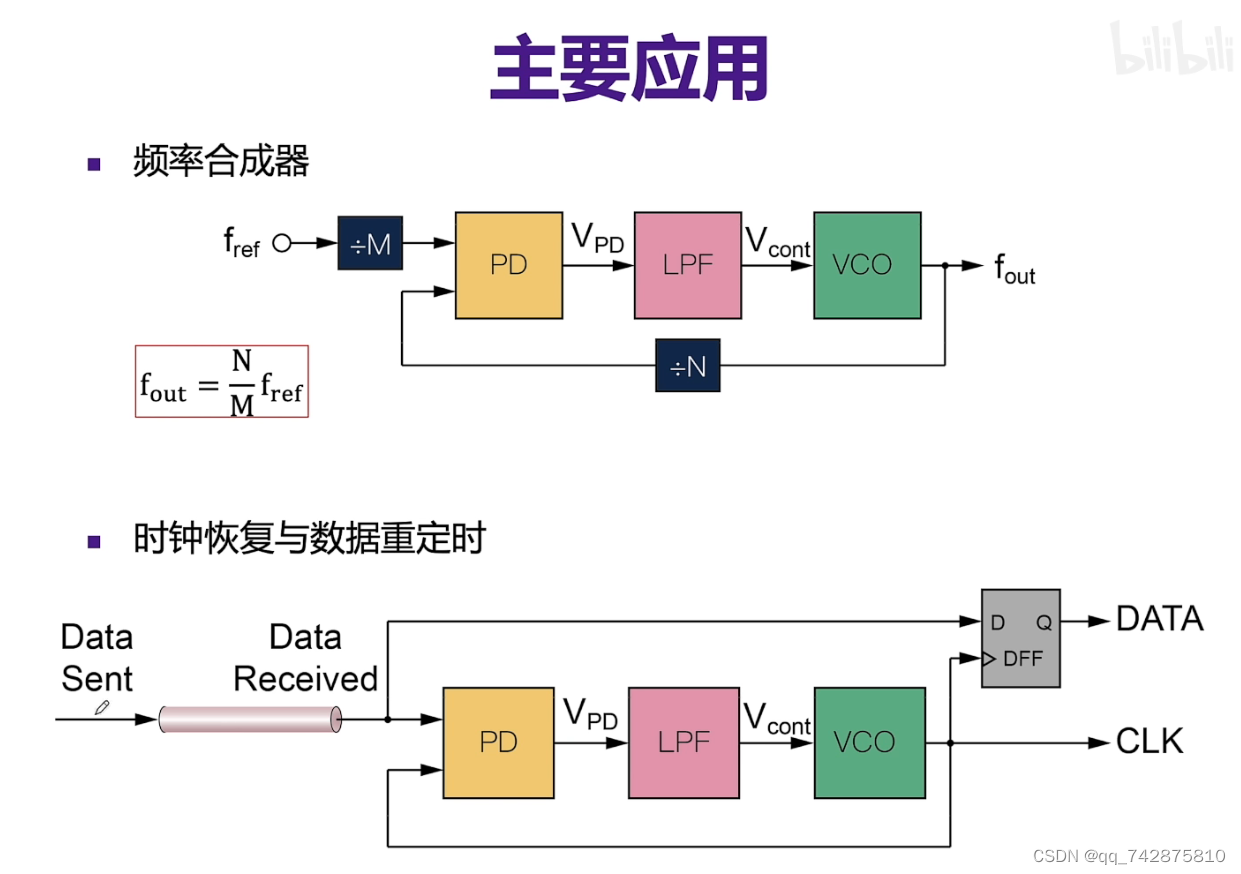

问题:既然是利用外部的参考时钟控制内部的振荡信号频率和相位使内部信号同步至外部参考,那为什么不直接用导线将外部参考信号连接到内部振荡信号呢?频率合成,比如10M产生100MHz,200MHz;时钟恢复,长距离传输后,在源端同步系统,经过传输后时钟和数据不同步,使用鉴相电路使时钟和数据同步。

鉴相器能够鉴别输入参考时钟和输出时钟的相位。一开始,Vin和Vout的相位是不同步的,当检测到两者相位不一致时,鉴相器会产生一个检测信号,该信号包含高频成分和低频成分,低通滤波器滤除高频成分,留下比较稳定的低频成分,稳定的低频分量控制压控振荡器。当Vout相位比Vin滞后时,LPF输出电压升高使VCO振荡频率更快一些,减小相位差。经过一段时间的反馈调整,Vout和Vin的相位、频率一致,保持稳定,这时候PLL就锁定了。

上图M和N为分频器,对输入参考进行M分频,多输出进行N分频,当锁相环稳定后,在鉴相器输入处满足Fref/M=Fout/N。由此可以推出,Fout=N/M * Fref。由此可以看到,调整N 和M的比值可以输出各