JTAG硬件电路设计

- 1 简介

- 1.1 JTAG分类

- 1.2 ARM调试器

- 2 设计要点

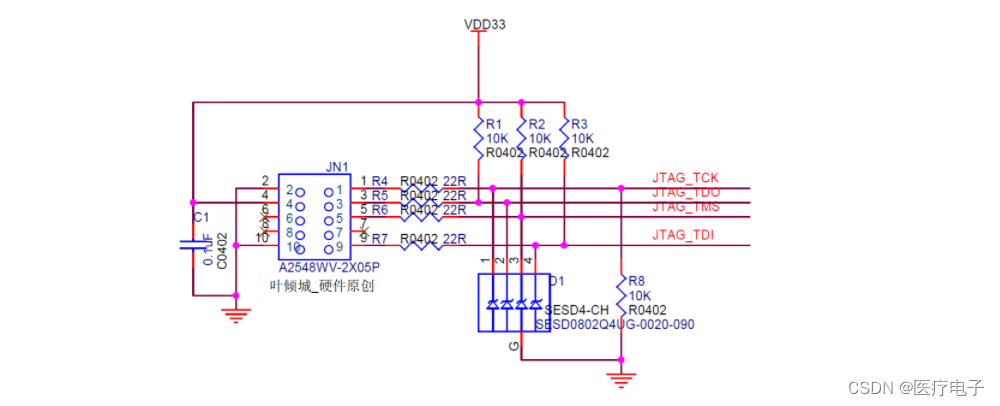

- 3 电路实战

- 3.1 Xilinx

- 3.2 ALTERA ------USB blaster

1 简介

JTAG(Join Test Action Group)的中文名称为联合测试工作组,是一种国际标准测试协议,主要用于芯片内部测试:验证设计和PCB测试。现在目前市面上的很多产品都支持JTAG协议(DSP、FPGA、CPLD、ARM等)。

JTAG接口通过4/5引脚连接到芯片上,这些引脚分别是:

| 网络 | 名称 | 描述 |

|---|---|---|

| TCK | 测试时钟输入 | 数据时钟输入 |

| TDI | 测试数据输入 | 数据通过 TDI 引脚输入 JTAG 接口 |

| TDO | 测试数据输出 | 数据通过 TDO 引脚从 JTAG 接口输出 |

| TMS | 测试模式选择 | TMS 用来设置 JTAG 接口处于某种特定的测试模式 |

| TRST | 为测试复位(可选) | 输入引脚,低电平有效。 |

1.1 JTAG分类

- 一类用于测试芯片的电气特性,检测芯片是否有问题

- 一类用于 Debug:一般支持 JTAG 的 CPU 内都包含了这两个模块。

一个含有 JTAG Debug 接口模块的 CPU,只要时钟正常,就可以通过 JTAG接口访问 CPU 的内部寄存器和挂在 CPU 总线上的设备,如 FLASH,RAM,SOC等内置模块的寄存器,像 UART,Timers,GPIO 等等的寄存器。上面说的只是 JTAG 接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。

上电时序

JTAG 电路的时序如图所示,所有基于 JTAG 的操作都必须同步于 JTAG时钟信号 TCK。在 TCK 的上升沿读取或输出有效数据,有严格的建立、保持时间要求,因此一般情况下 JTAG 的时钟不会太高。

1.2 ARM调试器

PIN序定义:

| PIN | SINGLE NAME | I/O DIAGRAM |

|---|---|---|

| 1 | VTREF | F |

| 2 | NC | NA |

| 3 | nTRST | D |

| 4 | GND | H |

| 5 | TDI | B |

| 6 | GND | H |

| 7 | TMS/SWDIO | B/C |

| 8 | GND | H |

| 9 | TCK/SWCLK | B |

| 10 | GND | H |

| 11 | RTCK | A |

| 12 | GND | H |

| 13 | TDO/SWO | A |

| 14 | GND | H |

| 15 | nSRST | E |

| 16 | GND | H |

| 17 | DBGRQ | B |

| 18 | GND | H |

| 19 | DBGACK | A |

| 20 | GND | H |

实物照片如图所示:

2 设计要点

-

TDI,TMS 是输入,上拉是为了在没有连接下载线的时候,给一个电平,同时提高信号的建立速度。

-

PCB 建库的需注意添加防呆标志,防止接反。

-

加上 ESD 保护芯片。

3 电路实战

3.1 Xilinx

3.2 ALTERA ------USB blaster

JTAG:JTAG 是直接烧到 FPGA 里面的。由于是 SRAM 断电后要重烧,AS 是烧到 FPGA 的配置芯片里保存的,每次上电就写到 FPGA 里。一般情况下,Cyclone II 开发板上应该有两种下载模式,AS 和 JTAG。AS 就是下载.pof 文件到 EPCS 中。而 JTAG 就是下载.sof 文件到 FPGA 中的RAM 中。//

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-C36KSwFV-1669636568318)(硬件电路设计.assets/image-20221128185545030.png)]](https://img-blog.csdnimg.cn/55c90f73d7b54c169750692721d6e34f.png)

![[附源码]Python计算机毕业设计Djangospringboot作业管理系统](https://img-blog.csdnimg.cn/a644c1d589b64cd084cf39149307783a.png)

![[附源码]计算机毕业设计springboot动物保护协会网站](https://img-blog.csdnimg.cn/b7554b4a21fc4ffcac849abfdeca9b94.png)