(一)CPU 的功能和组成

-

CPU 的功能

Ⅰ 概述:当程序指令装入内存储器后,CPU 用来自动完成取指令和执行指令的任务。

Ⅱ CPU 的功能:①指令控制 ②操作控制 ③时间控制 ④数据加工

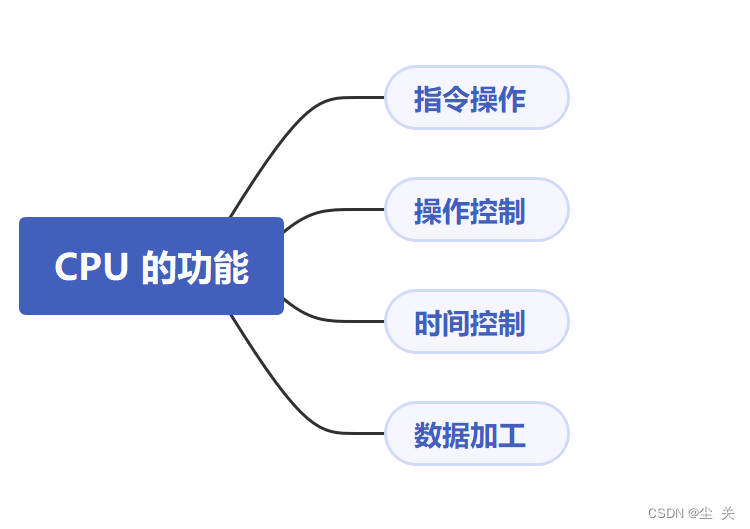

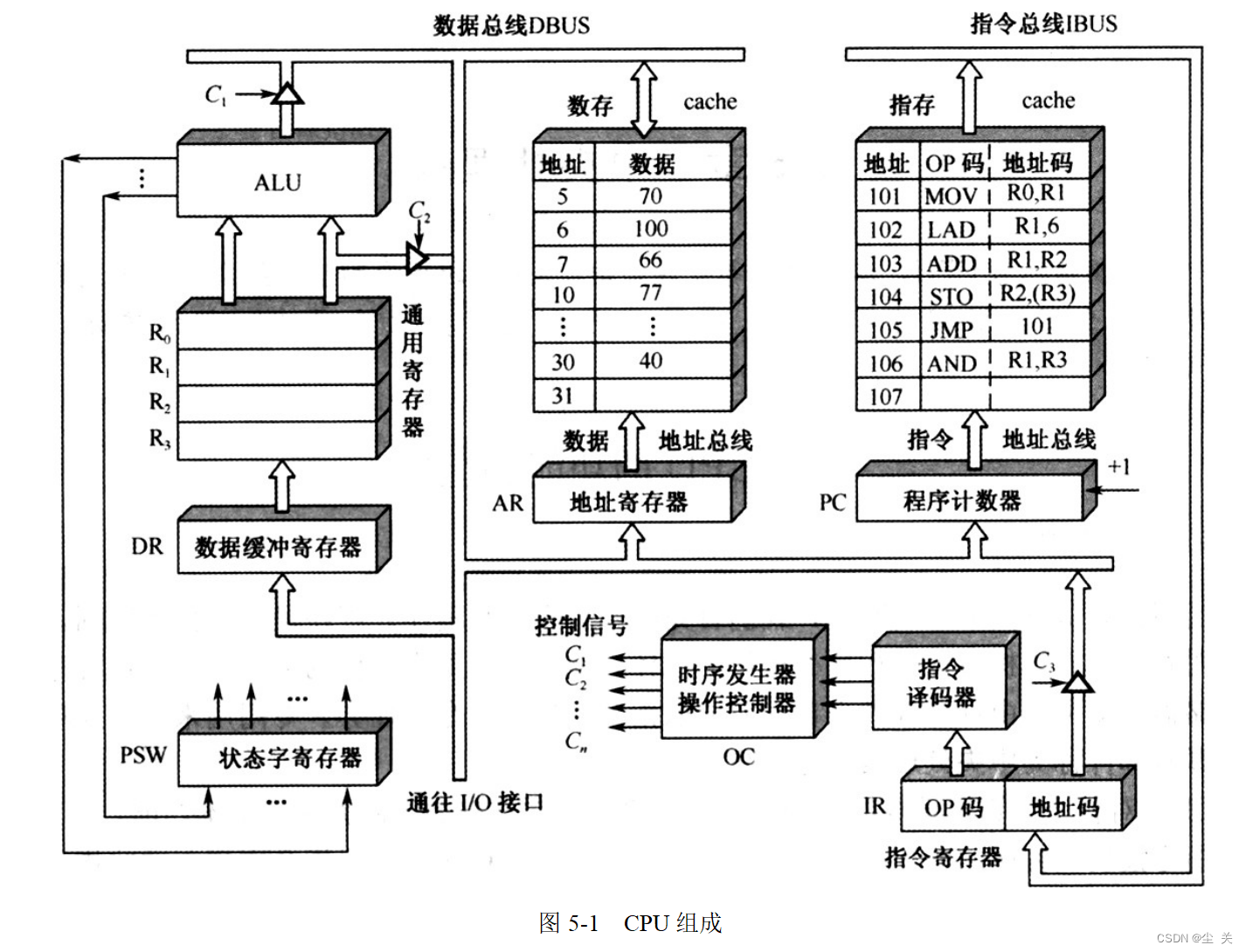

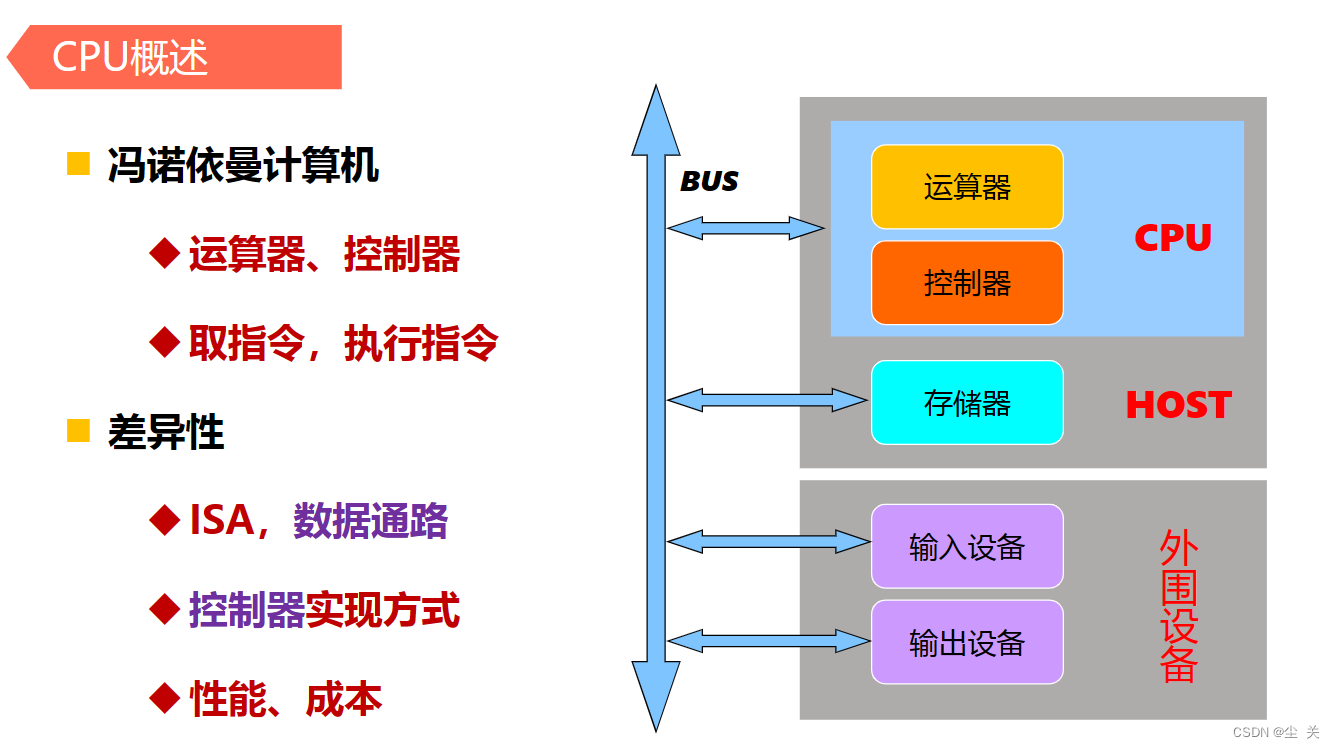

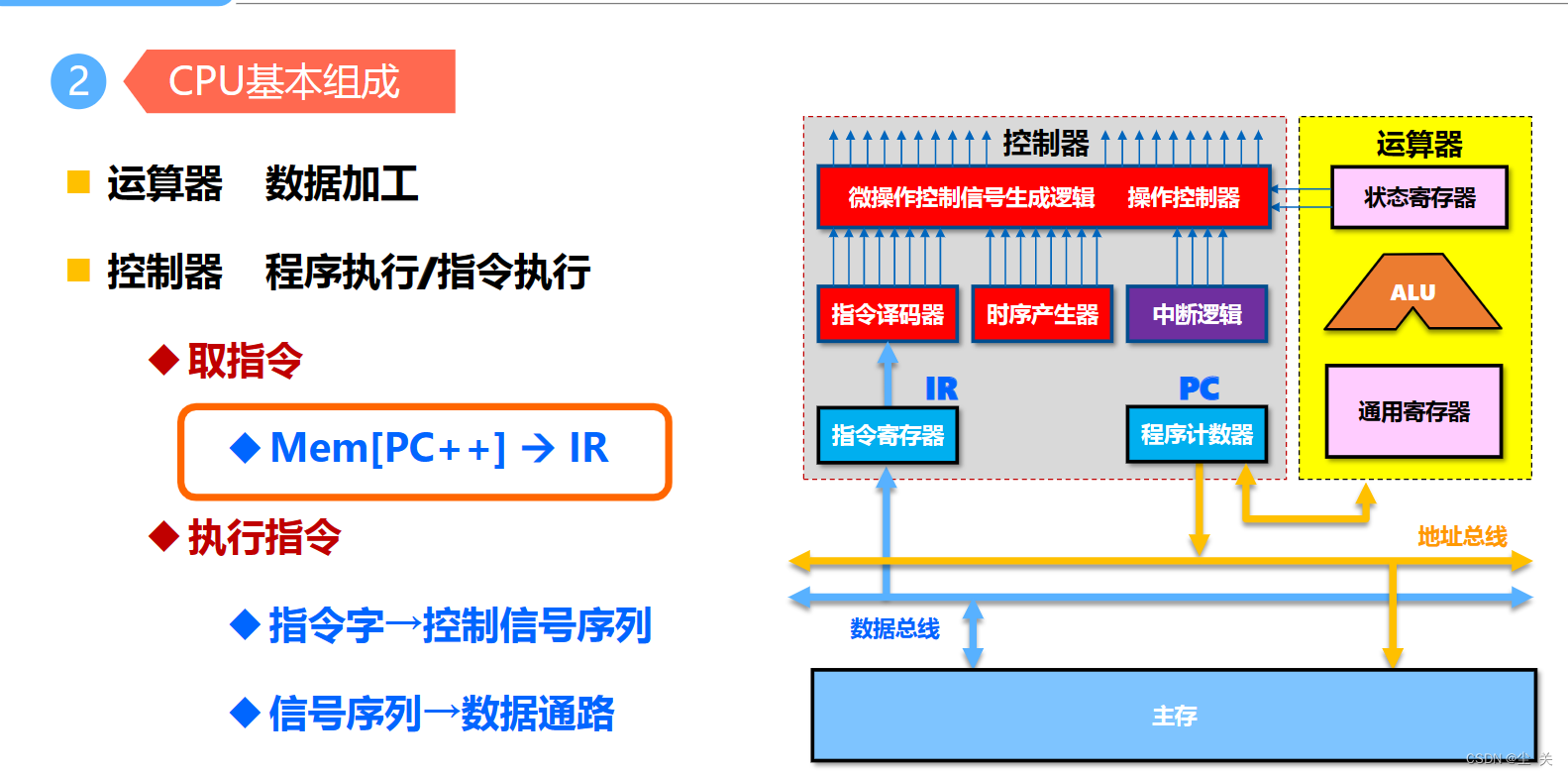

2.CPU 的基本组成

CPU 的基本部分为运算器、cache、控制器三大部分。 其中控制器由程序计数器、指令寄存器、指令译码器、时序产生器和操作控制器组成,运算器由算术逻辑单元(ALU)、通用寄存器、数据缓冲寄存器 DR 和状态条件寄存器 PSW 组成。

3.CPU 中的主要寄存器

CPU 中至少要有六类寄存器,如图 5-1 所示。这些寄存器用来暂存一个计算机字,根据需要,可以扩充其数目。

⑴数据缓冲寄存器(DR)

数据缓冲寄存器用来暂存算数逻辑单元(ALU)的运算结果,或由数据存储器读出的数据字,或来自外部接口的数据字。

缓冲寄存器的作用是:

①作为 ALU 运算结果和通用寄存器之间信息传送中时间上的缓冲;

②补偿 CPU 和内存、外围设备之间在操作速度上的差别。

⑵指令寄存器(IR)

指令寄存器用来保存当前正在执行的一条指令。当执行一条指令时,先把它从指令 cache 存储器(简称指存) 中读出,然后再传送至指令寄存器。

⑶ 程序计数器(PC)

程序计数器用来确定下一条指令的地址,程序若是顺序执行的,则对 PC 加 1;若遇到转移指令,后继指令的地址(即 PC 的内容)必须从指令寄存器中的地址字段取得。

⑷ 数据地址寄存器(AR)

数据地址寄存器(AR)用来保存当前 CPU 所访问的数据 cache 存储器单元(简称数存)中的地址。由于要对存储器阵列进行地址译码,故必须使用地址寄存器来保持地址信息,直到一次读/写操作完成为止。

⑸通用寄存器

在 CPU 模型中,通用寄存器是当 ALU 执行算术或逻辑运算时,为 ALU 提供一个工作区。目前 CPU 的通用寄存器数量很多,需要在指令格式中对寄存器号加以编址。

⑹状态字寄存器(PSW)

状态字寄存器(PSW)保存由算术指令和逻辑指令运算或测试结果建立的各种条件代码,如运算结果进位标志(C),溢出标志(V),零标志(Z),负标志(N)以及中断和系统工作状态等信息。

4.操作控制器与时序产生器

⑴ 操作控制器

操作控制器根据指令操作码和时序信号,产生各种操作控制信号,以便正确地选择数据通路,把有关数据打入到一个寄存器,从而完成取指令和执行指令的控制。根据设计方法不同,操作控制器可分为时序逻辑型和存储逻辑型两种:

①硬布线控制器

硬布线控制器采用时序逻辑技术实现;

②微程序控制器

微程序控制器采用存储逻辑技术实现。

⑵ 时序产生器

操作控制器产生的控制信号必须定时,为此必须有时序产生器。时序产生器的作用,就是对各种操作信号实施时间上的控制。

二、指令周期

-

指令周期的基本概念

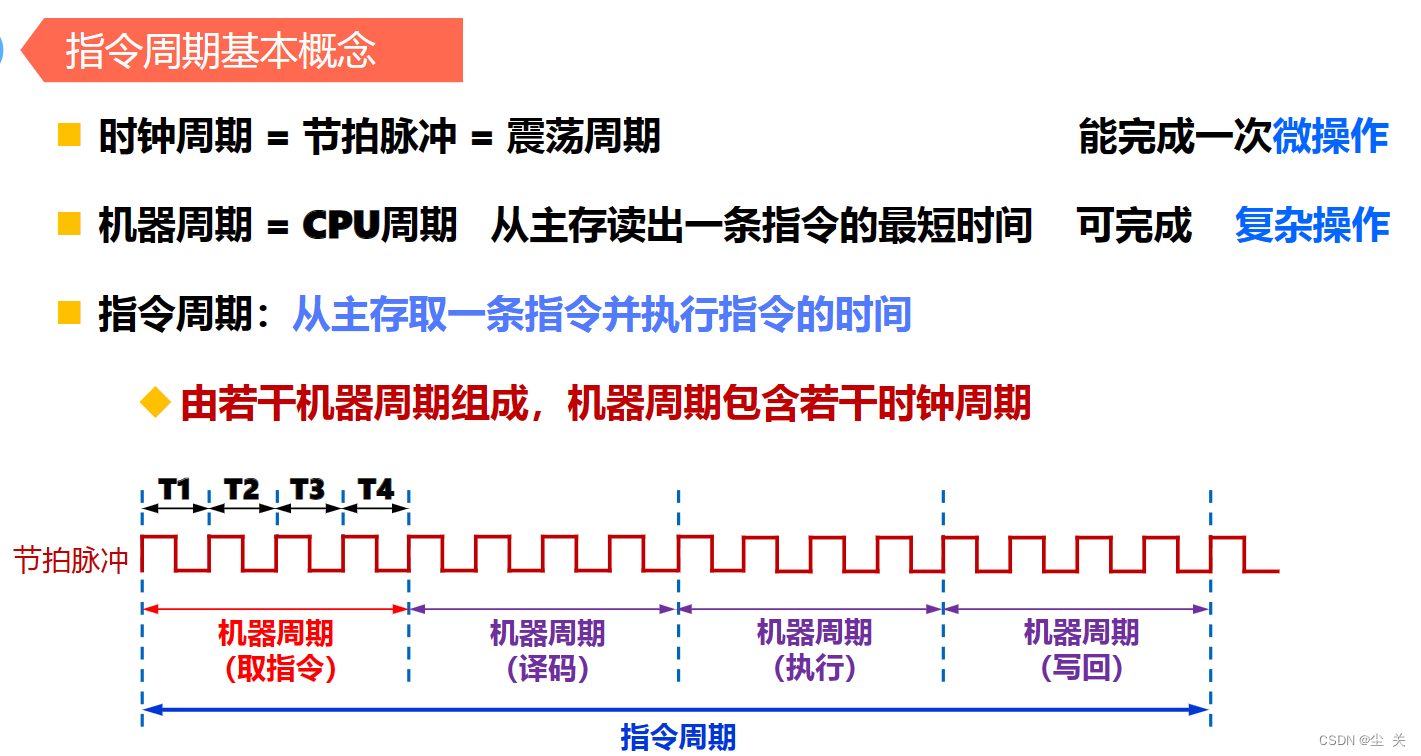

⑴ 指令周期的概念

指令周期是指取出一条指令并执行这条指令所花的时间。采用定长 CPU 周期的指令周期示意 所示,其中 T 周期称为节拍脉冲。

⑵ 单周期、多周期

单周期,就是在一个 CPU 周期中完成取指和执行操作(少数指令可实现)。大多数指令需要在多个 CPU 周期中完成指令周期的全部操作。

2.MOV 指令的指令周期

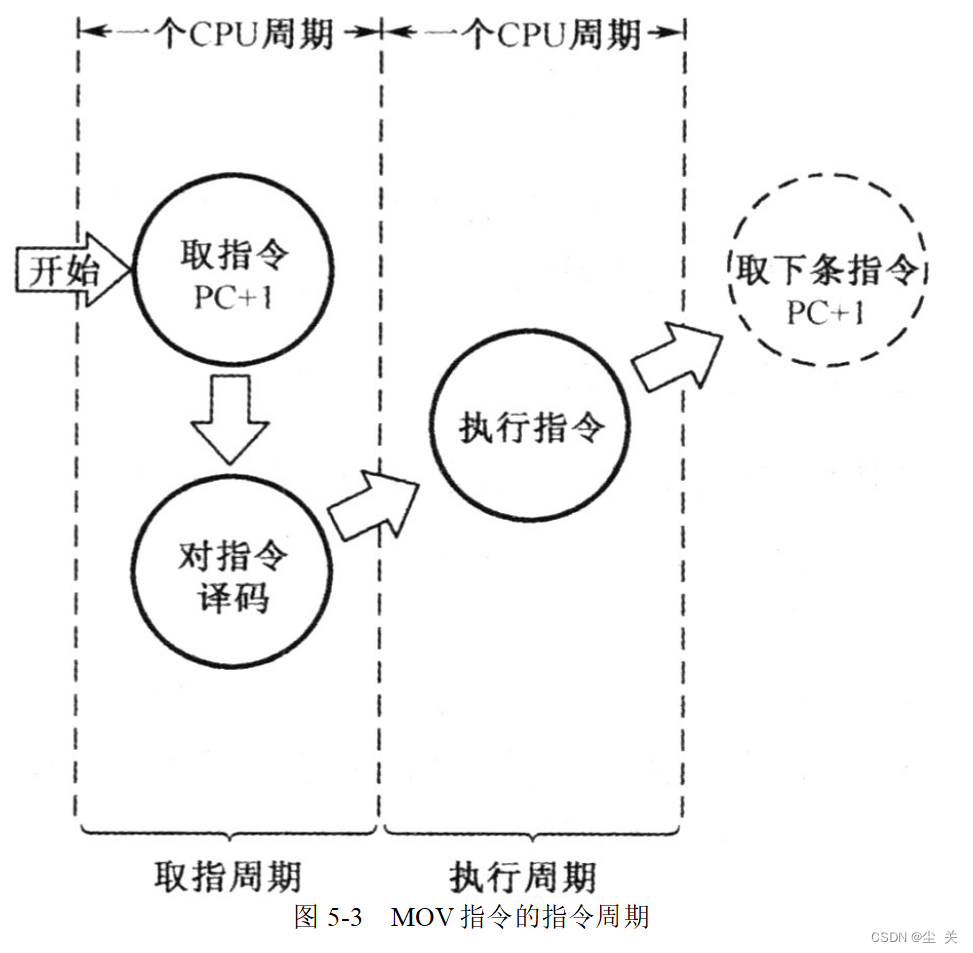

⑴ MOV 指令的指令周期

MOV 是一条 RR 型指令,其指令周期如图 5-3 所示。

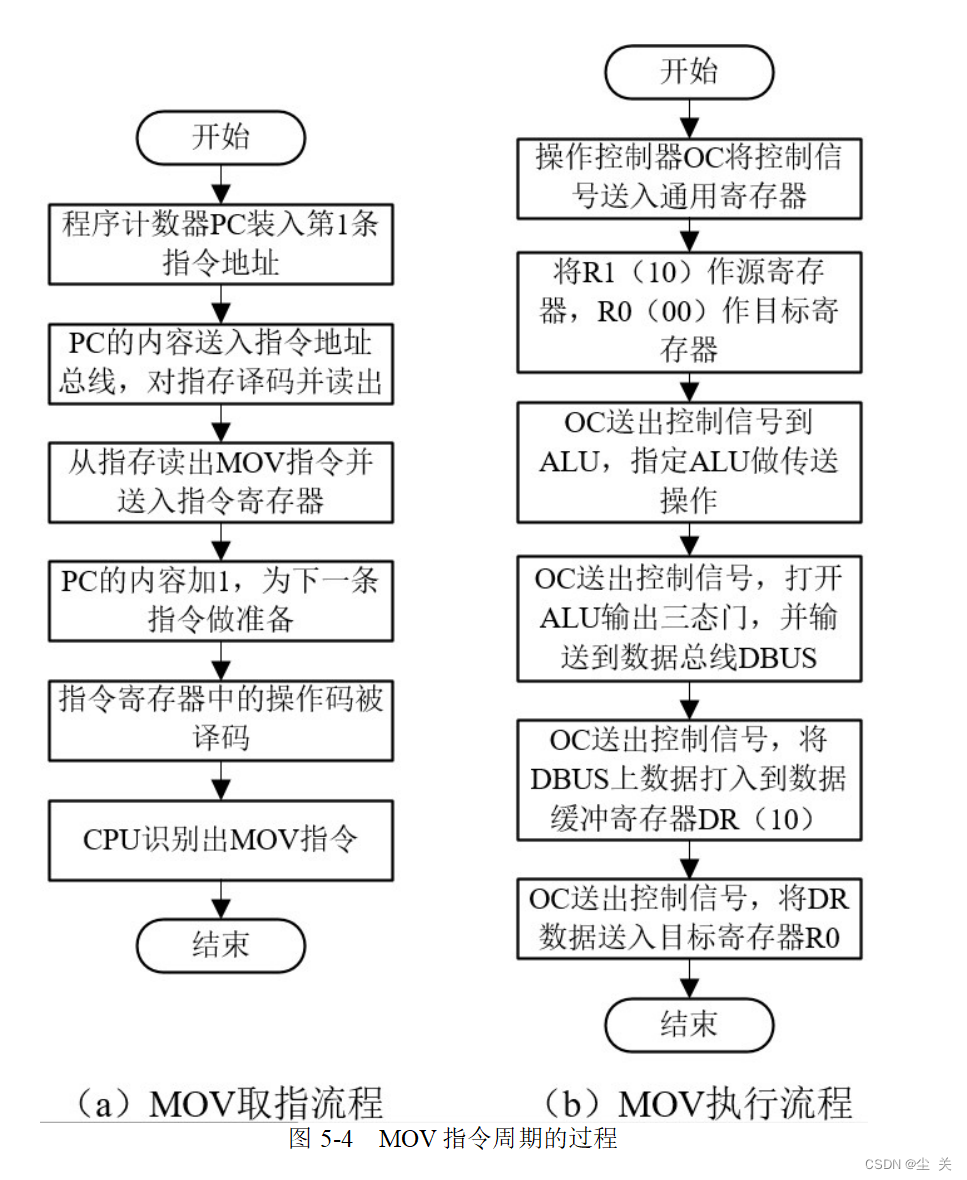

⑵ MOV 指令周期的过程

设 MOV 指令操作为 MOV R0,R1,则其取指周期及执行周期流程如图 5-4 所示。

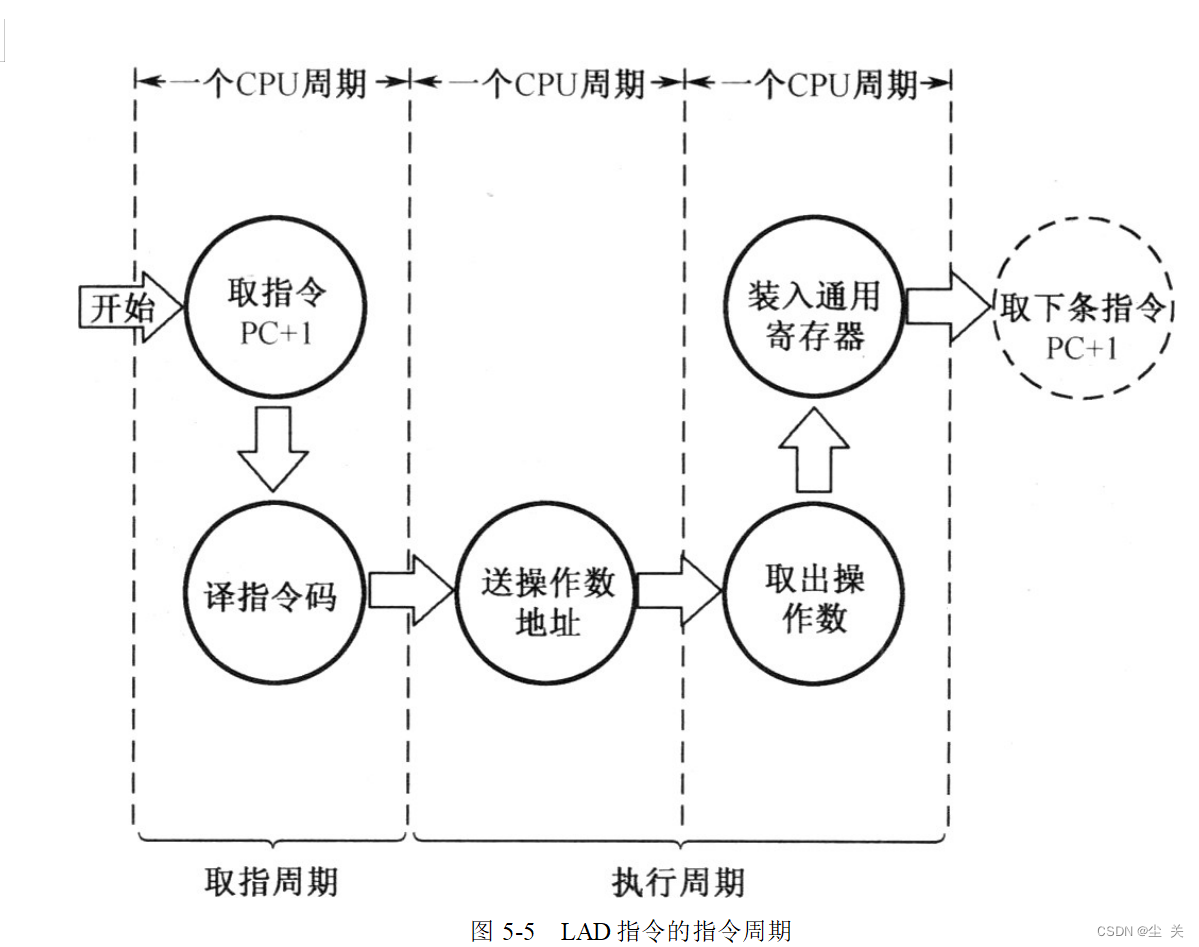

3.LAD 指令的指令周期

⑴ LAD 指令的指令周期

LAD 是一条 RS 型指令,其指令周期如图 5-5 所示,数据总线 DBUS 上分时进行了地址传送和数据传送,所以需要 2 个 CPU 周期。

⑵ LAD 指令周期的过程

设 LAD 指令为 LAD R1,6,则取指周期和 MOV 相同,其执行周期流程如图 5-6 所示。

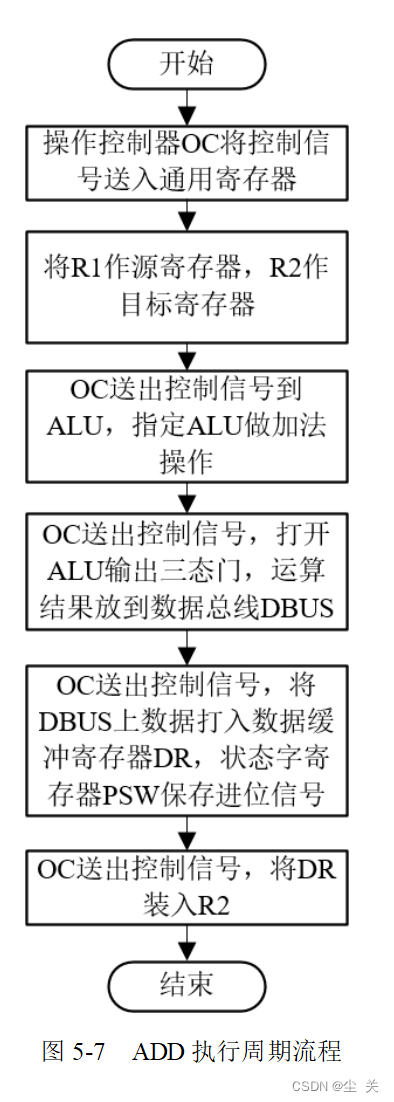

4.ADD 指令的指令周期

ADD 指令是RR 型指令,在运算器中用两个寄存器 R1 和 R2 的数据进行加法运算。整个指令周期为两个 CPU周期。取指周期过程和 MOV 相同,设 ADD 指令为 ADD R1,R2,执行周期流程如图 5-7 所示。

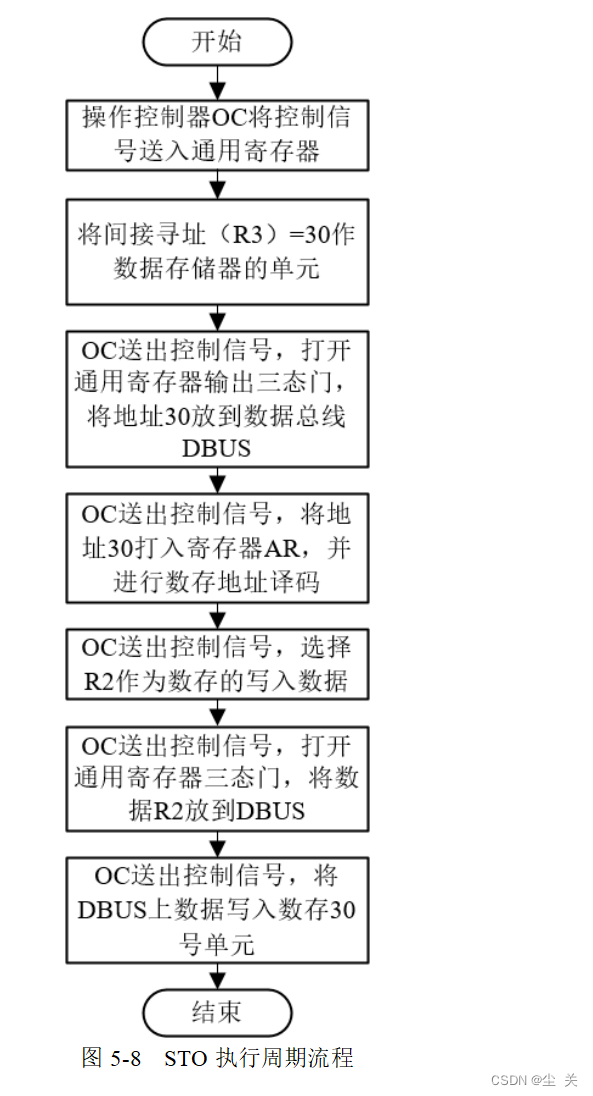

5.STO 指令的指令周期

STO 指令是 RS 型指令,一次访问指存,一次访问数存,故指令周期需 3 个 CPU 周期,其中执行周期为 2个 CPU 周期,其取指周期流程和 MOV 相同,设 STO 指令为 STO R2,R(3),则执行周期流程如图 5-8 所示。

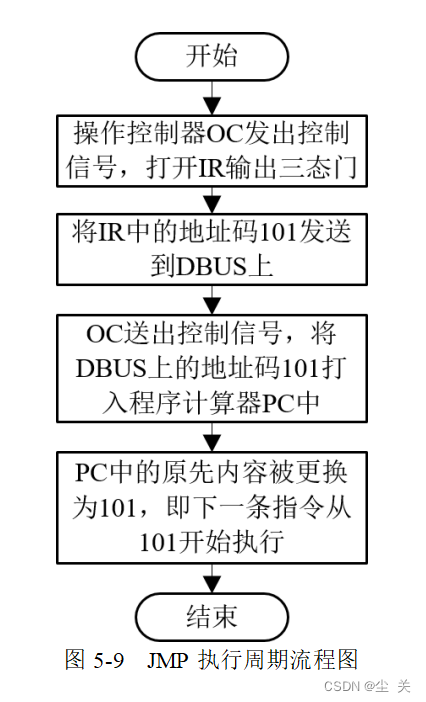

6.JMP 指令的指令周期

JMP 指令是一条无条件转移指令,用来改变程序的执行顺序。指令周期为两个 CPU 周期,其中取指周期流程与 MOV 相同,设 JMP 指令为 JMP 101,则其执行周期流程如图 5-9 所示。

7.用方框图语言表示指令周期

一个方框代表一个 CPU 周期,除了方框以外,还需要一个菱形符号,用来表示某种判别或测试,不过时间上它依附于紧接它的前面一个方框的 CPU 周期,而不单独占用一个 CPU 周期。

上述五条经典指令的方框图语言表示如图 5-10 所示。

三、时序产生器和控制方式

- 时序信号的作用和体制

⑴时序信号的作用

计算机能够准确、迅速、有条不紊地工作,正是因为在 CPU 中有一个时序信号产生器。

⑵时序信号的基本体制

①电位-脉冲体制

②主状态-节拍电位-节拍脉冲体制

硬布线控制器中,时序信号往往采用主状态周期-节拍电位-节拍脉冲三级体制。

③电位-节拍体制

在微程序控制器中,时序信号比较简单,一般采用节拍电位-节拍脉冲二级体制。

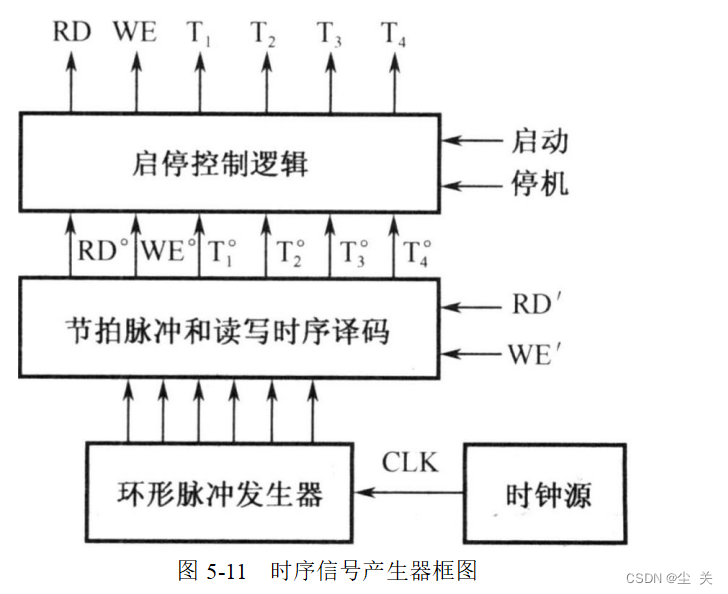

2.时序信号产生器

微程序控制器的结构图如图 5-11 所示,其时序信号产生器相对简单,但各类时序信号产生器的基本结构都是相似的。

⑴时钟源

时钟源用来为环形脉冲发生器提供频率稳定且电平匹配的方波时钟脉冲信号,通常由石英晶体振荡器和与非门组成的正反馈振荡电路组成。

⑵环形脉冲发生器

环形脉冲发生器的作用是产生一组有序的间隔相等或不等的脉冲序列,以便通过译码电路来产生最后所需的节拍脉冲。为了在节拍脉冲上不带干扰毛刺,环形脉冲发生器通常采用循环移位寄存器形式。

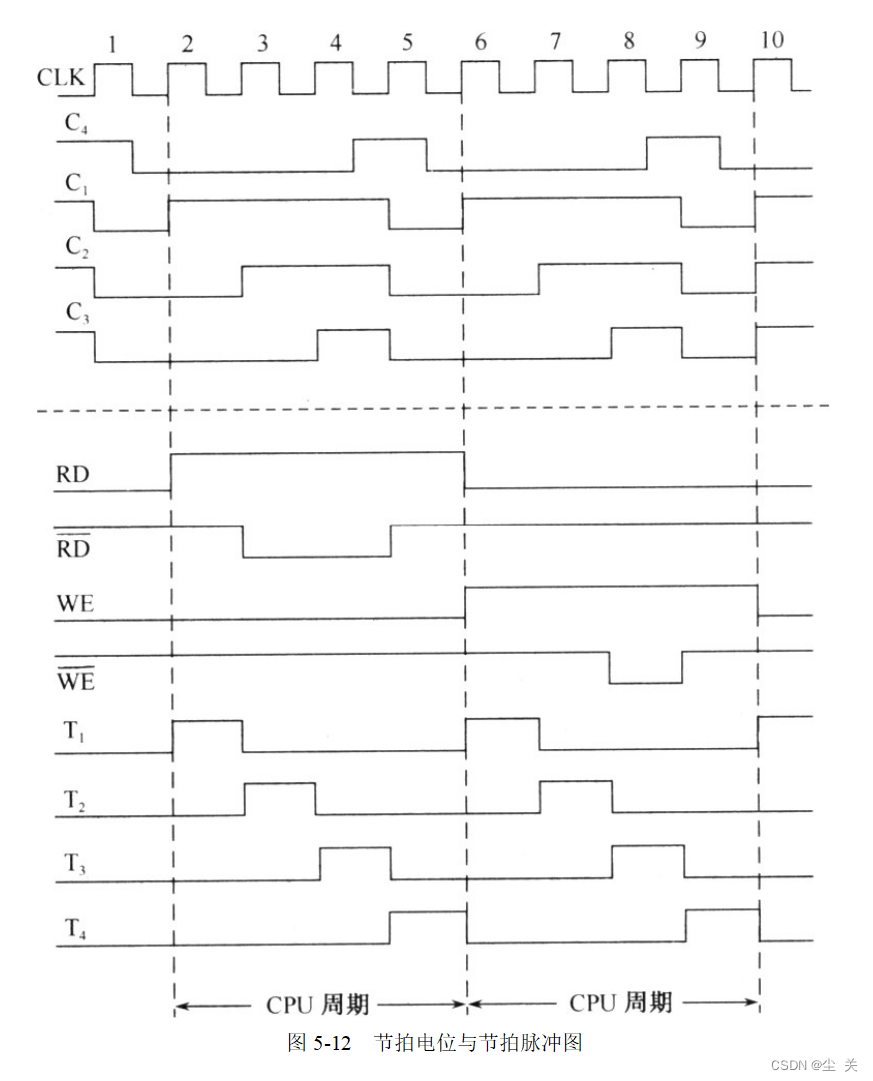

⑶节拍脉冲和存储器读/写时序

通过环形脉冲发生器产生的输出(C1、C2、C3、C4)经过译码组合后,形成具有先后关系的四个等间隔的节拍脉冲(T1、T2、T3、T4);读/写控制信号与环形脉冲发生器产生的输出译码组合产生读/写时序。节拍电位由时序产生器本身产生,通常为一个 CPU 周期的时间。

⑷启停控制逻辑

通过启停控制逻辑禁止和允许时序产生器向 CPU 发出工作所需的节拍脉冲和读/写时序。节拍电位与节拍脉冲图如图 5-12 所示。

3.控制方式

控制不同操作序列时序信号的方法,称为控制器的控制方式。

⑴同步控制方式

①采用完全统一的机器周期执行各种不同的指令

②采用不定长机器周期

③中央控制与局部控制结合

⑵异步控制方式

异步控制方式的特点是:每条指令或操作控制信号需要多少时间就占用多少时间。

⑶联合控制方式

联合控制方式为同步控制和异步控制相结合的方式。

四、微程序控制器

-

微程序控制原理

⑴概述

在计算机系统中,微程序设计技术是利用软件方法来设计硬件的一门技术。

⑵微命令和微操作

一台数字计算机基本上可以划分为两大部分——控制部件和执行部件。控制器是控制部件,而运算器、存储器、外围设备相对控制器来讲,是执行部件。

①微命令与微操作的联系

控制部件通过控制线向执行部件发出各种控制命令,通常把这种控制命令称为微命令,而执行部件接受微命令后所进行的操作称为微操作。

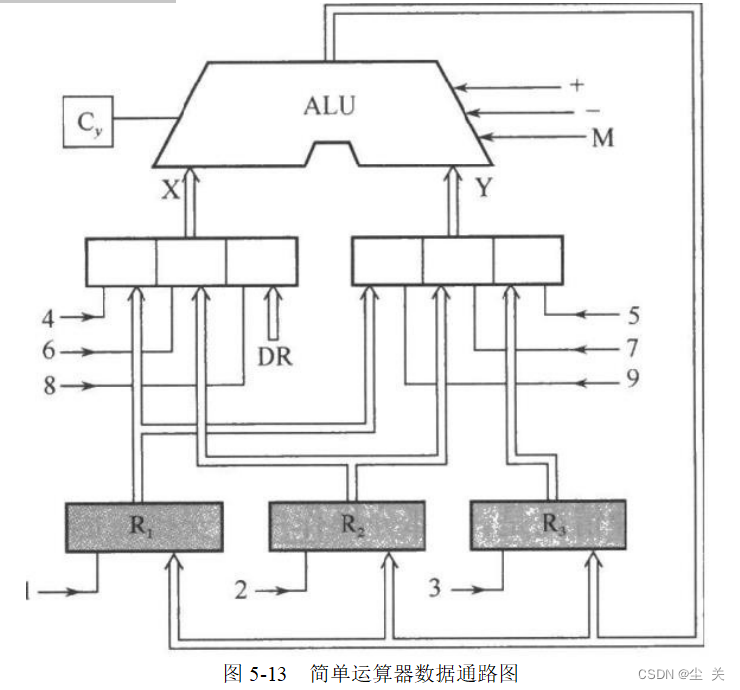

②运算器的工作过程

一个简单运算器模型如图 5-13 所示。其中 4、6、8 是互斥的,5、7、9 是互斥的,而 1、2、3 是相容的,通过控制 1~9 来控制数据的流动。

⑶微指令和微程序

一个 CPU 周期中,一组实现一定操作功能的微命令的组合,构成一条微指令,许多条微指令组成的序列为微程序。

具体的微指令结构如图 5-14 所示,微指令字长为 23 位,它由操作控制和顺序控制两大部分组成。

图 5-14 所示的控制信号都是节拍电位信号,其持续时间都为一个 CPU 周期,LDR1′,LDR2′,LDR3′三个信号作用为将运算结果打入寄存器,因此应该将其与节拍脉冲 T 相与来得到 LDR1~LDR3。

⑷微程序控制器原理框图

微程序控制器原理框图如图 5-15 所示

①控制存储器

读出一条微指令并执行这条微指令的时间总和称为一个微指令周期;控制存储器的字长就是微指令字的长度。

②微指令寄存器

微指令寄存器包括微地址与微命令寄存器,其中微地址寄存器决定将要访问的下一条微指令的地址,而微命令寄存器则保存一条微指令的操作控制字段和判别测试字段的信息。

③地址转移逻辑

地址转移逻辑负责自动完成修改微地址的任务。

⑸CPU 周期与微指令周期的关系

在串行方式的微程序控制器中,微指令周期等于读微指令的时间与执行微指令的时间之和。为了保证整个机器控制信号的同步,可以将一个微指令周期设计得恰好和 CPU 周期相等。

⑹机器指令与微指令的关系

①一条机器指令所完成的操作划分成若干条微指令来完成,由微指令进行解释和执行。

②从指令与微指令、程序与微程序、地址与微地址的一一对应关系来看,前者与内存储器有关,后者与控制存储器有关。

2.微程序设计技术

⑴ 微命令编码

①直接表示法:操作控制字段中的每一位代表一个微命令。

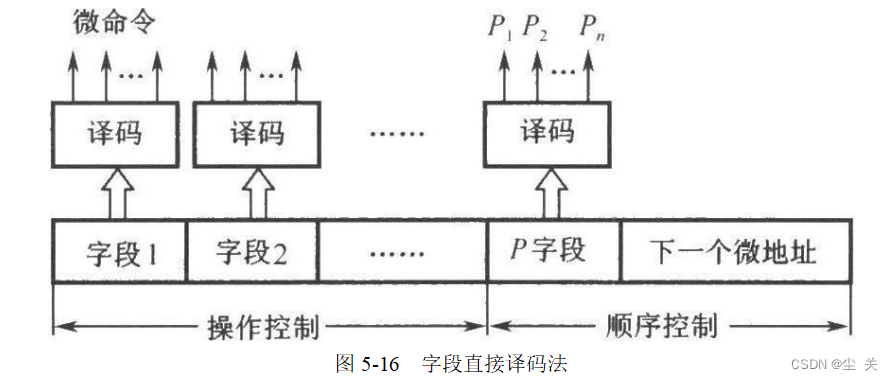

②编码表示法:把一组相斥性的微命令信号组成一个小组(即一个字段),然后通过小组译码器对每一个微命令信号进行译码,译码的输出结果作为操作控制信号,其微指令结构如图 5-16 所示,其优点是可以用较小的二进制信息位表示较多的微命令信号。

③混合表示法:把直接表示法与字段编码法混合使用。

⑵微地址形成方法

微指令执行的顺序控制问题,实际上是如何确定下一条微指令的地址问题。

①计数器方式

通过计数器方式产生微地址的方法同用程序器计数来产生机器指令地址的方法类似。

②多路转移方式

顺序控制字段中,若“状态条件”有 n 位标志,可实现微程序 2n 路转移,涉及微地址寄存器的 n 位。

⑶ 微指令格式

①水平型微指令一次能定义并执行多个并行操作微命令的微指令,称为水平型微指令。水平型微指令的一般格式如下:

| 控制字段 | 判别测试字段 | 下地址字段 |

按照控制字段的编码方法不同,水平型微指令又分为三种:

a.全水平型微指令;

b.字段译码法水平型微指令;

c.直接和译码相混合的水平型微指令。

②垂直型微指令

微指令中采用微操作码编译法来设置微操作码字段,即微操作码规定微指令的功能,称为垂直型微指令。与水平型微指令相比,垂直型对应的微程序要长,但其微指令结构较短。

五、硬连线控制器

-

基本思想

(1)概述

硬连线控制器把控制部件看作产生专门固定时序控制信号的逻辑电路,它是一种由门电路和触发器构成的复杂树形逻辑网络,故称之为硬连线控制器。

⑵ 结构

硬连线控制器的结构方框如图 5-17 所示。

逻辑网络的输入信号有三个来源:

①指令操作码译码器的输出 Im;

②执行部件的反馈信息 Bj;

③时序产生器的时序信号,包括节拍电位信号 Mi 和节拍脉冲信号 Tk。

与微程序控制相比,硬连线控制的速度较快。其原因是微程序控制中每条微指令都要从控存中读取一次,影响速度,而硬连线控制主要取决于电路延迟。

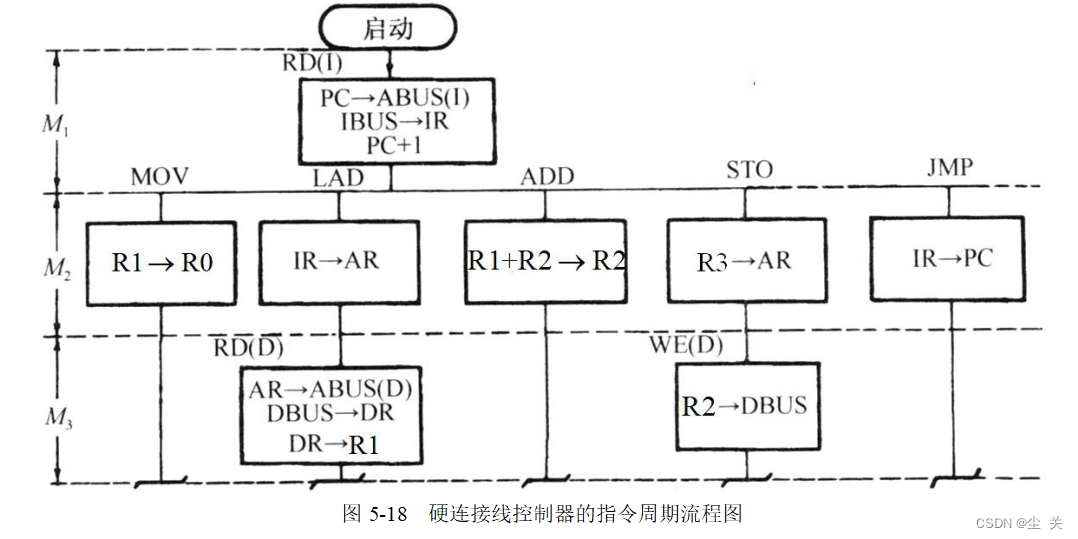

2.指令执行流程

一个机器指令对应一段微程序,而一个微指令周期则对应一个节拍电位。在用硬连线实现的操作控制器中, 时序产生器除了产生节拍脉冲信号,还应产生节拍电位信号,五条指令的指令周期流程如图 5-18 所示。

3.微操作控制信号的产生

在微程序控制器中,微操作控制信号由微指令产生,并且可以重复使用;在硬连线控制器中,微操作控制信号由布尔代数表达式描述的输出函数产生。

六、流水 CPU

1.并行处理技术

⑴ 并行性的含义

①一是同时性,指两个以上事件在同一时刻发生;

②二是并发性,指两个以上事件在同一时间间隔内发生。

⑵ 并行性的形式

①时间并行;

②空间并行;

③时间并行+空间并行。

2.流水 CPU 的结构

⑴ 流水计算机的系统组成

现代流水计算机的系统组成原理示意图如图 5-19 所示。

①CPU 的三级流水线

CPU 按流水线方式组织,通常包括三大部分:指令部件、指令队列、执行部件。这三个功能部件可以组成一个三级流水线,三大部分自身又用流水线构成。

②速度匹配的方法

为了解决执行段的速度匹配问题,通常采用并行的运算部件以及流水线的工作方式来解决:

a.将执行部件分为定点执行部件和浮点执行部件两个可并行执行的部分;

b.在浮点执行部件中,又分为浮点加法部件和浮点乘/除部件; c.浮点运算部件都以流水线方式工作。

⑵流水 CPU 的时空图

假设指令周期包含四个子过程:取指令(IF)、指令译码(ID)、执行运算(EX)、结果写回(WB),每个子过程称为过程段(Si),流水 CPU 中一个指令周期的任务分解如图 5-20(a)所示,非流水时空图如图 5-20(b)所示,而标量流水和超标量流水时空图如图 5-20(c)、5-20(d)所示。

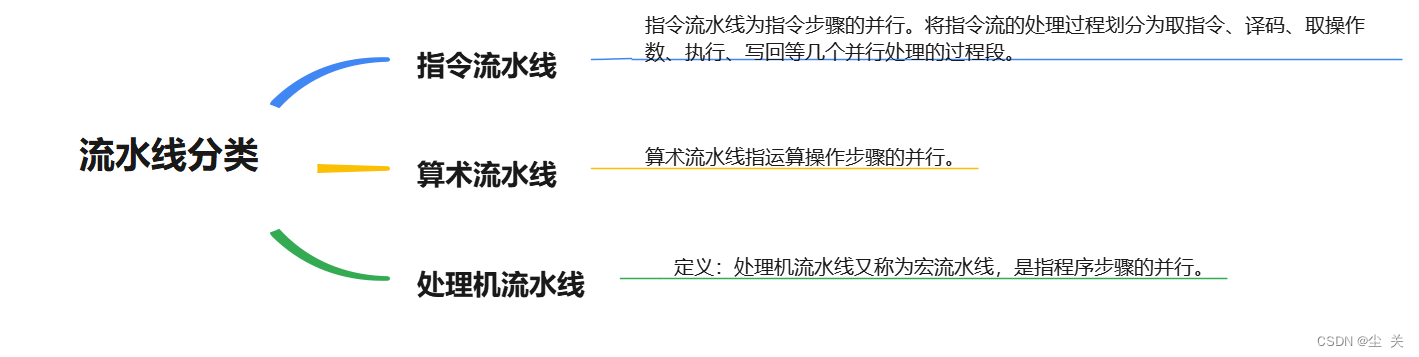

⑶流水线分类

一个计算机系统可以在不同的并行等级上采用流水线技术。常见的流水线形式有:

①指令流水线

指令流水线为指令步骤的并行。将指令流的处理过程划分为取指令、译码、取操作数、执行、写回等几个并行处理的过程段。

②算术流水线

算术流水线指运算操作步骤的并行。

③处理机流水线

处理机流水线又称为宏流水线,是指程序步骤的并行。

3.流水线中的主要问题

⑴ 资源相关冲突

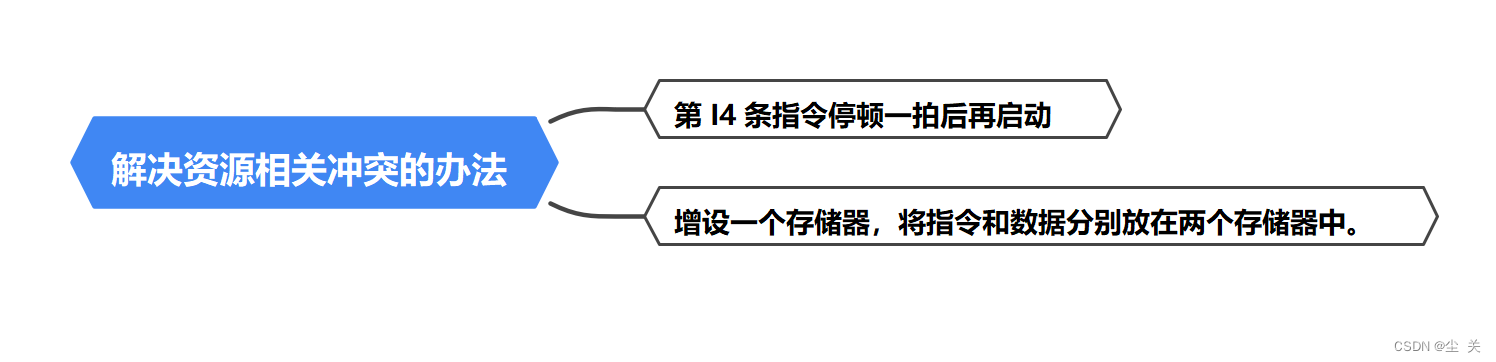

①概述

资源相关是指多条指令进入流水线后在同一机器时钟周期内争用同一个功能部件所发生的冲突。当数据和指令放在同一个存储器且只有一个访问口时,便发生两条指令争用存储器资源的相关冲突。

②解决冲突的办法

a.第I4 条指令停顿一拍后再启动;

b.增设一个存储器,将指令和数据分别放在两个存储器中。

⑵数据相关冲突

①概述

在一个程序中,如果必须等前一条指令执行完毕后,才能执行后一条指令,那么这两条指令就是数据相关的。

②解决冲突的办法

流水 CPU 的运算器中特意设置若干运算结果缓冲寄存器,暂时保留运算结果,以便于后继指令直接使用, 这称为“向前”或定向传送技术。

⑶控制相关冲突

①概述

控制相关冲突是由转移指令引起的。依据转移条件的产生结果,当执行转移指令时,可能顺序取下条指令, 也可能转移到新的目标地址取指令,从而使流水线发生断流。

②解决冲突的办法:

a.延迟转移法;

b.转移预测法。

![【论文阅读】[JBHI] VLTENet、[ISBI]](https://img-blog.csdnimg.cn/21f47ce9df0949a9bc686ce00d25bba0.png)