前言

世界各大主流闪存厂商,如美光、海力士、铠侠和长江存储积极致力于QLC的研发,并相继推出了QLC SSD 产品。随着技术的不断进步,人们普遍担心的QLC擦写寿命少正逐渐被改善。QLC SSD 成本是最大的优势,不指望说替代 TLC SSD, 替代 HDD 指日可待。

但因为 PLC NAND 本身的一些劣势, 对 NAND 闪存控制器(主控)带来了很大的挑战。

今天我们一起聊一聊?

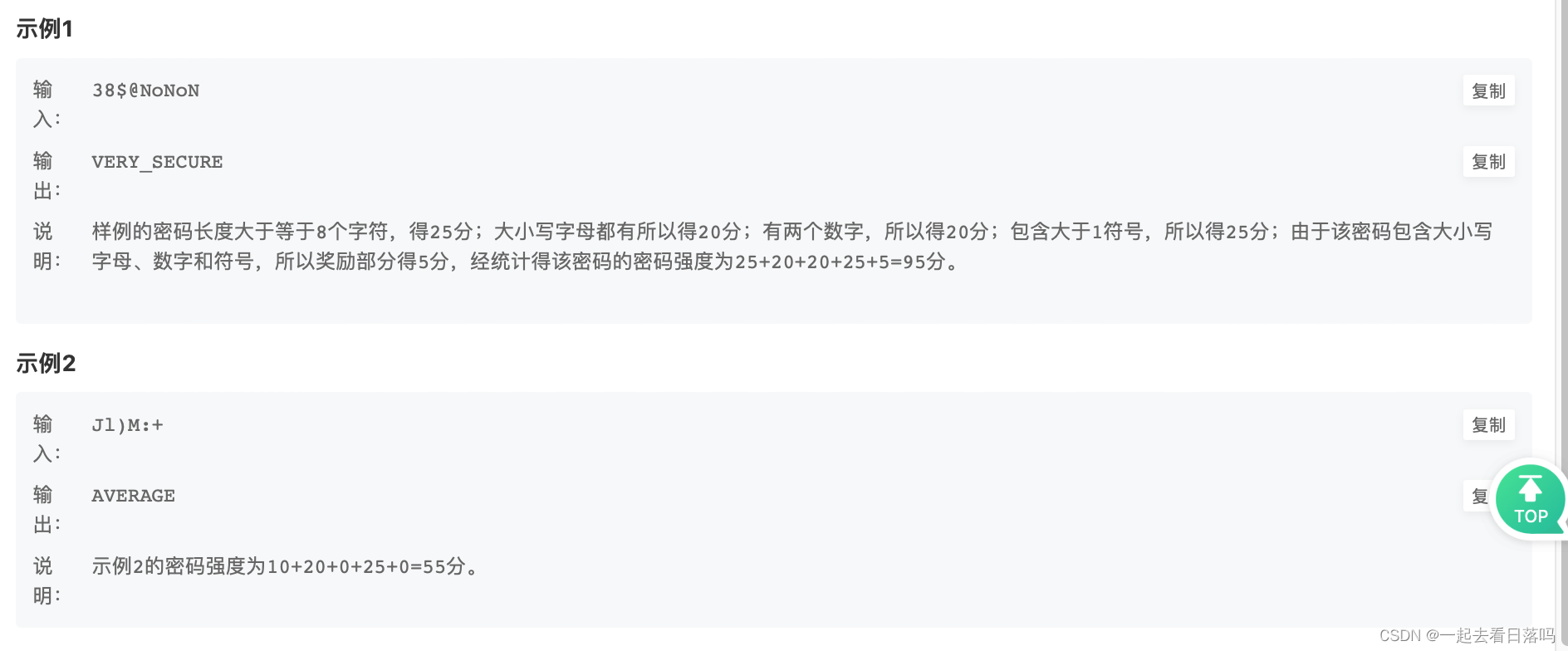

随着NAND Flash的制程越来越先进、单个Cell里面的bit数量不断增加。

NAND Flash由最初的SLC发展到目前的QLC,虽然存储密度获得了很大的提高,单位Bit的成本得到极大降低,但是也带来性能和可靠性缺陷。性能&可靠性对比是SLC>MLC>TLC>QLC,随着每个cell的bit数量的增加,读写寿命逐渐变短,速度变慢,能耗高,出错概率大。

1. 对芯片纠错能力要求更高

为什么随着NAND密度的增加,主控芯片纠错能力的重要性更大?

造成出错的主要原因是当每个cell(存储单元)存储多个bit时,相比SLC,存储单元之间的干扰就会增大。因此MLC,TLC乃至QLC对主控芯片和差错控制技术提出了更高的要求,而纠错技术也从BCH过渡到了LDPC。随着工艺的不断进步,下一代NAND存储单元所容纳的Bit数量会越来越多,对算法的纠错能力要求也会越来越高。

在高密度存储中,每个cell bit数量增加,互相干扰增大,擦写次数增加,存储结构中的氧化层会遭到破坏,捕获电子的能力越差,影响产品寿命,

一问如何解决QLC NAND 误码率?

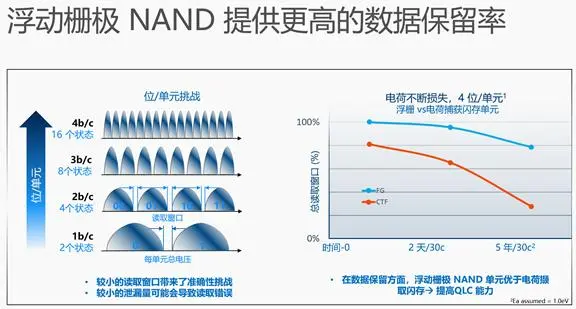

一方面闪存原厂利用浮栅技术,降低出错概率

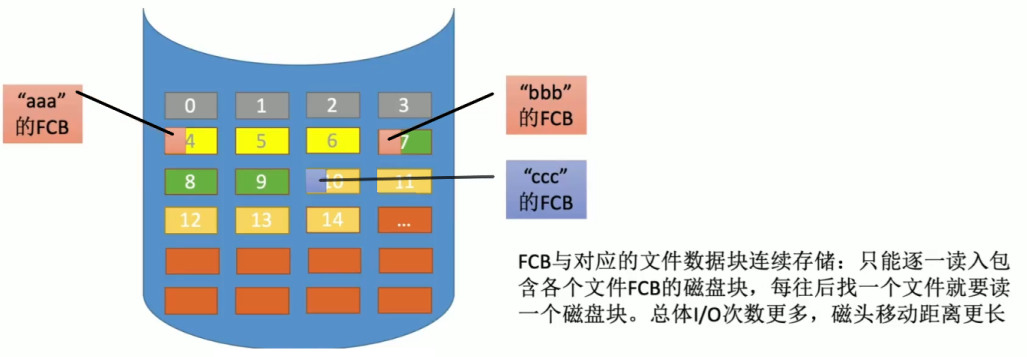

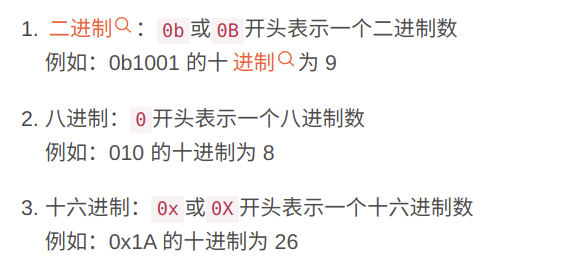

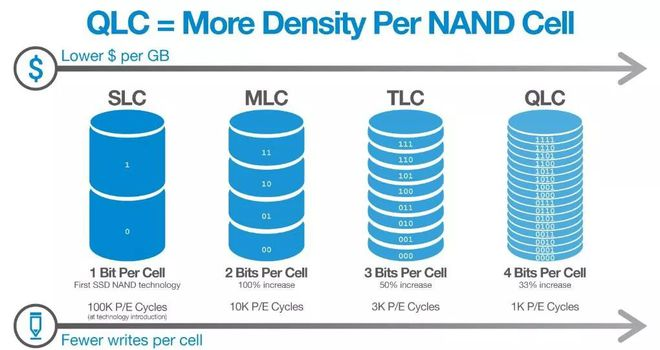

RWB (Read Window Budget,阈值电压窗口) 指标对于NAND可靠性至关重要。RWB越大越好,出错概率越小。上图展示了1b/c (1 bit/cell)一直到 4b/c (4 bit/cell)之间的差别,你会注意到位之间的差距越小,每个单元的位数越多。

然而,如果看看右侧的图表——其中对比了浮动栅极单元和电荷捕获单元两种技术的RWB——可以看到浮栅单元的RWB高于电荷捕获技术。RWB越高,数据保留周期就越长,可靠性越好,从而也更容易实现4b/c, 5b/c等技术的产品化。浮栅技术的RWB非常卓越,这大大提升了QLC的数据维持能力,减少误码率。

二问如何解决QLC NAND 误码率?

另一方面闪存主控有效的纠错编码, 提高纠错能力

TLC NAND 的主控芯片主要采用2K LDPC编码。 但QLC 误码率更大, 需要用到4K LDPC(低密度奇偶校验Low-Density Parity-Check)纠错技术。4K LDPC在同样的码率下(纠错码使用bit数量一样),实测4K LDPC纠错比2K方案降低UBER至少两个数量级以上,大大提高纠错性能。

不过在芯片中实现4K LDPC的难度还是很大的,如果不做优化,相当于至少2个2K LDPC,因此对主控芯片面积、功耗都有极大的挑战和要求。

正因为原厂持续不断的优化技术降低误码, 和主控厂家不断提升的纠错能力。 这才很好地加速QLC的商用化落地。

2. 更高并行度

SSD性能高的秘密就在于有很多个闪存芯片可以并行读写,虽然单个芯片带宽不高,芯片并行起来速度就可成倍增长,实现非常高的性能。

QLC 闪存芯片单颗容量会很大,同样是 1TB 的SSD, QLC 就不需要那么多颗,这就会产生一个严重的问题,一旦SSD内部没有这么多的闪存颗粒,并行度就会下降,导致性能上不去,这该怎么办?

目前闪存厂商在想办法让NAND Flash内部提升并行度。主要做法是Plane(平面)数目会增加。相较于目前主要是4个plane,长江存储的 QLC 达到了 6 Plane. 未来闪存有可能会有8个甚至16个plane。主控需要支持更多的 Plane 组合。

因为 Plane 还不能完全做到延迟(Latency)并行, Intel 发展了一项新技术,让Plane0/1 和 Plane 2/3 独立, 这样变成了两个 双 Plane, 这两个双 Plane 可以完全并行。这自然是一个先进技术,对了提高并行速度效果很明显, 但这也要闪存控制芯片 FTL 算法支持这样。

3. 支持更高的闪存接口速度

闪存芯片的接口速度也在日新月异,国际闪存原厂下一代闪存芯片接口将达到2400MT/s甚至更高。

我国自主的长江存储推出的128层QLC产品,接口速度达到1600MT/s,标志着我国闪存芯片的设计能力已达到世界先进水平。

QLC NAND 需要增加接口速度以支持使用PCIe 4.0和最终PCIe 5.0的下一代NVMe SSD应用,对主控芯片的主频和高频信号质量提出了更高的要求。

4. 其他挑战

QLC还有其他缺点:

- 写延迟是12ms,非常长

- 擦写次数通常只能达到2000

- Data Retention 问题

这些都需要通过主控技术进行补偿。

写延迟需要通过DRAM 缓存(或HMB技术借用主机内存缓存)提高速度。

擦写次数低, 要求主控的磨损均衡要更加优秀。

Data Retention 需要主控刷新数据。

不过我认为主控之前就有这些技术, 只是现在针对更极端的场景,要优化主控的管理算法, 更加适用 QLC NAND 的特点。

结语与展望

随着每个cell的bit数量的增加,读写寿命逐渐变短,速度变慢,能耗高,另外,一个主要的缺点是出错概率大。QLC NNAD 给闪存主控带来了很大的挑战,强大的低密度奇偶校验(LDPC)纠错对于NAND控制器来说至关重要。

QLC NAND 需要增加接口速度以支持使用PCIe 4.0和最终PCIe 5.0的下一代NVMe SSD应用,对主控芯片的频率和信号完整性提出了更高的要求。

但好在主控厂商已准备好了。慧荣、群联、英韧等都已推出了支持 QLC 的主控。这对于QLC SSD 的普及,有如神助。

QLC最有可能在数据中心有更大的应用场景,因其具有巨大的成本优势,尤其在海量数据的应用场景中。QLC本身容量大、成本低,因此使用了QLC SSD之后,存储密度更高,服务器集成度更高,这会极大地节省数据中心面积,进而节省运营成本。

参考

http://www.ssdfans.com/?p=113823

https://www.163.com/dy/article/EODB68AO0511DQFI.html