各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们说到信号的时序设计需要保证数据和时钟信号同步传输。今天我们开始学习电源完整性分析需要考虑什么?

PI分析概述

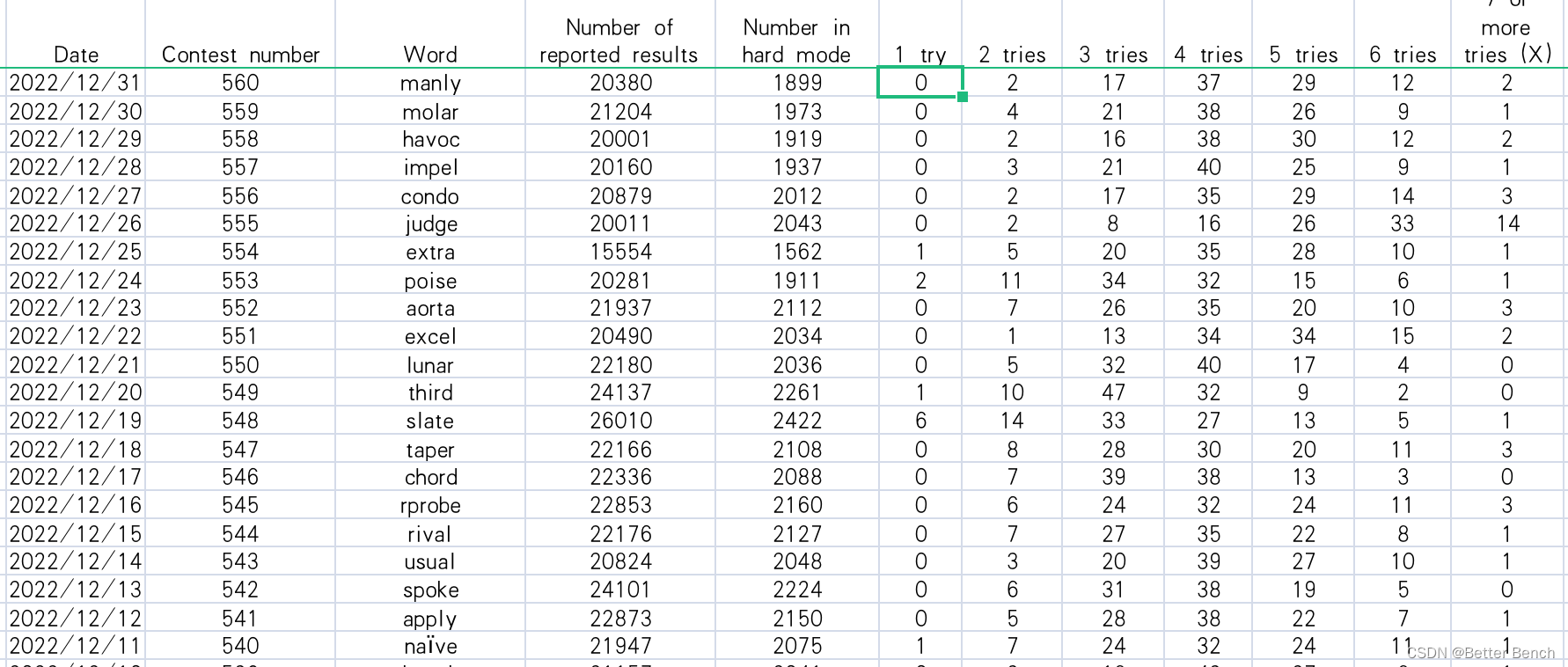

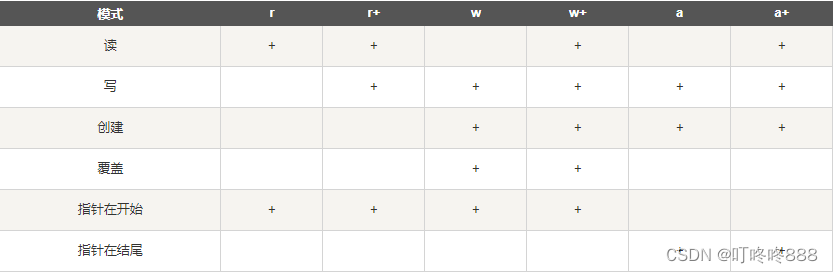

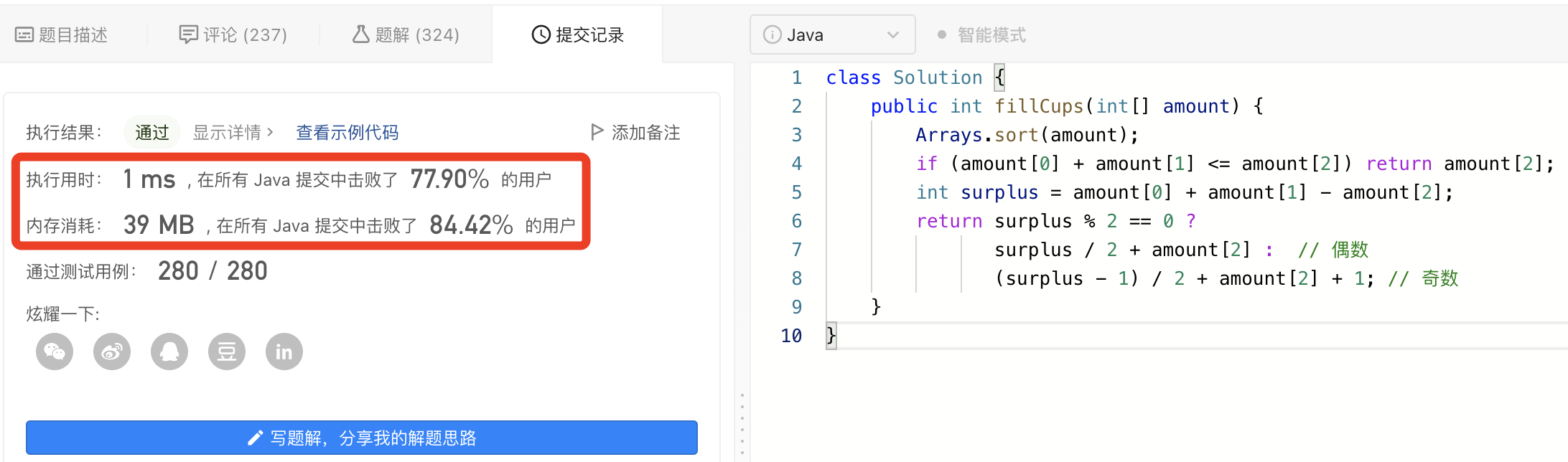

电源完整性研究的是电源分配网络(Power Distribution Network, PDN),包含电源的源头、供电模块VRM、PCB上的储能电容和去耦电容、PCB上的电源和地平面、芯片封装内的电源和地网络、Die上的电容,如下图所示:

电源分配网络

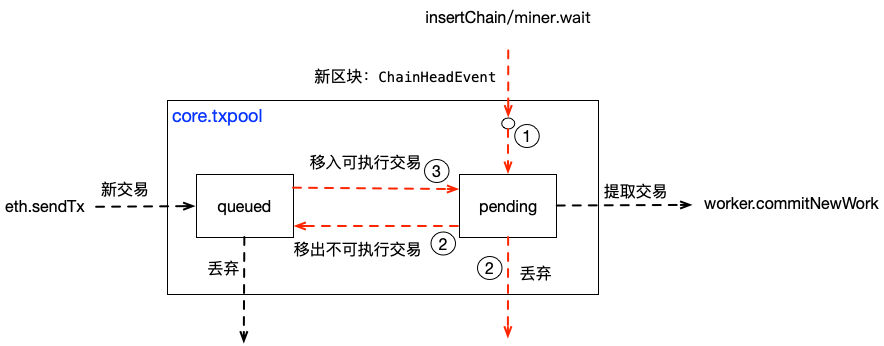

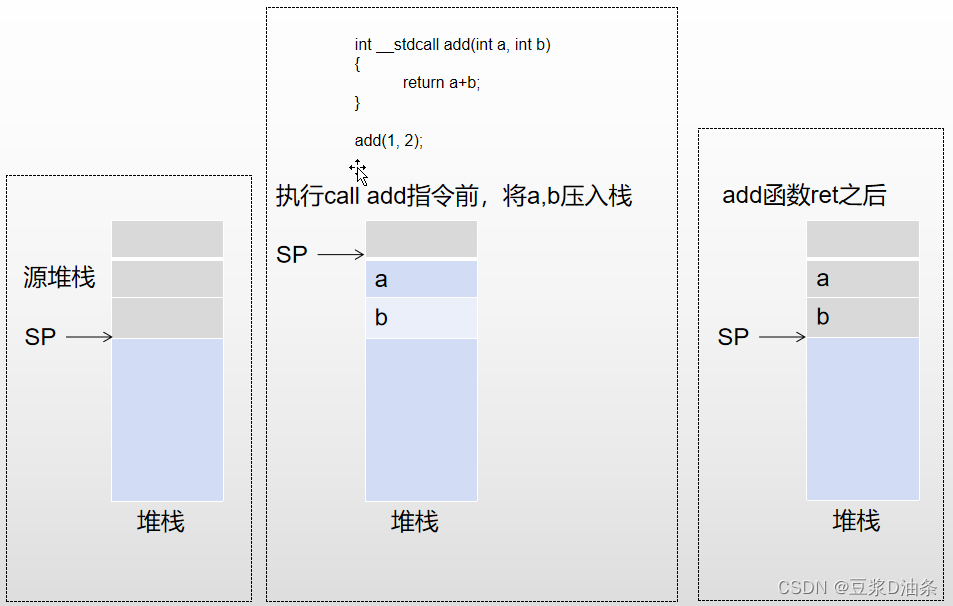

电源经过的路径依次是供电电源-->VRM供电模块-->储能电容-->平面电容-->芯片封装内的电源和地网络-->Die电容。作者说电源的供电顺序可以用“远水解不了近渴”来阐述,也就是说供电像水厂的水运输一样逐级传递,如下图所示:

水运输与电传输的等效关系

水的逐级传递过程:山泉水-->水厂-->桶装水-->水杯-->喝到口中。也就是说,Die电容的供电从上一级芯片封装内的电源和地网络获取,而不会越级直接从供电电源获取。

电源噪声的主要来源

电源系统中,噪声是影响电源完整性的一个主要问题,明确噪声来源,可以更有效地去避免、解决噪声问题。电源噪声的主要来源有:

1.VRM供电模块输出的噪声:像我们常用的LDO和DC/DC等,在输出电压时,都会有一定的输出纹波,在器件的Datasheet中有明确的规格参数。原理上,LDO、DC/DC之类的稳压芯片都是通过感知的输出电压与电流对输出做调整,但是这个调整是需要时间的,一般当负载电流的变化在DC到几百kHz内时,VRM供电模块可以做出很好的响应。如果负载瞬态电流的变化速率要求更高,输出就会出现电压跌落,引入噪声,这时就需要添加额外的去耦电容来满足需求。

2.走线的直流电阻与寄生电感:长距离的供电走线会产生直流压降;走线、引脚、过孔、去耦电容的寄生电感会使高频阻抗增加,使电压出现波动。

3.PCB上Core/IO逻辑状态跳变产生的噪声:由于同步开关输出(SSO)引起的同步开关噪声(SSN)。芯片引脚在逻辑状态的切换时,会有一个大的瞬态电流流过回路,造成地平面波动,造成芯片的地和系统地不一致,称为地弹,也会造成芯片和系统的电源有差压,称为电源反弹。

4.电源与地平面谐振引入的噪声:电源和地平面可以看成由许多电感和电容构成的平面网络,平面层之间可以看成一个谐振腔体,在谐振点附近也会进一步增强谐振,产生噪声影响信号完整性。需根据谐振点的位置布置去耦电容来降低平面的谐振特性,降低电源与地平面的阻抗。

5.邻近电源网络耦合的噪声:该噪声主要通过容性耦合和感性耦合的方式在邻近平面上产生。在PCB叠层设计时,应尽可能使电源平面不相邻。

6.其他部件耦合的噪声:因邻近走线或平面附近布置的器件通过辐射、传导引入的噪声。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

链接可在往期文章中找(在文章的最后有链接)~

模拟电路设计的九个级别,你是模电几段?