(https://www.eefocus.com/article/472120.html此链接是一篇关于XillinxFPGA的IO的状态分析,希望自己也要能了解到AnLogic的IO状态并有对此问题的分析能力)

1、DriveStrength:

驱动强度,即最大能驱动的电流大小(见带负载能力的博文)。

2、PullType:

PullType共有四种选择: PULLUP、PULLDOWN、 NONE、KEEPER。数字电路有三种状态:高平、低和阻。当 数字电路有三种状态:高平、低和阻。当 数字电路有三种状态:高平、低和阻。当 数字电路有三种状态:高平、低和阻。当 数字电路有三种状态:高平、低和阻。当 输入为无效 信号的时候 ,可以通过上拉( ,可以通过上拉( ,可以通过上拉( PULLUP)电阻 )电阻 和下拉 (PULLDOWN)电阻 的方式使其处于 稳定状态。当选择 稳定状态。当选择 (KEEPER)时, 使电平保持为上一个有效值。当 使电平保持为上一个有效值。当 使电平保持为上一个有效值。当 使电平保持为上一个有效值。当 IO端口设为 LVDS的 时候, PullType只能 设为 None。

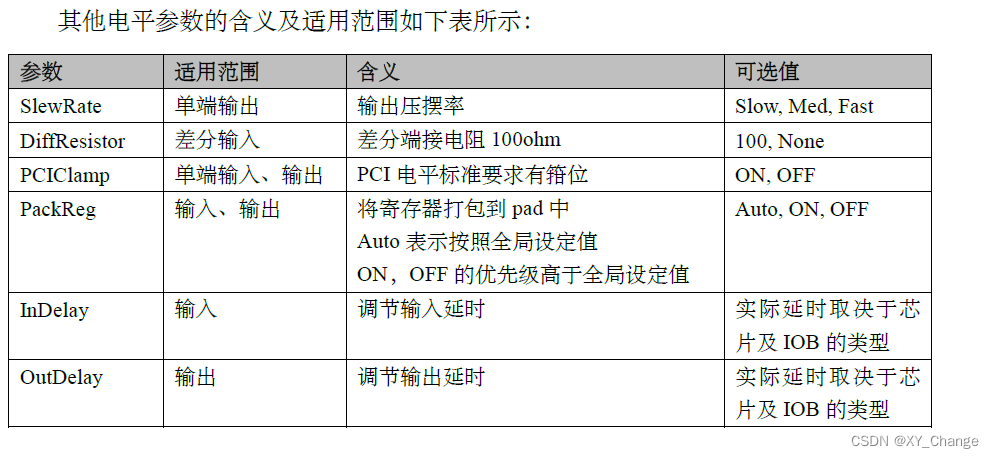

3、PackReg:

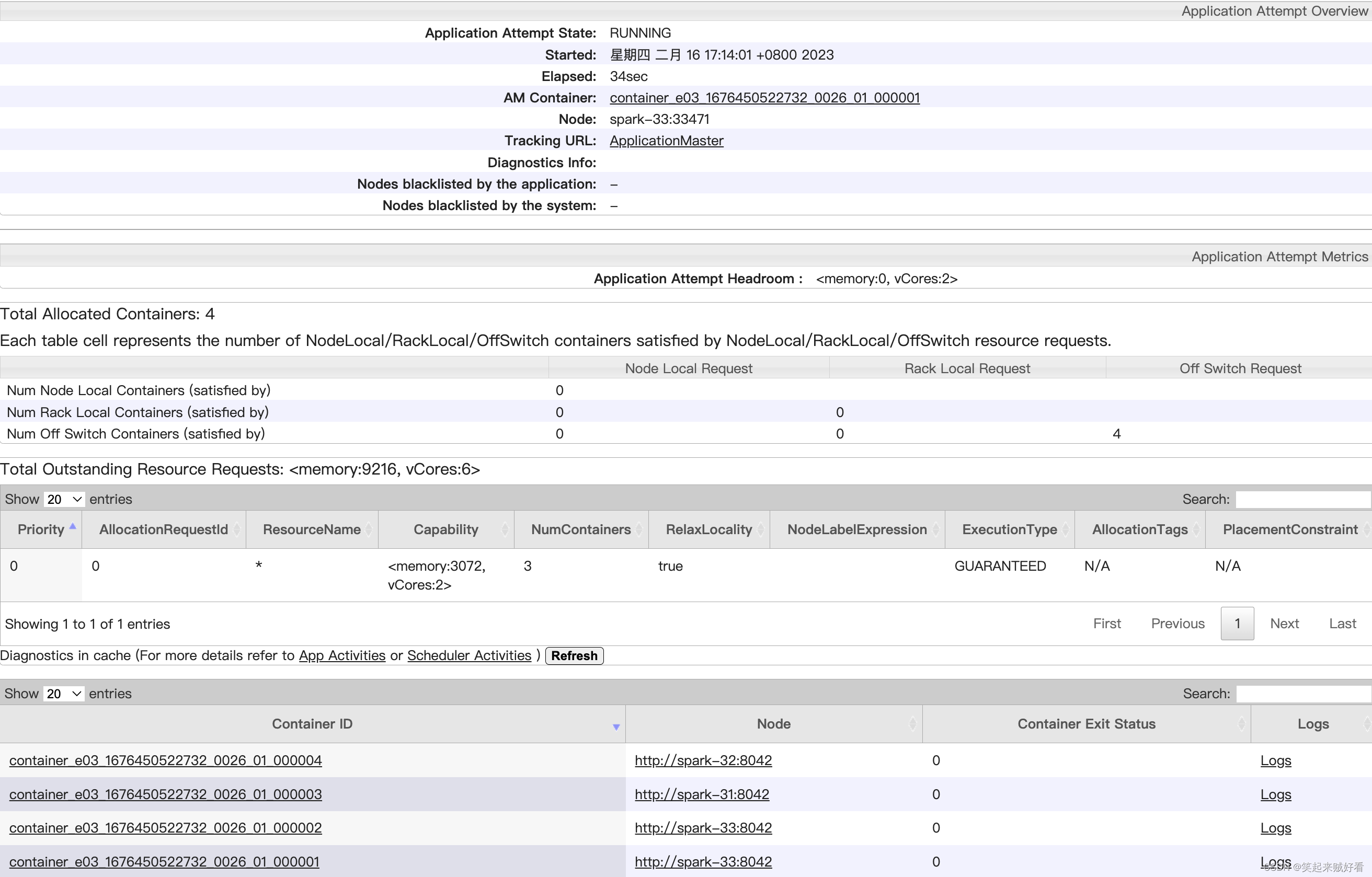

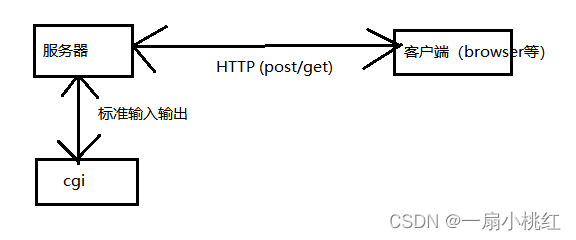

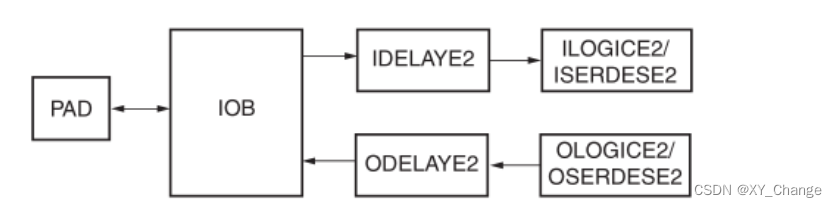

xilinx FPGA的基本资源一般包括可编程IO,IOB,CLB,BRAM,DCM,DSP等资源,某些器件还会集成一些特殊的硬核,例如GT、MIG等。其中IOB就是input/output buffer。可编程IO的作用就是完成信号的采集和输出,引脚可以配置支持不同电气特性,上拉下拉或三态,差分或单端。IOB与附近的idelay、odelay、ilogic、ologic和可编程IO等资源,共同组成FPGA的IO_Bank。(https://blog.csdn.net/wenjia7803/article/details/115339122)

为了保证FPGA输入输出接口的时序,一般会要求将输入管脚首先打一拍再使用,输出接口也要打一拍再输出FPGA。这样做的目的是为了让这打一拍的寄存器约束到IOB上,从而使得每一次编译输入或者输出的时序不会发生改变。这是因为,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,并且位置固定。当你输入或者输出采用了IOB约束,那么就可以保证从IO到达寄存器或者从寄存器到达IO之间的走线延迟最短、最大限度保证时序满足要求,同时由于IO的位置是固定的,所以每一次编译都不会造成输入或者输出的时序发生改变。

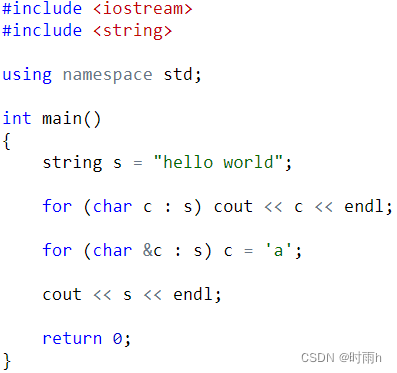

IOB的应用一般有两种,一种是在代码中添加约束,另一种可以在约束文件xdc中添加。

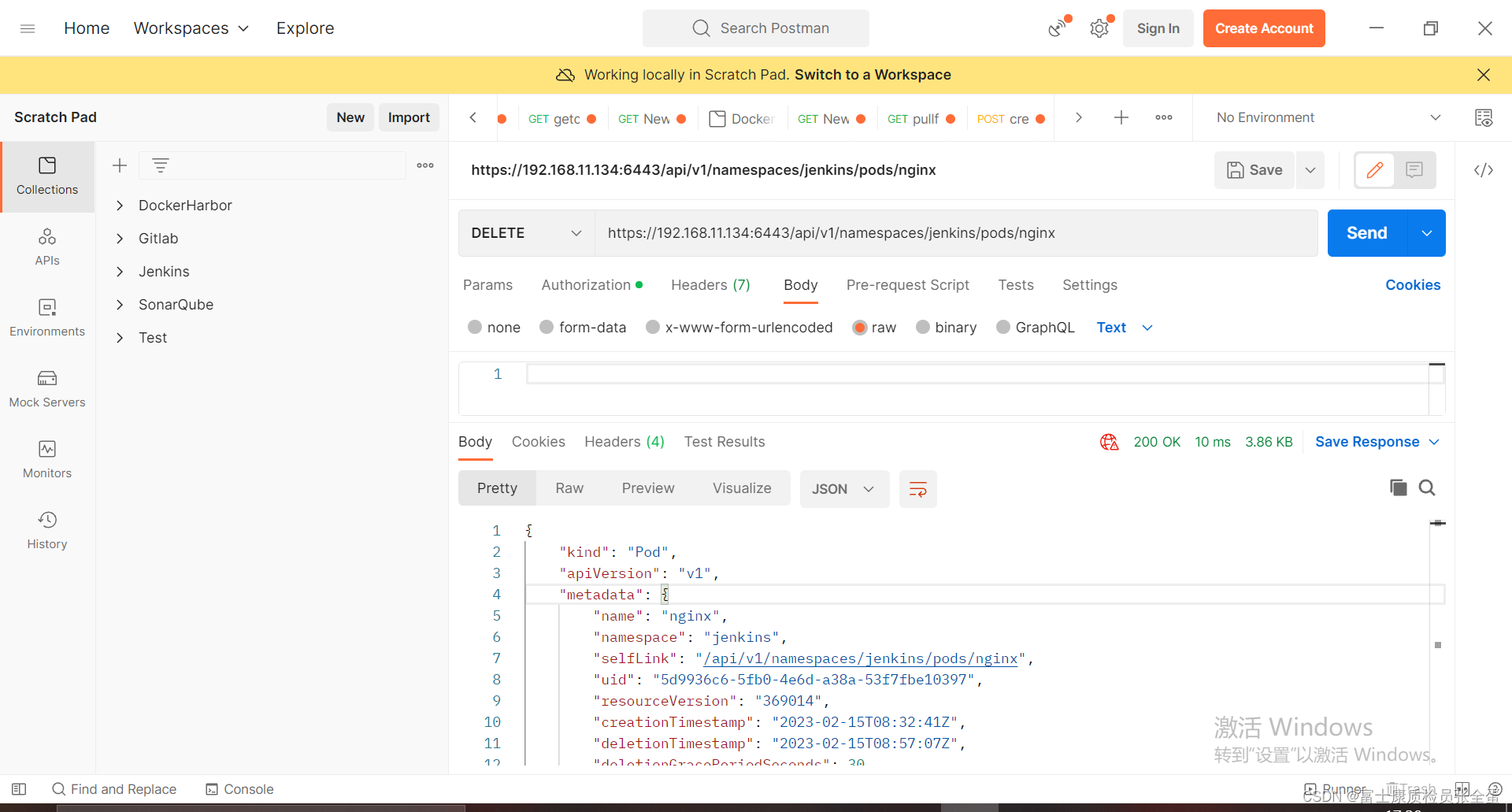

在约束文件中加入下面约束:

set_property IOB true [get_ports {port_name}]

直接在代码中加约束,在寄存器前加入下面约束,需要注意的是,对于输入IOB约束,这里的寄存器是第一级寄存器,对于输出IOB约束,这里的寄存器是最后一级寄存器,且寄存器输出不能再作为组合逻辑输入。

(* IOB = “true” *) reg O_data;

对于AnLogic-FPGA直接在IO Constraints界面的的PackReg来设置即可。

4、InDelay/OutDelay:

(https://blog.csdn.net/qq_41332806/article/details/109863482)

(https://blog.csdn.net/miracle_eicont/article/details/113064533)

Xillinx对于In/Out的delay,是由一整套操作流程,对于AnLogic,IO设置界面可以直接选取固定的一些值。这个延迟是内部延迟,到IOL的延迟(其实这部分延迟,具体的细节不清楚,有可能也不需要清楚,只要读懂时序报告,能根据时序报告来做出反应最重要),我们set_input_delay是外部到端口pad的延迟。

5、hysteresis 【ˌhɪstəˈriːsɪs】迟滞:

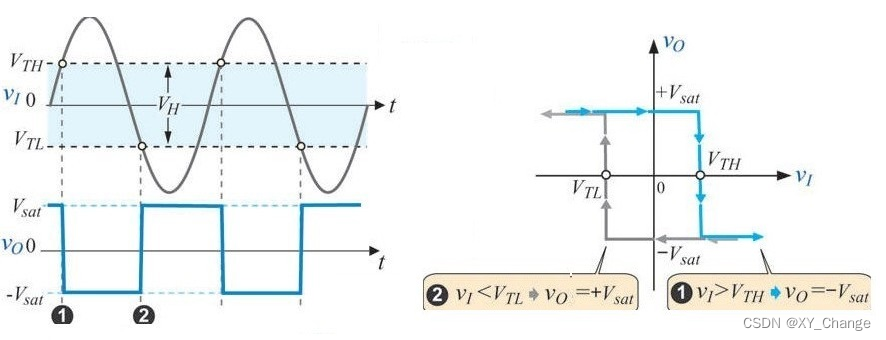

(https://blog.csdn.net/chentengkui/article/details/72567762)施密特触发器

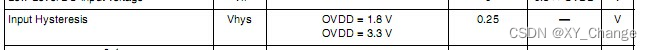

网上有一个问题是,一个工程师看到某器件手册的Input Hysteresis参数指标,不明白。

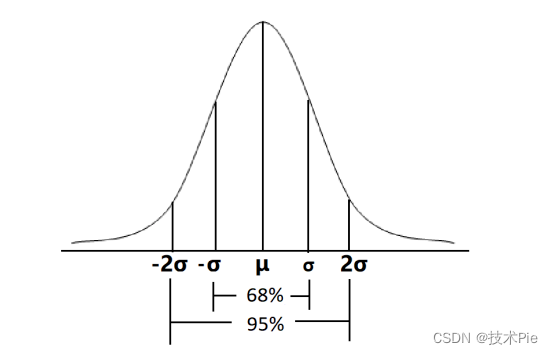

迟滞。打个比方说, 有个电压值,高于3V则为高,低于3V则为低。如果一个电压在3V左右,比如一会是3.0xV,一会又是2.9xV(这种情况在现实中很常见的), 这时你判断的状态就一会是低一会是高。

如果此时加入了迟滞,比如说加入了0.25V的迟滞,当电压高于3V时,判断为高,此时,只要电压高于(3-0.25V),则仍然判断为高。同样的道理,当电压低于3V时,则判断为低,此时只要电压低于(3+0.25V)时,仍然判断为低。这样一来,即使你电压由于噪声在小范围的波动,也不会出现误判了。

对于IO的一些设置,关注点重点还是在于时序上,对于PLL的时钟反馈模式,也让我纠结过,

根据TN604对源同步模式反馈的描述,文字理解如下:

设置了PLL核,选择源同步模式,那么PLL的输入参考时钟也即时钟输入端口到IOB寄存器的物理延时会和数据端口到IOB寄存器的物理延时相等。

对于一个开发工程来说,有一个输入时钟脚进入一个时钟clk0,系统用到的时钟有几种情况:

1)整个设计只有这一个时钟,也不用在设计中倍频或分频来給别的模块用;

对于这种情况可以,又可以做俩种处理,第一是不上BUFG,对应的同步数据口,我们希望数据进入的第一个寄存器要在IOB中。

第二是上BUFG,那么出来BUFG输出的全局时钟来进行锁存数据端口,要搞清时钟上BUFG后,较时钟端口的时钟信号clk0要延迟的量度在多少。

2)需要用锁相环进行分频倍频来进行相关模块的设计;

分频倍频出来的时钟和锁相环进入的时钟信号,软件会清楚他们之间的关系。所以分倍频出来的时钟直接去驱动其他模块就好了,而数据端口

依旧用clk0来进行锁存,若是锁相环用源同步反馈,clk0与数据口的时序对应关系 和 数据在IOB的寄存器D端与IOB寄存器的时钟口时序对应关系 一致。

那么有人会用锁相环来出一个和时钟端口clk0一样的时钟频率clk1,对于用IOB的寄存器时钟口时钟来进行锁存数据,要经历的延迟有:

clk0到PLL输入口的延迟 加 clk1较clk0的偏移 加 clk1到全局时钟网络上又到IOB寄存器时钟口的延迟。到IOB寄存器时钟口的总延迟若是十分接近数据

端口到IOB寄存器D端的话(要满足建立保持时间),那么就不会有太大问题。

硬件结构上每家器件有些许不同,不过要看得懂时序报告,能根据时序报告分析出问题,时序报告应该具有相通性