目录

- 1、图像对数变换理论

- 2、log系数的matlab生成

- 3、FPGA实现图像对数变换

- 4、vivado与matlab联合仿真

- 5、vivado工程介绍

- 6、上板调试验证并演示

- 7、福利:工程代码的获取

1、图像对数变换理论

对数变换可以将图像的低灰度值部分扩展,显示出低灰度部分更多的细节,将其高灰度值部分压缩,减少高灰度值部分的细节,从而达到强调图像低灰度部分的目的。

图像对数变换一般公式为:g = c*log(1 + f)

其中 c 为常数系数,f 为像素值范围 0~255。

如图所示,对数曲线在像素值较低的区域斜率较大,像素值较高的区域斜率比较低,所以图像经过对数变换之后,在较暗的区域对比度将得到提升,因而能增强图像暗部的细节。

2、log系数的matlab生成

由g = c*log(1 + f)公式可知,只要给出系数c,就能得到log系数,但对数计算不是FPGA的长项,所以使用matlab生成,并转换为.coe 文件

matlab部分代码如下:完整代码请看到文章最后;

clear;clear all;clc;

% g = c*log(1 + f)

num = 256;

f = [0:1:255];

c =40;

g = c*log(1+f);

%=================================================================

%创建coe文件保存参数

fid = fopen('log_para_256.coe','w');

fprintf(fid,'memory_initialization_radix = 10;\n');

fprintf(fid,'memory_initialization_vector =\n');

再经系数用verilog代码固化到rom,形成一个log系数查找表;

3、FPGA实现图像对数变换

既然已经有了log系数查找表,那么只需要将图像像素数据与查找表逐一对应输出即可,这是FPGA的强项,FPGA图像对数变换顶层代码如下:

module helai_log_algorithm (

input i_vid_hs ,

input i_vid_vs ,

input i_vid_de ,

input [7:0] i_vid_rgb ,

output o_vout_hs ,

output o_vout_vs ,

output o_vout_de ,

output [7:0] o_vout_rgb,

);

//同步输出使能信号

assign o_vout_hs = i_vid_hs;

assign o_vout_vs = i_vid_vs;

assign o_vout_de = i_vid_de;

helai_log_para r_log_para(

.addra(i_vid_rgb[23:16]),

.doutao_vout_rgb([23:16])

);

helai_log_para g_log_para(

.addra(i_vid_rgb[15:8]),

.doutao_vout_rgb([15:8])

);

helai_log_para g_log_para(

.addra(i_vid_rgb[7:0]),

.doutao_vout_rgb([7:0])

);

endmodule

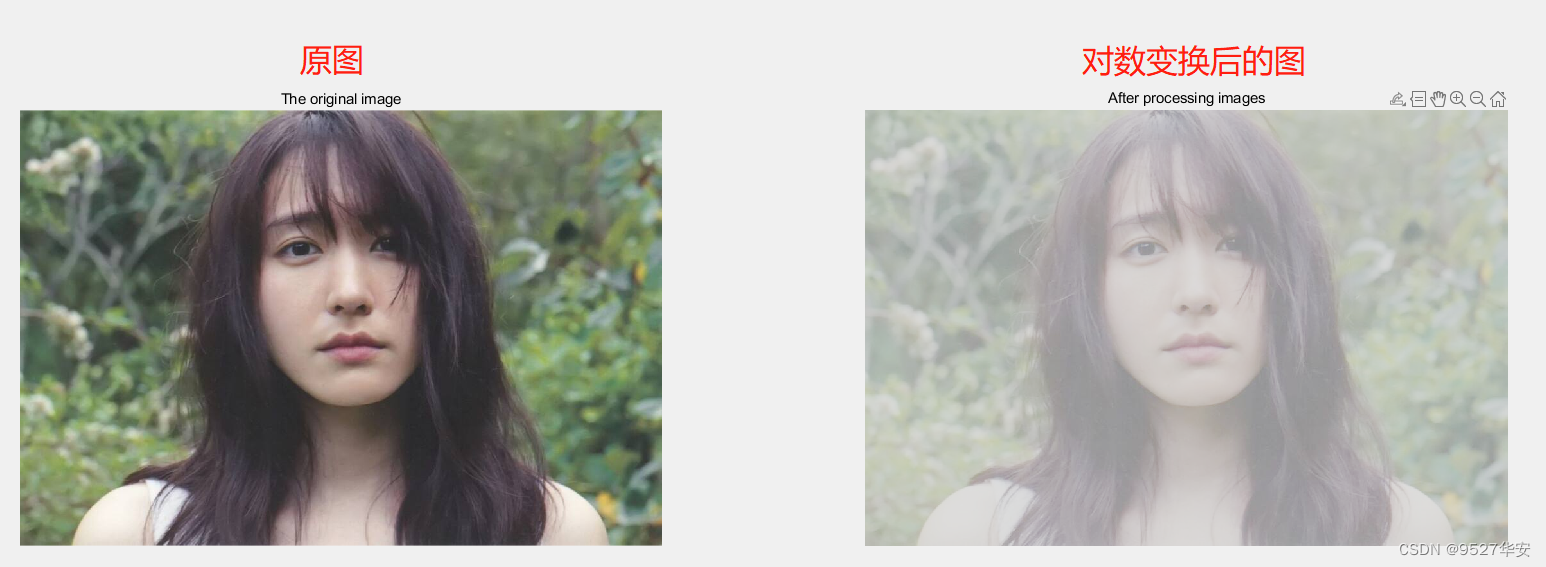

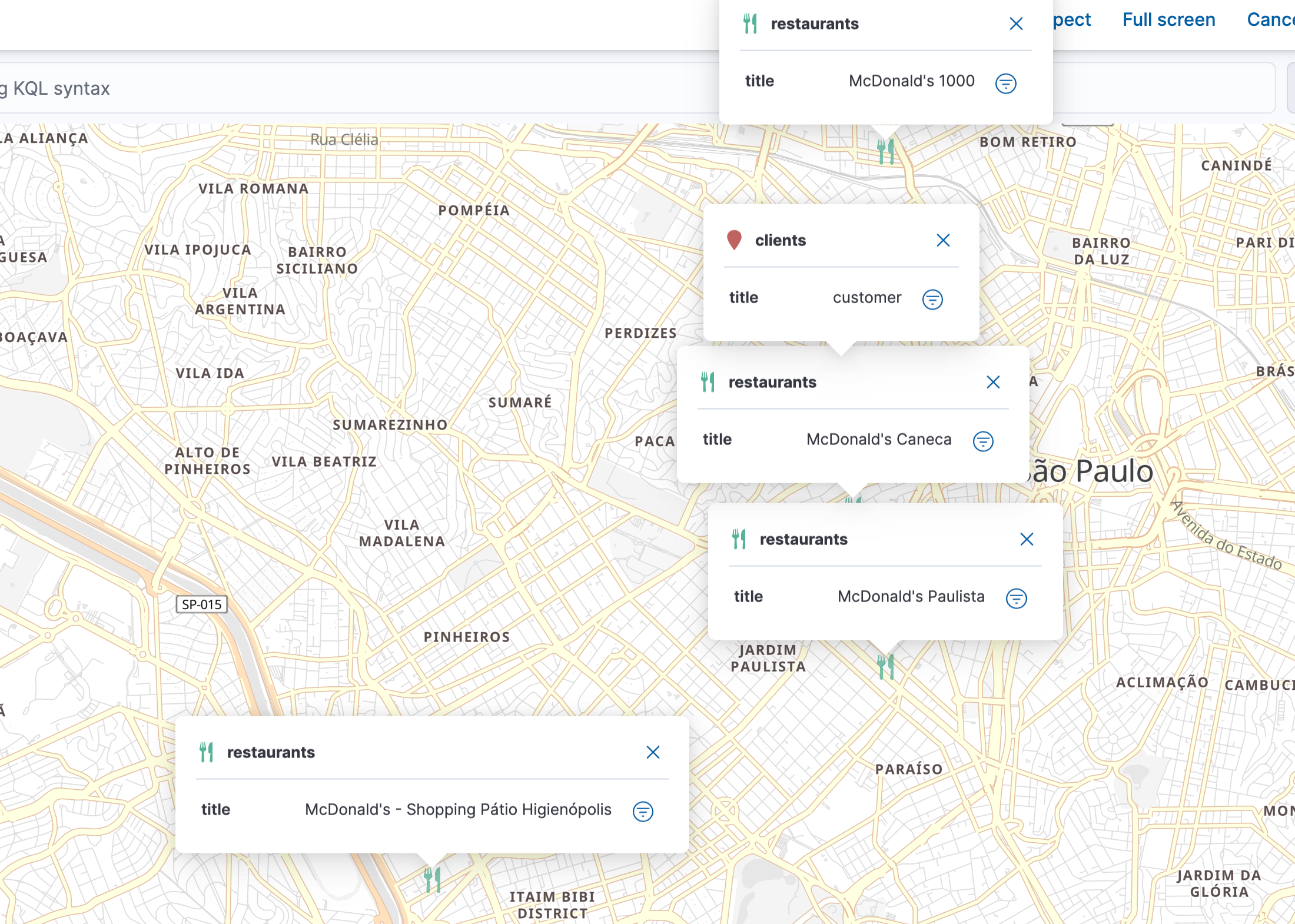

4、vivado与matlab联合仿真

仿真结果如下:

这张图的暗黑区域很少,只有我女友黑色秀发区域,可以看到输出图像整体变白了;

在看另一组仿真:

这张图原图是黑夜,对数变换后的图像就很明显了;

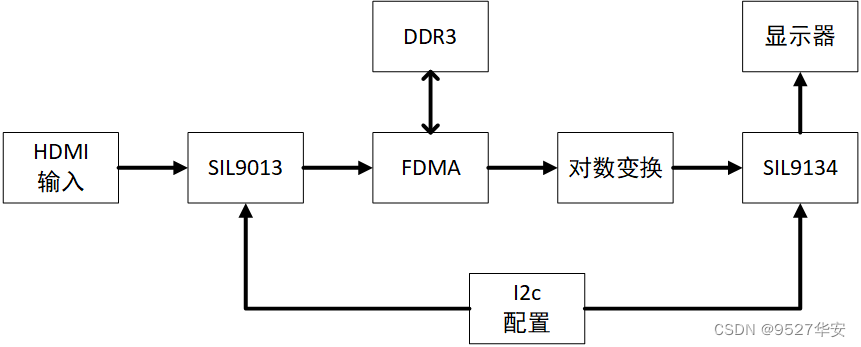

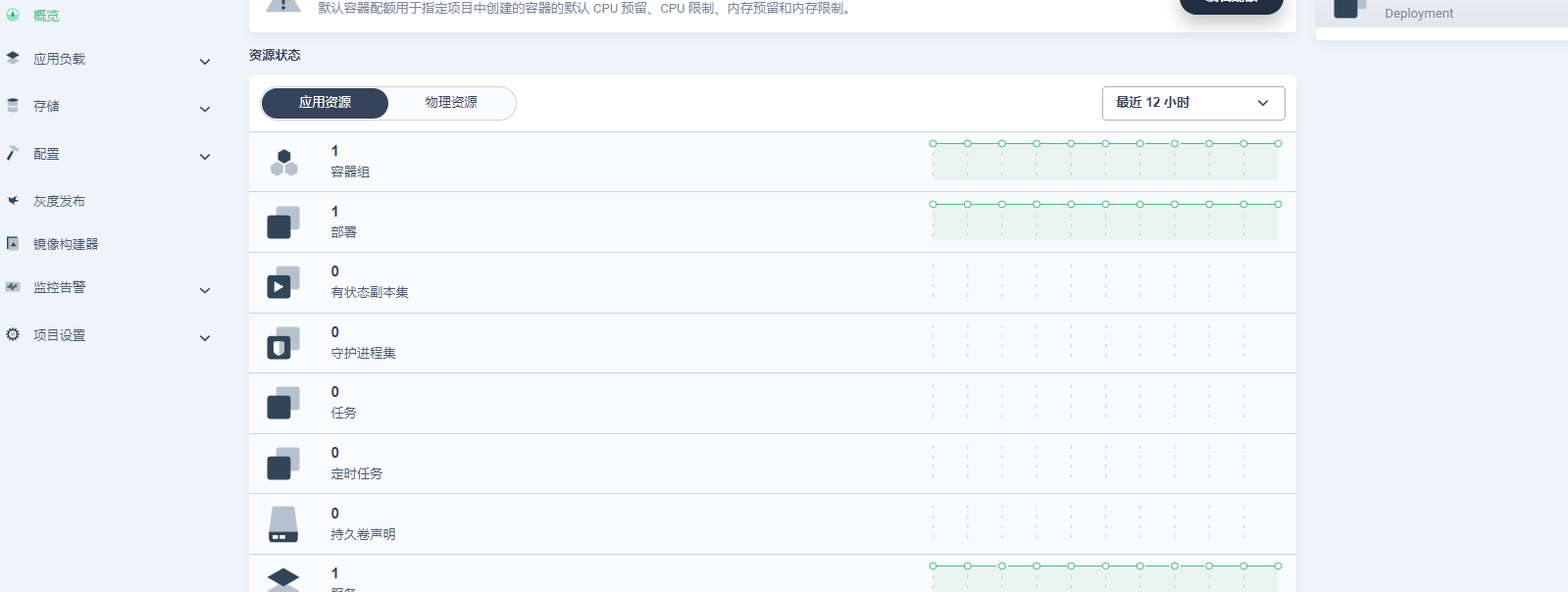

5、vivado工程介绍

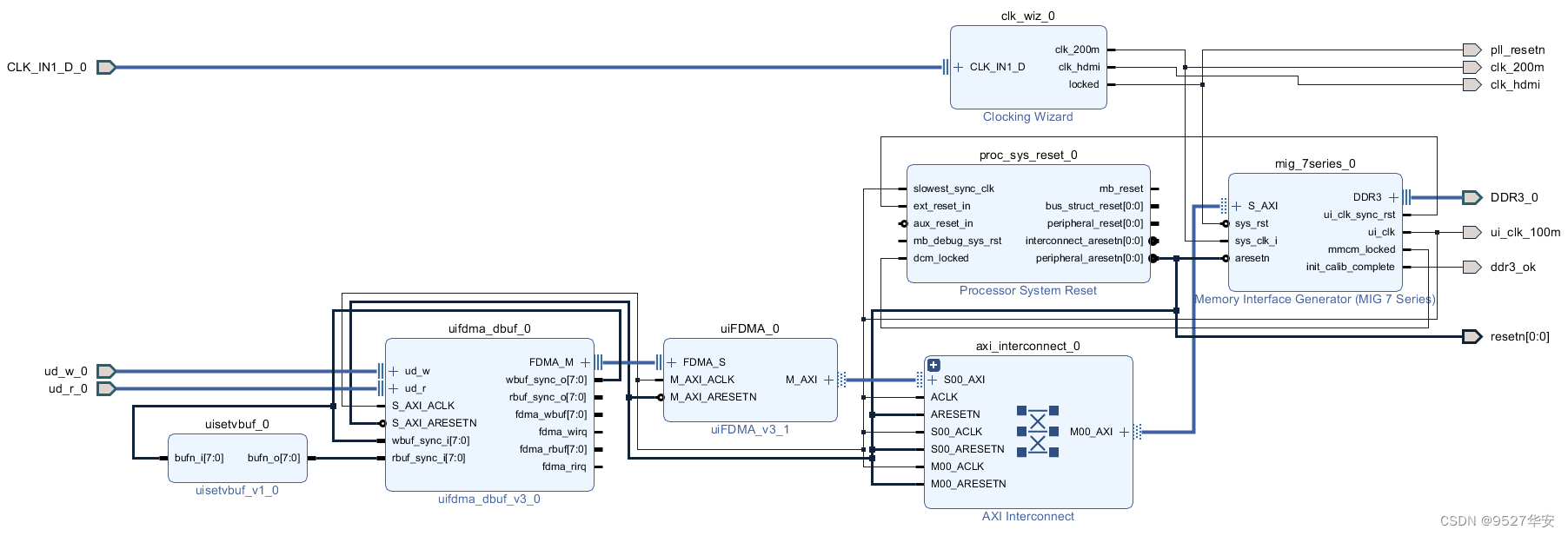

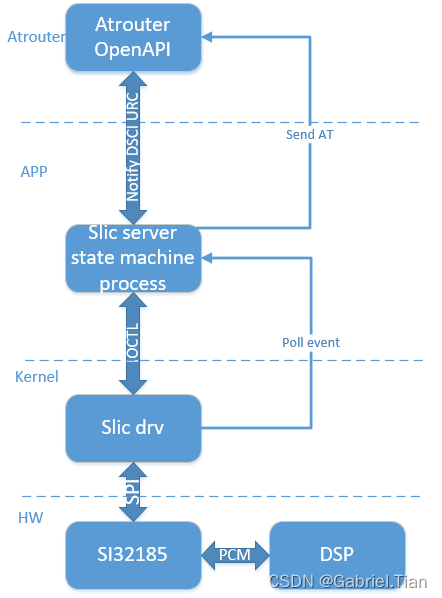

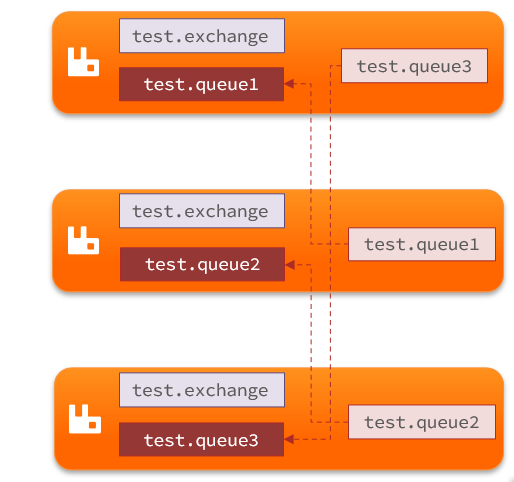

工程设计思路和框架如下:

HDMI输入和输出由编解码器由Silion Image 公 司的SIL9013和SIL9134完成,芯片工作需要iic配置,关于SIL9013和SIL9134的使用和配置,请参考我之前写的文章点击查看:SIL9013和SIL9134的使用和配置

数据采集后经FDMA将通过AXI总线图像写入到DDR3做3帧缓存再输出,关于FDMA三帧缓存,请参考我之前写的文章点击查看:FDMA三帧缓存方案

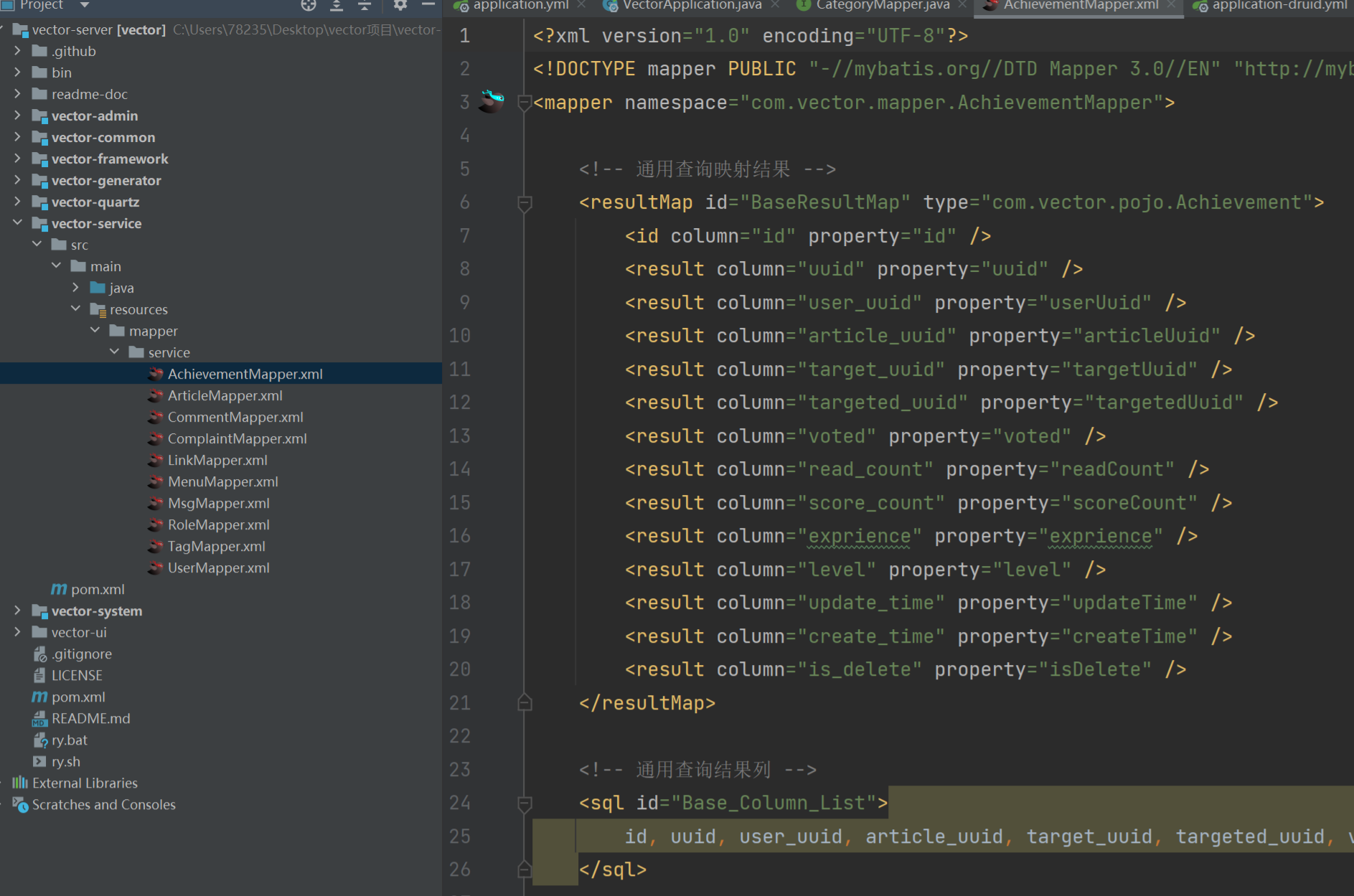

工程BD如下:

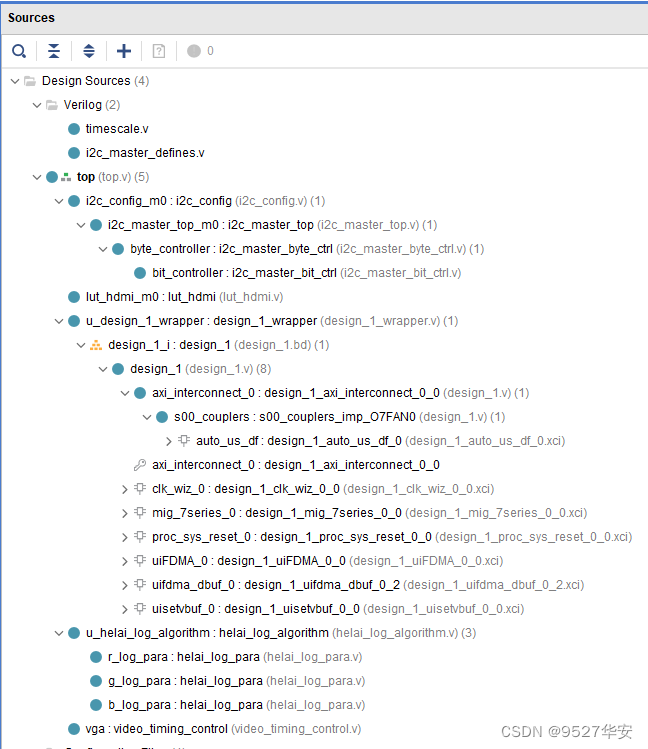

代码架构如下:

顶层代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/12/12 21:42:17

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top(

//ddr3

output [14:0]DDR3_0_addr,

output [2:0]DDR3_0_ba ,

output DDR3_0_cas_n ,

output [0:0]DDR3_0_ck_n ,

output [0:0]DDR3_0_ck_p ,

output [0:0]DDR3_0_cke ,

output [0:0]DDR3_0_cs_n ,

output [3:0]DDR3_0_dm ,

inout [31:0]DDR3_0_dq ,

inout [3:0]DDR3_0_dqs_n ,

inout [3:0]DDR3_0_dqs_p ,

output [0:0]DDR3_0_odt ,

output DDR3_0_ras_n ,

output DDR3_0_reset_n ,

output DDR3_0_we_n ,

input CLK_IN1_D_0_clk_n,

input CLK_IN1_D_0_clk_p,

output ddr3_ok ,

//hdmi_in

output hdmi_in_nreset , //9011/9013 reset

input vin_clk , //clock for 9111/9013

input vin_hs , //horizontal synchronization for 9011/9013

input vin_vs , //vertical synchronization for 9011/9013

input vin_de , //data valid for 9011/9013

input[23:0] vin_data , //data for 9011/9013

inout hdmi_scl , //HDMI I2C clock

inout hdmi_sda , //HDMI I2C data

output hdmi_nreset , //9134 reset

//hdmi_out

output vout_hs , //horizontal synchronization for 9134

output vout_vs , //vertical synchronization for 9134

output vout_de , //data valid for 9134

output vout_clk , //clock for 9134

output[23:0] vout_data //data for 9134

);

wire clk_200m ;

wire clk_hdmi ;

wire pll_resetn;

wire [0:0] resetn;

wire ud_r_0_ud_rclk;

wire [31:0] ud_r_0_ud_rdata;

wire ud_r_0_ud_rde;

wire ud_r_0_ud_rvs;

wire ud_w_0_ud_wclk;

wire [31:0] ud_w_0_ud_wdata;

wire ud_w_0_ud_wde;

wire ud_w_0_ud_wvs;

wire ui_clk_100m;

wire [9:0] lut_index;

wire [31:0] lut_data;

wire [23:0] log_rgb;

wire [23:0] i_rgb;

wire o_hs ;

wire o_vs ;

wire o_de ;

wire [23:0] o_rgb;

wire hdmi_clk_rstn;

assign hdmi_nreset =pll_resetn;

assign hdmi_in_nreset=pll_resetn;

assign ud_w_0_ud_wclk =vin_clk ;

assign ud_w_0_ud_wvs =vin_vs ;

assign ud_w_0_ud_wde =vin_de ;

assign ud_w_0_ud_wdata=vin_data;

assign ud_r_0_ud_rclk=clk_hdmi;

assign ud_r_0_ud_rvs=o_vs;

assign ud_r_0_ud_rde=o_de;

assign i_rgb=ud_r_0_ud_rdata[23:0];

assign vout_clk=clk_hdmi;

assign vout_hs=o_hs;

assign vout_vs=o_vs;

assign vout_de=o_de;

assign vout_data=o_rgb;

i2c_config i2c_config_m0(

.rst (~pll_resetn ),

.clk (clk_200m ),

.clk_div_cnt (16'd500 ),

.i2c_addr_2byte (1'b0 ),

.lut_index (lut_index ),

.lut_dev_addr (lut_data[31:24]),

.lut_reg_addr (lut_data[23:8] ),

.lut_reg_data (lut_data[7:0] ),

.error ( ),

.done ( ),

.i2c_scl (hdmi_scl ),

.i2c_sda (hdmi_sda )

);

lut_hdmi lut_hdmi_m0

(

.lut_index (lut_index),

.lut_data (lut_data )

);

design_1_wrapper u_design_1_wrapper

(

.CLK_IN1_D_0_clk_n(CLK_IN1_D_0_clk_n),

.CLK_IN1_D_0_clk_p(CLK_IN1_D_0_clk_p),

.DDR3_0_addr (DDR3_0_addr ),

.DDR3_0_ba (DDR3_0_ba ),

.DDR3_0_cas_n (DDR3_0_cas_n ),

.DDR3_0_ck_n (DDR3_0_ck_n ),

.DDR3_0_ck_p (DDR3_0_ck_p ),

.DDR3_0_cke (DDR3_0_cke ),

.DDR3_0_cs_n (DDR3_0_cs_n ),

.DDR3_0_dm (DDR3_0_dm ),

.DDR3_0_dq (DDR3_0_dq ),

.DDR3_0_dqs_n (DDR3_0_dqs_n ),

.DDR3_0_dqs_p (DDR3_0_dqs_p ),

.DDR3_0_odt (DDR3_0_odt ),

.DDR3_0_ras_n (DDR3_0_ras_n ),

.DDR3_0_reset_n (DDR3_0_reset_n ),

.DDR3_0_we_n (DDR3_0_we_n ),

.clk_200m (clk_200m ),

.clk_hdmi (clk_hdmi ),

.ddr3_ok (ddr3_ok ),

.pll_resetn (pll_resetn ),

.resetn (resetn ),

.ud_r_0_ud_rclk (ud_r_0_ud_rclk ),

.ud_r_0_ud_rdata (ud_r_0_ud_rdata ),

.ud_r_0_ud_rde (ud_r_0_ud_rde ),

.ud_r_0_ud_rempty (ud_r_0_ud_rempty ),

.ud_r_0_ud_rvs (ud_r_0_ud_rvs ),

.ud_w_0_ud_wclk (ud_w_0_ud_wclk ),

.ud_w_0_ud_wdata (ud_w_0_ud_wdata ),

.ud_w_0_ud_wde (ud_w_0_ud_wde ),

.ud_w_0_ud_wfull (ud_w_0_ud_wfull ),

.ud_w_0_ud_wvs (ud_w_0_ud_wvs ),

.ui_clk_100m (ui_clk_100m )

);

helai_log_algorithm u_helai_log_algorithm(

.i_vid_hs (),

.i_vid_vs (),

.i_vid_de (),

.i_vid_rgb (i_rgb),

.o_vout_hs (),

.o_vout_vs (),

.o_vout_de (),

.o_vout_rgb(log_rgb)

);

video_timing_control vga(

.i_clk (clk_hdmi ),

.i_rst_n(pll_resetn ),

.i_rgb (log_rgb ),

.o_hs (o_hs ),

.o_vs (o_vs ),

.o_de (o_de ),

.o_rgb (o_rgb ),

.o_x_pos(),

.o_y_pos()

);

endmodule

6、上板调试验证并演示

FPGA纯verilog代码实现图像对数变换,提供工程源码和

7、福利:工程代码的获取

福利:工程代码的获取

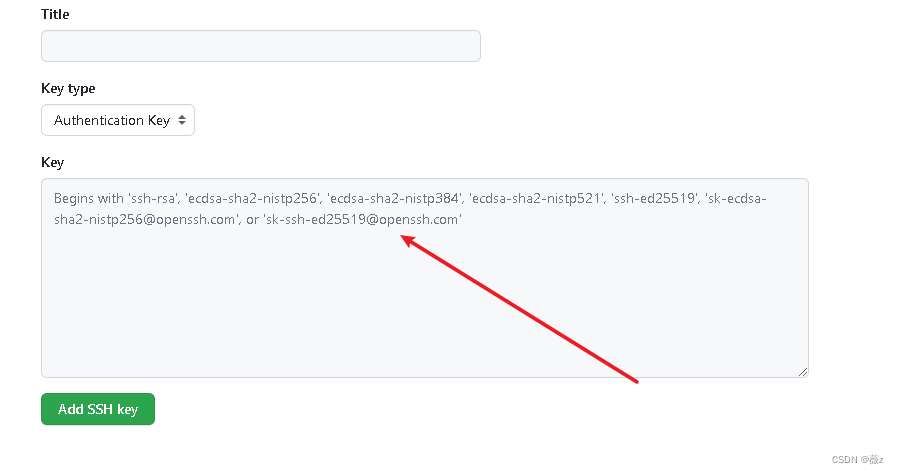

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:文章末尾的V名片。

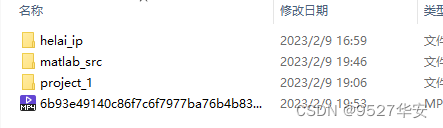

网盘资料如下:

![[C++] -- 模板初阶](https://img-blog.csdnimg.cn/5d12957543be4310aff56dadcceb9d6f.png)