CMT简介

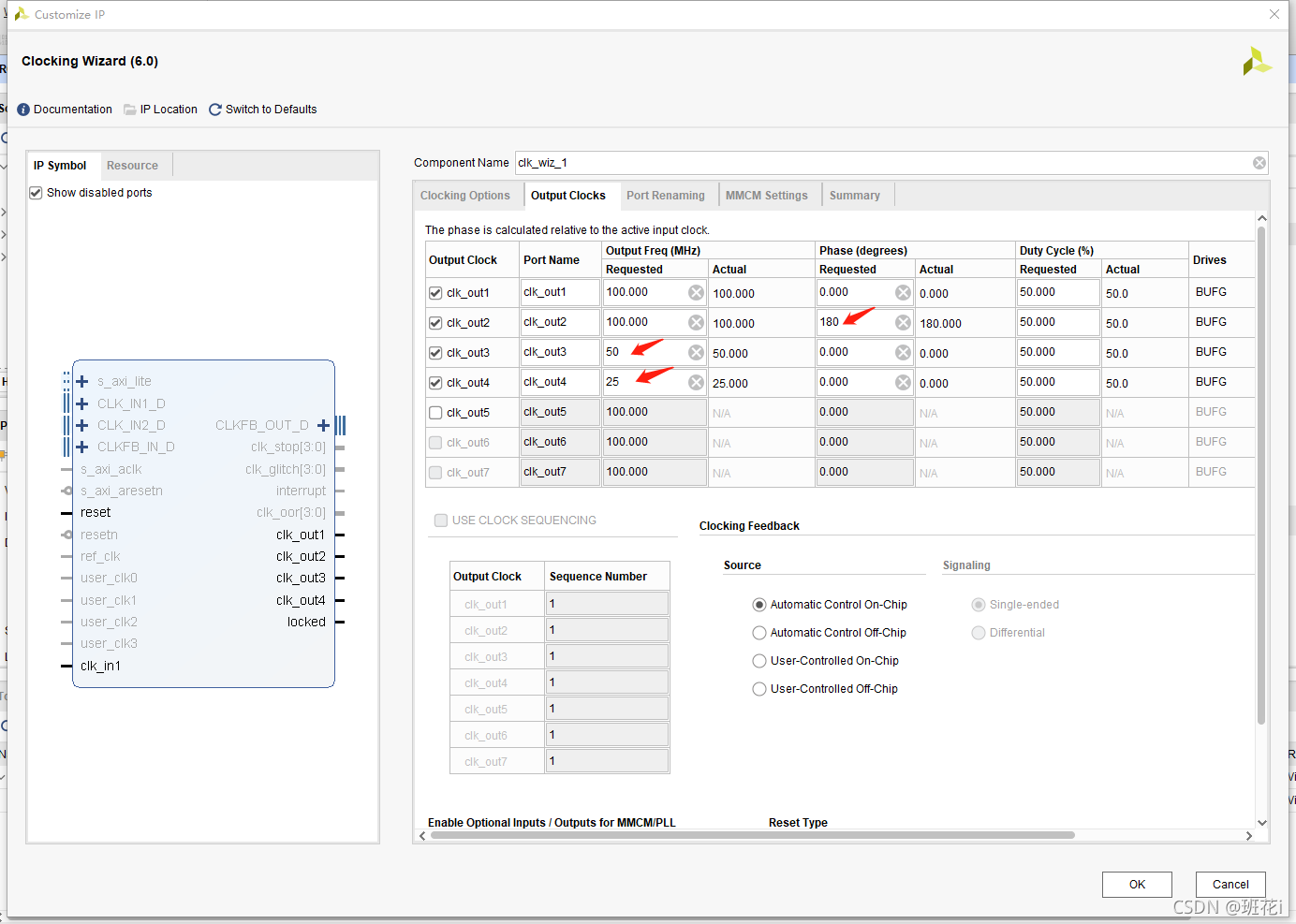

FPGA中时钟管理模块(CMT)包括PLL和MMCM,用于将时钟倍频(比如输入时钟25M,我们要产生50M时钟)、分频(在不影响系统功能的前提下,较低的工作时钟,能够降低系统功耗)、改变相位偏移或占空比等。

当需要上板时,由于板上晶振时钟固定,所以其他频率的时钟产生就要用到PLL或者MMCM。两者类似,MMCM可以完成PLL的所有功能外加一些高级功能。

时钟IP核的使用

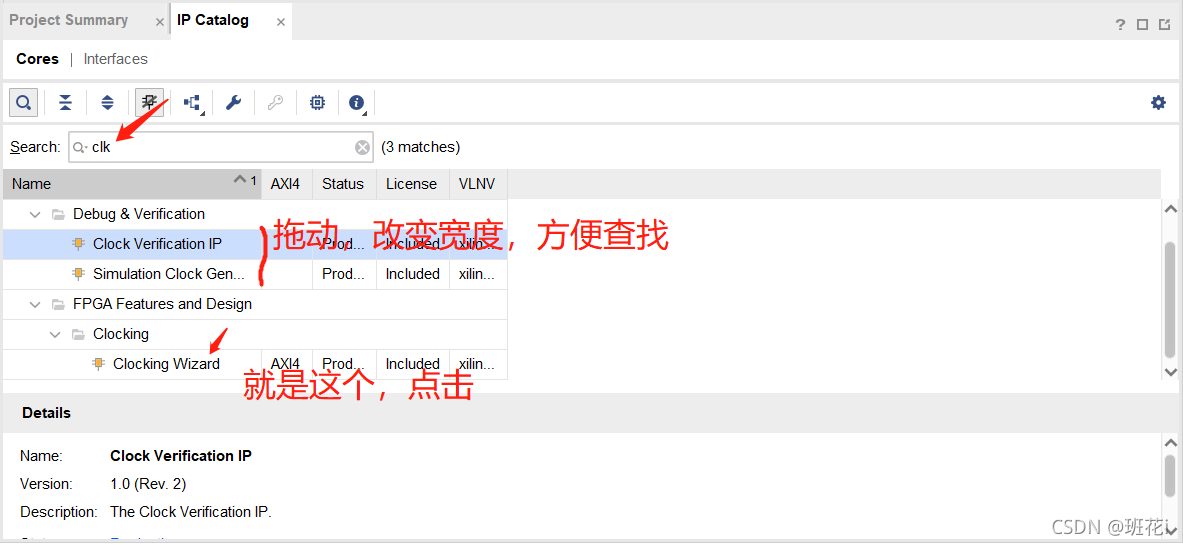

创建和配置时钟IP核

赛灵思提供的IP核在这儿

FPGA中时钟管理模块(CMT)包括PLL和MMCM,用于将时钟倍频(比如输入时钟25M,我们要产生50M时钟)、分频(在不影响系统功能的前提下,较低的工作时钟,能够降低系统功耗)、改变相位偏移或占空比等。

当需要上板时,由于板上晶振时钟固定,所以其他频率的时钟产生就要用到PLL或者MMCM。两者类似,MMCM可以完成PLL的所有功能外加一些高级功能。

赛灵思提供的IP核在这儿

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2339215.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!