EDA工具,目标是硬件设计,而硬件设计,您也可以看成是一个编程过程。

大模型可以辅助软件编程,相信很多人都体验过了。但大都是针对高级语言的软件编程,比如:C++,Java,Python,JavaSctipt。面向的行为是软件(CPU或GPU)。有多大用处,见仁见智,我在之前的博客里也提到过。这里不再多说,但是对于硬件编程,也就是我们所说的RTL编程,EDA工具的使用。大语言模型是否有效,有多大的帮助,实际上没有认真思考过。

首先,RTL编程,最常用的仍然是VS-Code,在线工具可以使用EDA Playgroud。如果针对FPGA编程,使用的是专用的Vivado和 Quarters,如果要仿真,用得最多的是Mentor 的 ModelSim,还有一个很有名的综合工具:Synopsys Design。可以看到,这些工具,大多数都是厂家特制的工具,并不是针对语言级别的,这些厂家是否会提供 AI Assistant,目前并没有见到。但我们有时会使用 chatGPT来生成System Verilog,来做一些验证测试程序。

一:RTL & EDA

对于RTL代码,它的考量指标,不止是性能和可维护性,终极目标是实现的硬件的PPA,可以说,它的目标与软件编程有所不同。

- RTL设计需要符合综合工具的要求,而综合工具很有可能是厂家私有定制的。这对于AI有一定的难度。提供一些建议是可以的,要100%的正确,可能还得综合工具原厂的配合。对于综合工具反馈的问题,需要有能力修复,否则不可用。

- 不仅仅是语法问题,RTL运行依赖于SDC,LLM必须要理解SDC所描述的约束。否则无法用于实际的硬件设计。

- RTL的逻辑验证,也就是重要的测试是在仿真工具中完成,写仿真需要的激励代码和测试环境非常重要,输出的波形也是在仿真器中完成调试的,这个是否只能人工来完成?还是有可能让AI工具通过图形或视频来自动验证?

可以看出,硬件编程会与芯片的综合过程有关,与约束相关,测试验证与仿真相关,这些重要的过程,AI必须要干预,最终的目标,当然是提供更好的PPA。这些既是要求,机会,也是LLM要达成目标的难点。

二:硬件编程的关注点

那我们进一步来看看,如果要让AI生成RTL代码,需要聚焦哪些点?

2.1:PPA

和软件有很大不同,硬件开发更注重最终实现的硬件的性能,因为产出物最重是要投入大批量生产的。并不像软件那样,更注重代码的生产量。RTL设计中,代码最终的硬件性能指标往往是更重要的,也就是我们说的PPA。

PPA:Power,Performance,Area,功耗,性能,面积 是RTL设计中最重要的衡量指标。

生成代码不仅要逻辑正确,还需要能优化硬件资源的使用量(面积),满足性能需求(时序能够收敛),并且能尽量降低功耗。这些要求与软件设计中对逻辑正确性和运行Runtime性能优化有很大的不同。

硬件设计的错误,代价极大,因为在芯片流片后发现问题,修复BUG有巨大的时间和经济成本。这意味着,对于RTL代码在生成和测试阶段要求会比软件开发更加严格。

2.2:综合,仿真,调试

对于综合工具,仿真工具,调试器的依赖很高

这里我们又强调一次,综合就是将逻辑转成实际的物理硬件(芯片会提供Primtive组件)。

仿真工具就是模拟RTL的运行,需要有激励代码和测试环境,需要查看运行时的波形。

调试器可以随时查看程序中的变量和IO值。

总的来说,RTL的编程,复杂度更高,依赖性更强,不仅仅是RTL语法的问题。

2.3:期望和猜想

对于RTL开发团队,最在意什么?上面讲了,更好的PPA,那如何得到?

硬件编程不仅仅是写好RTL,需要和EDA其它工具很好的整合,提供相应EDA工具的更好的使用方法,为综合,仿真,调试提供建议(实际上,要做到这个就很难了,因为相应的工具是闭源的)

所以,我们可以看出,RTL编码对于AI的要求,与纯软件编程是完全不同的,目标不同,环境不同。

我们期望:工程师使用 Prompt(自然语言)直接生成电路的设计:

(来自 ChipGPT的思路)

- 提示生成:它根据用户给出的规范描述为ChatGPT创建提示(例如:“设计带有进位和进位输出的4位加法器”)。

- 程序生成:它使用 ChatGPT 生成每个提示的 Verilog 代码。

- 程序优化:输出管理器通过机器反馈和人工反馈修复和改进 Verilog 代码(原始程序),并将它们放在最终的设计空间(程序列表)中。这个空间包含了所有可能的解决方案。

- 设计选择: ChipGPT 搜索最终的设计空间,并根据目标指标选择最佳设计。

好了,然后 如何优化,达成合理的PPA?

我们可以使用四个模块来控制输出:Specification Split、Prompt Manager、Output Manager和Enumerate Search。

规范拆分和提示管理器在调用 GPT 之前工作,以处理自然语言规范并为 GPT 生成提示。

调用 GPT后,输出管理器和枚举搜索将工作,以处理设计约束并根据功耗、性能和面积指标选择最佳版本的代码。

在每次迭代中重复这些步骤,直到获得满足规范和约束的最终输出。

三:NVida.ChipNeMo

说了要求和难点,我们看看目前做得比较好的RTL生成工具(我们认为可能做得比较好,实际上也没有用过,纯粹是看它的名头)。

ChipNeMo是英伟达开发的专用于芯片设计的LLM,旨在利用生成式AI技术提升芯片设计流程中的生产力和效率。

3.1:它的主要作用

- 工程助理聊天机器人:聊天辅助,这和chatGPT类似了,只是它专门针对GPU,ASIC和架构设计工程师们提供支持

- EDA脚本生成:基于Python和Tcl等特定领域工具,为VLSI相关的定时任务提供脚本。

- 错误和摘要分析:内部错误和问题跟踪系统的一部分,对错误进行总结和分析。

- 自动生成RTL Verlog代码

- 生成断言用于形式化模型检查 :这个用于形式化验证,确保设计符合特定的规范和约束条件。

3.2:训练的数据来源

内部数据:(占了90%)

设计原代码:芯片设计中的实际源代码。

文档数据:设计和实现过程中的文档。

Bug总结:内部设计和验证过程中的Bug报告和总结。

验证数据:验证过程的相关数据。

其它数据:可能包括非标准化的设计过程相关内容。

公共数据(10%)

Wiki(7.2%):公开的Wiki

GitHub(2.8%):公开的代码库,包含Verilog的开源项目。

可以看得出,公开的数据非常的少。数据总量:25.3亿Token。用于训练的有24亿。

3.3:验证数据集

模型的评测集是使用的公开评测集:VerilogEval。

- VerilogEval 是一个公开的评测集,用于评估 ChipNeMo 在 Verilog 代码生成任务中的性能。

- 这一工具可以为社区提供一个标准化的验证框架,用于测试 Verilog HDL 代码生成的准确性和性能。

关于ChipNeMo的详细信息,可以参见:

ChipNeMo:Domain-Adapted LLMs for Chip Design

很可惜,就只有论文,该模型目前只能内部使用,未提供对外发布或商业服务。

四:LLM & EDA

我们把问题放大一点,放到EDA工具的层面,而不仅仅是RTL代码。因为,从前面的描述,我们也可以看出,单独讲RTL Code,实际上是没有意义的,因为它只是形成硬件设计的环节之一,必须要把整个EDA工具都考虑进去,才能意义。

目前,LLM 对于EDA的助力,有三种做法:

1:Assistant Chatbot——聊天对话

2:HDL Generation —— 硬件编程语言也就是RTL code 的生成器

3:HDL V & V —— Code Verification & Analysis

4.1:Assistant Chatbot

ChipNeMo:https://arxiv.org/pdf/2311.00176

该项目旨在探索大型语言模型(LLMs)在工业芯片设计中的应用。不同于直接部署商业或开源的LLMs,ChipNeMo采用了领域适应技术,包括领域适应标记化、领域适应继续预训练、模型与特定领域指令的对齐以及领域适应检索模型。研究通过三个选定的应用场景评估了这些方法:工程助手聊天机器人、EDA脚本生成和错误总结与分析。

这是Nvida的项目,上面已经做过介绍。

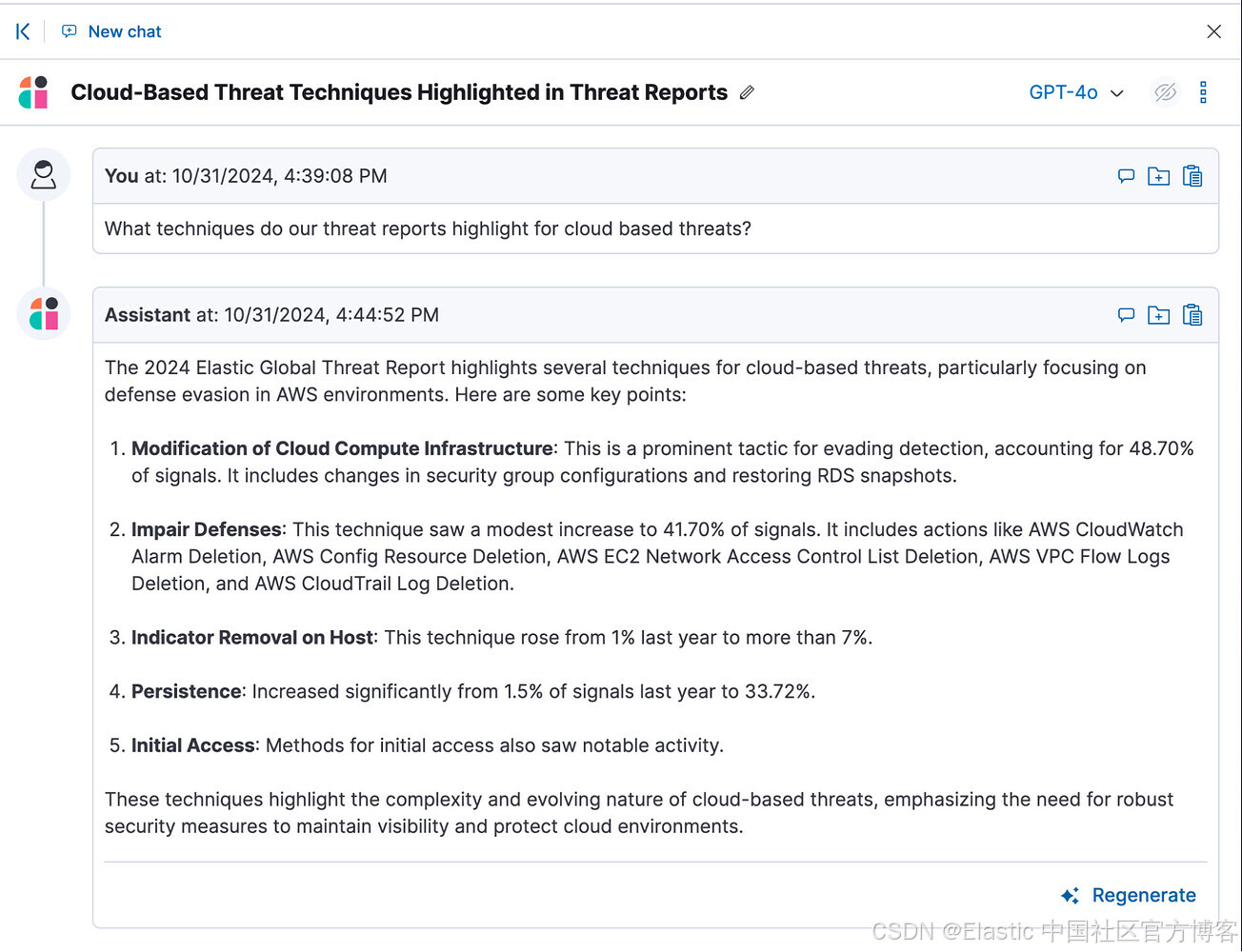

Smarton-AI:Home | Smart On

这是针对EDA工具的使用助手,底层支持是LLM。

AskSia:免费在线 Verilog 助手 - AskSia

RapidGPT:Welcome to RapidGPT | PrimisAI

这是针对VS-Code的插件,如下图:

试了一个免费版,速度极慢,应该需要翻墙。

4.2:HDL Generation

ChatEDA:https://arxiv.org/pdf/2308.10204

一个由大型语言模型(LLM)驱动的电子设计自动化(EDA)自主代理。ChatEDA旨在通过有效管理任务分解、脚本生成和任务执行来简化从寄存器传输级(RTL)到图形数据系统版本II(GDSII)的设计流程。

ChipGPT:https://arxiv.org/pdf/2305.14019

大型语言模型(如ChatGPT)在硬件设计中的潜力,特别是通过自然语言交互辅助硬件工程师实现更高效的逻辑设计。研究提出了一种基于LLM的零代码四阶段逻辑设计框架,无需重新训练或微调,以评估LLM在硬件设计过程中的潜在能力。

Cadence 提供的EDA AI 增强工具,也叫ChipGPT。

VerilogEval:https://arxiv.org/pdf/2309.07544

用于评估大型语言模型(LLMs)在生成Verilog代码方面的性能的基准框架。随着LLMs在各个领域的广泛应用,特别是在硬件设计和验证中的应用,作者提出了一套全面的评估数据集,包含来自HDLBits网站的156个问题,涵盖了从简单组合电路到复杂有限状态机的各种Verilog代码生成任务。

GPT4AIGChip:https://arxiv.org/pdf/2309.10730

通过大型语言模型(LLMs)自动化人工智能(AI)加速器设计的可能性,并提出了一个名为GPT4AIGChip的框架。该框架旨在利用人类自然语言而非领域特定语言来简化AI加速器的设计过程。

Chip-Chat:https://arxiv.org/pdf/2305.13243

在硬件设计中利用大型语言模型(LLMs)面临的挑战和机遇。随着数字设计能力的增长和复杂性增加,软件组件在集成电路(IC)计算机辅助设计(CAD)中采用了机器学习(ML)。尽管ML研究在IC CAD中主要集中在后端流程上,本文探索了将新兴的ML模型应用于硬件设计过程的早期阶段,即编写硬件描述语言(HDL)。

AutoChip:https://arxiv.org/pdf/2311.04887

这是一个利用大型语言模型(LLMs)反馈来自动化生成硬件描述语言(HDL)代码的方法。传统上,硬件工程师使用如Verilog这样的HDL编写设计,并通过调试来修正错误。这种方法虽然有效,但对于复杂的设计来说,既耗时又容易出错。LLMs可以通过提供工具帮助生成代码来缓解这些问题。

RTLLM:https://arxiv.org/pdf/2308.05345

一个用于评估基于自然语言指令生成设计RTL(寄存器传输级)的大规模语言模型(LLMs)的开源基准。作者们指出,尽管LLMs在商业产品如GPT-3.5和GPT-4中取得了显著的成功,但现有研究中针对硬件设计的LLM应用案例相对简单且规模较小,这使得不同LLM解决方案之间的公平比较变得困难。

VeriGen:https://arxiv.org/pdf/2308.00708

大型语言模型(LLMs)在生成高质量Verilog代码方面的潜力,以实现硬件设计自动化。研究团队通过在GitHub和Verilog教材数据集上微调预训练的LLMs,并使用自定义测试套件评估生成代码的功能正确性。

RapidGPT:Welcome to RapidGPT | PrimisAI

RapidGPT 是业界首款为 FPGA 工程师量身定制的基于人工智能的配对设计器。这个强大的工具旨在通过提供上下文建议和无与伦比的语言到 HDL 功能来彻底改变硬件设计流程。

4.3:Code Verification & Analysis

ChipNeMo:同上。

RTLFixer:https://arxiv.org/pdf/2311.16543

RTLFixer框架,该框架利用大型语言模型(LLMs)自动修复Verilog代码中的语法错误。尽管LLMs在生成代码方面表现出色,但作者发现约55%的LLM生成的Verilog代码错误是语法相关的,这导致编译失败。为了解决这个问题,作者提出了一种新的调试框架,结合了检索增强生成(RAG)和ReAct提示,使LLMs能够作为自主代理与反馈互动地调试代码。

AutoSVA:AutoSVA

AutoSVA 是一种自动生成单元级 RTL 验证的正式测试平台的工具。其目标是根据 RTL 模块信号声明部分的注释生成属性,以便模块最终向前推进。

我们不仿看看行业标杆,Synopsys准备在它的EDA产品中如何融入AI?

五:Synopsys.ai

新思的战略是与微软,英伟达合作。

5.1:新思的AI战略

芯片设计复杂度的迅速增加给半导体行业带来挑战,包括工艺节点的推进、多芯片集成、节点迁移等。新思通过AI在电子设计自动化(EDA)中的进步来应对这些挑战,Synopsys.ai 是一个全面的AI驱动EDA套件,旨在解决芯片设计复杂性带来的挑战。

Synopsys.ai 通过AI驱动的设计优化、数据分析和生成式AI能力,显著提高了整个设计流程的质量和效率。

该套件包括设计空间优化(DSO.ai)、验证空间优化(VSO.ai)、测试空间优化(TSO.ai)和模拟空间优化(ASO.ai)等解决方案,帮助工程师在PPA(功耗、性能、面积)目标上取得最佳结果。

5.2:Synopsys.ai 的主要功能

5.2.1:对设计的优化

Synopsys.ai 的设计优化解决方案显著提高了设计效率和质量。

Synopsys DSO.ai 是业界首个自主AI应用,通过强化学习在巨大的设计空间中搜索优化目标,显著提高PPA。DSO.ai 获得了行业奖项,被90%的半导体公司采用,用户报告生产率提高超过3倍,功耗降低高达15%,芯片尺寸显著减小。

面向设计工程师:

Synopsys VSO.ai 通过AI分析RTL并推断覆盖率,帮助验证工程师更快地达到覆盖率目标并发现更多错误。

面向验证工程师:

Synopsys TSO.ai 自动搜索测试空间中的最优解,显著减少测试模式数量和ATPG周转时间,降低测试成本并加速结果。

面向测试工程师:

Synopsys ASO.ai 通过AI驱动的自动化功能显著提高模拟设计的生产力,实现快速的模拟设计迁移和优化。

面向模拟设计工程师:

5.2.2:对数据的分析

Synopsys.ai 的数据驱动解决方案通过全面的AI数据分析提高设计效率和质量。

Synopsys Design.da 提供全面的数据可视化和机器智能引导的设计优化和签核关闭解决方案,通过分析大量数据提供深入的见解。

Synopsys Fab.da 是一个AI驱动的制造过程分析和控制解决方案,帮助客户充分利用制造数据,提高生产效率和良率。

Synopsys Silicon.da 提供独特的分析解决方案,跨越设计和产品制造阶段,通过自动识别硅数据异常来提高芯片质量和产量。

这些解决方案通过分析大量数据,提供实时的分析仪表板和智能指导,帮助工程师快速识别和解决设计和制造中的问题。

5.2.3:生成式AI

Synopsys.ai Copilot 提供协作能力,指导工程师使用工具、分析结果和优化EDA工作流程。

生成式能力加速RTL、形式验证断言创建和UVM测试平台的开发。

完全自主能力实现从自然语言到架构、设计和制造的端到端工作流程创建。

生成式AI能力基于大型语言模型(LLMs),可以在任何本地或云环境中部署。

-

Knowledge Assistant

在工具的使用流程中提供专业的问题答复,类似专家库吧。

- Debug Assistant

根据上下文进在调试过程中进行分析和设计

- Wokflow Assistant

针对EDA的过程流中提供规范性指引和流程推荐

- Collateral Generation

RTL 代码,测试平台代码,断言调试生成。

5.3:优势

- 提高产品质量或结果(QoR)和生产力

-

解决系统复杂性、人才短缺和行业需求增加的问题

-

实现前所未有的生产率提升

5.4:目标

- 系统架构至设计和制造,利用AI优化性能,加速芯片设计并提高EDA流程效率

-

功耗、性能、面积(PPA)目标优化,提供领先的PPA和良率

-

缩短上市时间并降低成本,工程团队可以专注于设计创新

六:Cadence:ChipGPT

ChipGPT是 Cadence 和 Renesas 合作的 AI产品,我们简单看一下它能做什么?

大体要做的事情,与synopsys的一致:

- 自动化重复性任务 示例:一家大型芯片公司使用 ChipGPT 进行编码和模拟。这节省了时间,因此工程师可以致力于改进设计。

- 提供实时反馈 示例:设计团队使用 ChipGPT 获得有关其电路的快速反馈。这帮助他们快速尝试不同的设计,使事情变得更好更快。

- 提高设计质量 示例: ChipGPT帮助一家知名公司及早发现问题,节省了资金。最终的芯片比预期的要好,体现了AI的价值。

- 提高设计灵活性 示例:一家小型科技公司使用 ChipGPT 根据功耗等因素更改设计。当问题出现时,他们迅速解决问题,保持领先。

- 缩短上市时间 示例: ChipGPT 帮助另一家芯片公司提前按时完成任务。这让他们能够更快地推出产品,从而击败其他公司。

附:工具

附1:VGen

GitHub - shailja-thakur/VGen

VGen 是一个基于大型语言模型(LLMs)的开源项目,旨在自动生成高质量、低错误率的 Verilog 代码。

附2:Verilog Plugin

直接使用各种LLM的大模型插件,比如:阿里的通义灵码,Github Copilot,Continue(自已配置LLM Model)

附3:AskSia

免费在线 Verilog 助手 - AskSia

一个免费的在线问题助手,可以询问一下RTL编程的问题。