数字IC后端设计导入需要用到的input数据如下图所示。

数字后端零基础入门系列 | Innovus零基础LAB学习Day9

Netlist:

设计的Gate level(门级)网表。下图所示为一个计数器设计综合后的门级netlist。

从这个netlist中我们看到这个设计顶层的名字叫counter,包含四个输入信号,一个输出信号。而且这个设计调用了8个标准单元的cell。

Netlist本质是一个电路原理图。上述Netlist对应的电路图如下图所示。

看这个电路时需要搞清楚如下几个概念:

1)Port 。像咱们这个counter的设计中的in[0],in[1] 都是属于io port。

2)Pin 。每个标准单元cell都有若干输入输出pin。比如U11这颗cell的A1,A2,B,C都是这个cell的四个输入pin,而Z pin是它的输出pin。每个pin都要和其他信号进行互连(逻辑连接)。

- Net。上图设计中的U12的输出Pin Z和out_reg_1这个寄存器的D pin互连的逻辑线就是Net,它的名字为N7。注意我们所说的net为逻辑net。后续绕线后对应的physical走线为physical net shape。

4)Timing Arc (时序弧)。标准单元的输入到输出这段就是一段Timing arc。比如U13这颗cell,它的timing arc有两条。每条timing arc在时序库lib中都会定义好。它是后续工具计算每个cell 延时的基础。

Tech File/Tech Lef : 精简版的物理设计规则,它是被用来指导工具按照design rule来完成布线。这个design rule是foundary代工厂加工制作的物理规则,比如metal间距要求,metal最小线宽等规则。

icc和icc2用tf,encounter/innovus用tech LEF,本质描述的信息是一样的,不过tech LEF里面会含有一些tf里面没有的信息,比如天线效应规则,cell spacing rule等。

Site:代表最基本的布局单元。site一般情况是最小standard cell的大小。类似cell的最小size。定义在 lef中, 如下图所示:

SITE tsm3site

SYMMETRY y ;

CLASS core ;

SIZE 0.660 BY 5.040 ;

END tsm3site

上面LEF字段定义了site的尺寸大小和方向, size是横向长度,BY是高度,接下来的standard cell会引用该site定义,所有stardard cell横向长度一定是site长度的整数倍,我们不允许非整数倍site长度的stardard cell。如下图size 1.32是基本site 0.66的2倍宽。

MACRO INVXL

CLASS CORE ;

FOREIGN INVXL 00 ;

ORIGIN 0 0 ;

SIZE 1.32 BY5.04 ;

SYMMETRY X Y ;

SITE tsm3site;

PIN Y

DIRECTION OUTPUT ;

PORT

LAYER Metal1 ;

RECT 1.03 2.38 1.18 3.225 ;

RECT 1.03 1.35 1.12 1.845 ;

END Y

END INVXL

Row: 和site有关的另一个概念是row,row是有N个site排列组成。

Routing Track: 它是指金属走线的通道。工艺库中会指定好每层金属的track,它有默认方向的走线方向,比如M2的优先走线为水平方向,那么工具在走M2 routing的时候就会优先走水平方向。因此,对于一个给定大小的设计,绕线资源是固定的,即每层金属的绕线track都是定好的。

Tluplus &QRC: Tluplus和QRC分别是foundary提供给Synopsys和Cadence PR工具使用的。工具用这个文件来估算设计中的R和C,从而计算互连线的delay。

这两个文件的内容本质上是等效的,而且它们都是以二进制的形式呈现出来,我们通过gvim打开会显示成乱码。

对于Tluplus和QRC,我们需要知道以下几方面内容:

1)每层metal单位长度的R和C

2)这个文件里面layer名字需要和tech lef,itf文件中的层次匹配

3)QRC的准确性要比captable文件好。如果没有QRC,也可以使用captable文件来替代

4)MMMC创建时需要加载对应的Tluplus和QRC文件,否则工具无法估算互连线延迟会报错,更谈不上优化时序了

Lib:liberty interchange format,描述工艺库中cell的时序和功耗信息的文件。

Lef:Library exchange format,描述std cell的物理信息,包括形状,尺寸,出pin的位置及金属层,不可布线区域OBS等。它是用来告诉工具当前std cell的形状,出pin位置以及std cell内部的走线(表现为OBS)。

DEF(Design Exchange Format): 设计交换格式DEF(Design Exchange Format)文件是有Cadence公司开发用于描述电路物理设计信息的一种文件格式,它不仅包含电路的连接关系而且还描述了电路布局布线后cell和互连线的具体物理信息。

一句话,DEF可以体现出设计的全貌。比如一个innovus routeopt后的database,我们可以通过写出设计的def,导入到Starrc中寄生参数的提取。

LEF/FRAM View/GDS VIEW: 下图左侧为NAND与非门的LEF或叫FRAM VIEW,这里的View理解成视图。右侧是NAND的GDS View,GDS是一个设计的全貌,它包含了组成这个逻辑单元的一切管子device器件。而我们知道任何一个管子都有它的Base layer和Metal layer。Base layer一般也叫FEOL Layer,Metal Layer也叫BEOL Layer。

SDC: 全称是Synopsys Design Constraints Format,是由Synopsys公司最早提出的一种约束文件格式。主要用于指定design内部的Timing关系,约束Power消耗和Area大小。但是在这当中,最为关键的便是指定design的时序。其语法结构是基于TCL语法实现的。主要应用于综合、PR、以及STA过程当中,当然在其他方面也会有很大用途,比如CDC check。现在的SDC可以看做是一项标准的指令系统,基本上所有的EDA工具都可以兼容性识别。

关于SDC更多具体的命令,可以查看下面这份教程。

https://alidocs.dingtalk.com/api/doc/transit?spaceId=5094368790&dentryId=69645565609&corpId=dingcd9df953ab4a15574ac5d6980864d335

Transition: 它是指信号转换时间,也被称为transition time。是指电压从10%VDD上升到90%VDD所需要的时间,或者是从90%VDD下降到10%VDD所需要的时间,当然也可以是20%VDD上升到80%VDD的时间,具体要看timing lib库里面的定义,如:

Falling edge thresholds:

slew_lower_threshold_pct_fall : 10.0;

slew_upper_threshold_pct_fall : 90.0;

Rising edge thresholds:

slew_lower_threshold_pct_rise : 10.0;

slew_upper_threshold_pct_rise : 90.0;

信号上升和下降的转换时间过长意味着该单元内部电路的速度很慢,延时就比较长。在sdc中,用以下命令来限制slew大小。

set_max_transition 0.1 -clock_path [all_clocks]

CELL Delay: 逻辑单元的传播延时。传播延时是指信号从逻辑门的输入端到其输出端所需要的时间。

这里引用一个英文的定义(很多时候用中文来描述专业术语,真的很别扭)

It is defined as the difference between the times when the transitioning input reaches 50% of its final value to the time when the output reaches 50% of the final value showing the effect of input change. 这里50%被定义为逻辑阈值,具体看下图就可以看明白。

以图1中的两输入与门为例。I1端是一个constant,value为1,I2端信号波形如图所示。O为两输入与门的输出。

传播延时取决于以下两大因素:

1.input transition

input transition越小(即fast slew),cell delay越小。在数字后端设计实现中,常常看到cell delay比较大的原因之一就是input transition比较大(transition比较差)导致的。

- output load

输出负载越大,需要给负载充电的时间就越长,因此cell delay也就越大。这里顺便提下,有的时候我们为了balance delay值,可以通过加dummy net来增加load,从而增大latency。

Net Delay: 互连线Inter-connected延时,它是指逻辑net对应的走线延时。走线越长,net delay越大。

Net delay的计算往往是将整个design中的net拆分成若干段来进行的,同时把每段net用某种RC模型来表征。数字后端实现过程中net delay也仅仅是基于特定的delay 模型来进行net delay的估算。PR工具布线后的database需要利用Start-RC 来进行RC 抽取,以SPEF格式的RC文件输出。最后在Timing signoff工具Primetime中读取这个RC spef文件来进行delay的计算。net delay和R*C成正比。

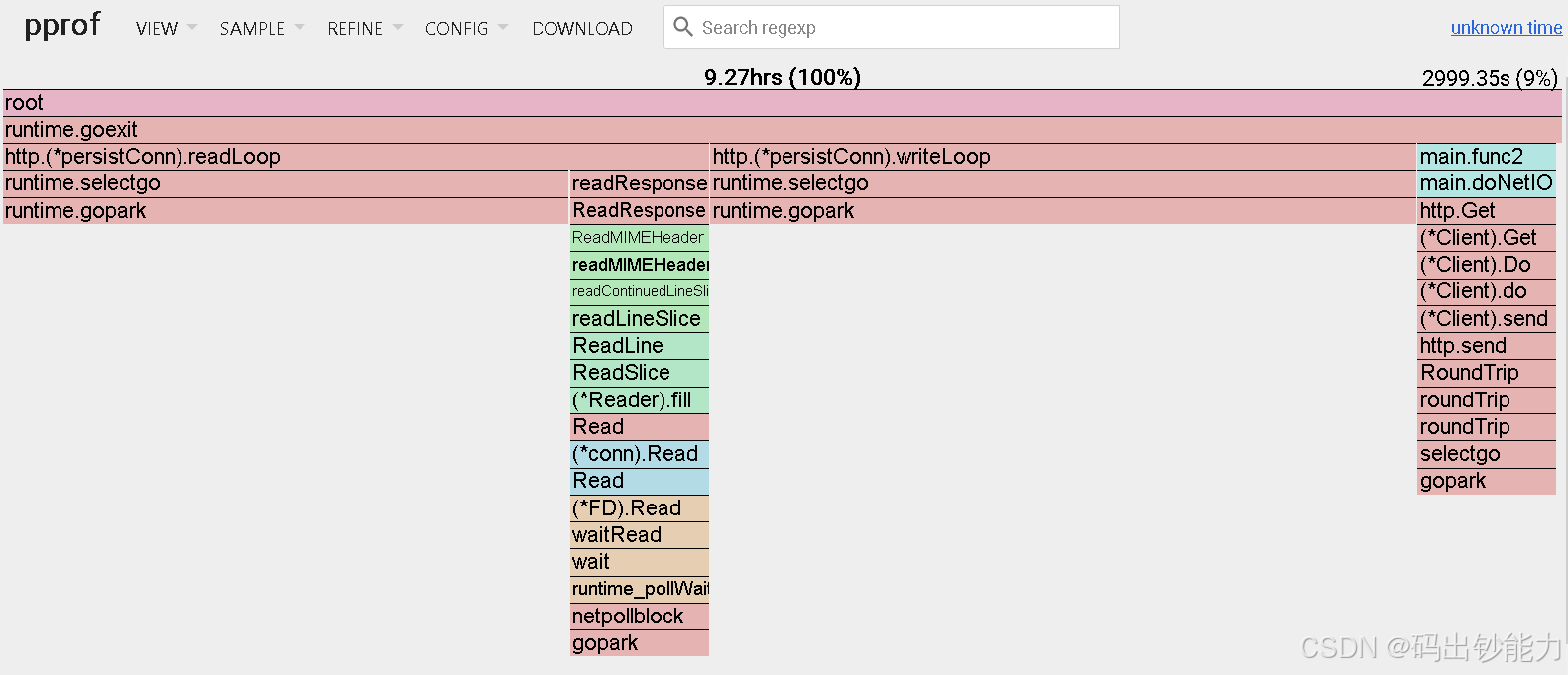

MMMC:Multi mode multi corner,多种工作模块多种工艺角组合下进行timing等check。

随着工艺节点越做越小,timingsignoff阶段需要signoff的corner越来越多。以本次训练营所使用的的TSMC28nm工艺为例,官方给出的timingsignoffcorner要求如下图所示,即setup 检查需要在不同的librarypvt和RCcorner下都能满足我们的spec。

如果我们的PRflow只带一个传统的cworst125和cbestm40去跑flow,布局布线后的timing 可能存在大量的setup和holdviolation(PrimeTime检查)。因此我们就希望工具在PR阶段就能看到其他corner下的timingviolation并对这些violation进行时序的优化。这就引入了MCMM的概念。引入它的好处是后续PT可能signoff会收敛的更快,坏处是PR阶段的runtime会更久。

每个View = Library Set (lib) + RC Corner (QRC) + Constraint Mode