FPGA Xilinx维特比译码器实现卷积码译码

文章目录

- FPGA Xilinx维特比译码器实现卷积码译码

- 1 Xilinx维特比译码器实现

- 2 完整代码

- 3 仿真结果

MATLAB (n,k,m)卷积码原理及仿真代码(你值得拥有)_matlab仿真后代码-CSDN博客

MATLAB 仿真实现任意(n,k,m)卷积码译码_维特比译码matlab-CSDN博客

前面已经使用MATLAB实现了卷积码和译码,前段时间也在项目中实现了Xilinx中维特比译码器,这次就简单介绍一下这个译码器,从项目中把关于卷积码编译码的部分抽取出来 修改了一下,匆促实现了一下,还行。

1 Xilinx维特比译码器实现

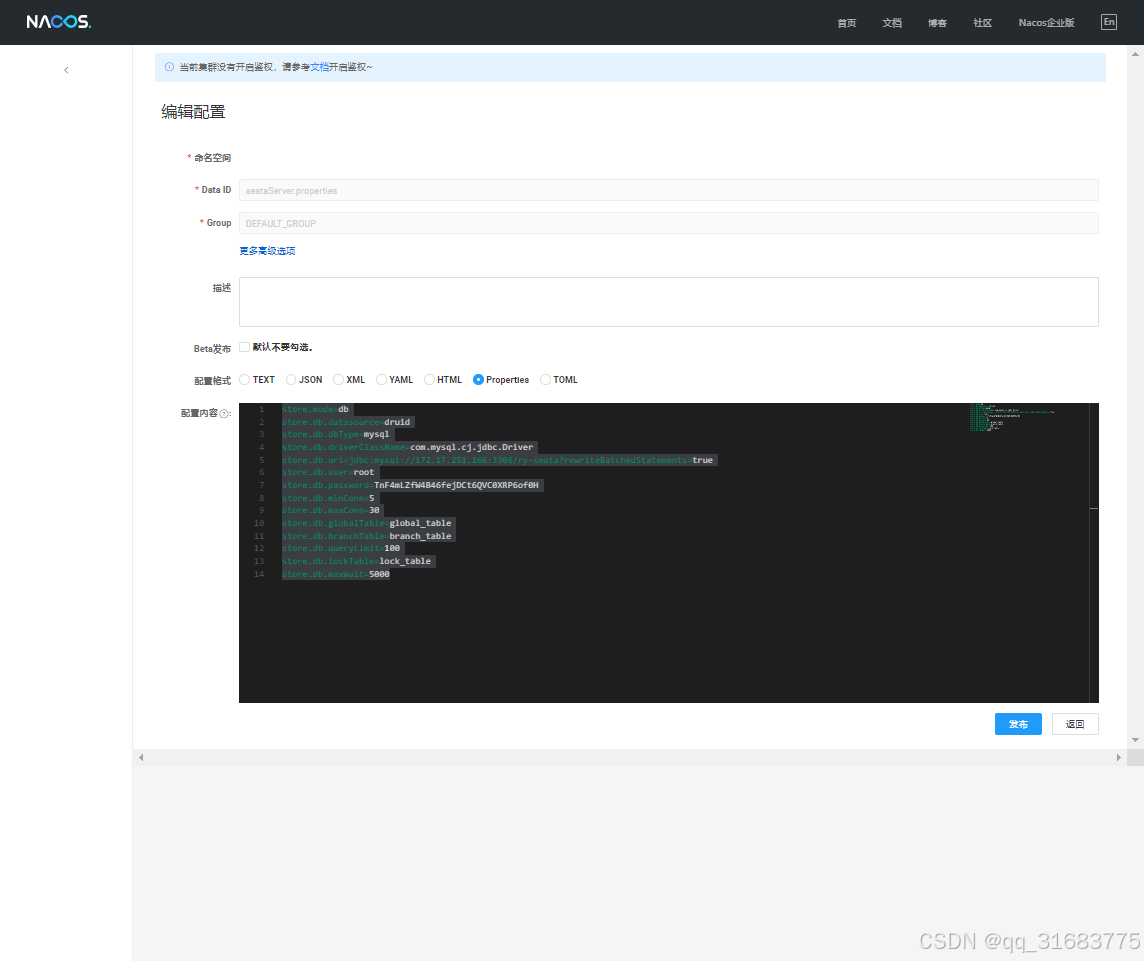

首先找到Viterbi译码器 随便选一个

第一页 别管兄弟们 我也很多不懂什么意思,反正第一个就标准 Standard,第二个就回溯长度 ,兄弟们自己设置。

第二页 的第一个Best State 也不懂,用了之后会多几个看不懂的引脚 第二个Puncturing 好像那个是打孔的意思,我也没用到。第三个Coding是软硬编码的,我选择最简单的硬编码,直接输入0 1 就行了

第三页就是CC编码时的选项了,我编码使用的是1/2CC 然后对应的表达式分别为7 5,所以这里第一个就是2 代表两个输出码元,然后下面的代表的是表达式7 5

第四页第一个BER Options也没用到,用到了也会多几个引脚,没敢用

最后一页就是总结,大家注意上图中 左侧信息 “Implementation Details”

其中第一个DATA_IN_1(8:8) DATA_IN_1(0:0)意思是输入的比特第8位和第0位有效,到时候你只需要把输入的两比特放进这个变量里的第0位和第8位就行了。

DATA(0:0) 就代表每一次输出只有第0位是有效的,也就是一次输入一位 这一位就是第0位

2 完整代码

仿真文件

///

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//接口申明

reg clk;

reg rst_n;

reg input_bit;

reg input_valid;

wire [1:0] output_bits;

wire output_valid;

reg enable;

wire out_data;

wire outdata_valid;

wire over;

reg o_data_end;

// 对被测试的设计进行例化

// 实例化待测试的卷积编码模块

CC2 u_CC2( //二分之一码率 多项式 = 7,5

.clk (clk),

.rst (rst_n),

.enable (enable), //使能信号

.sink_data (input_bit), //输入数据

.sink_valid (input_valid), //数据有效信号

.out_valid (output_valid), //输出数据有效信号

.out_data (output_bits) //输出数据

);

CC2_Decoding u_CC2_Decoding(

.clk (clk),

.rst (rst_n),

.in_data_valid (output_valid), //进来的全是有效数据 直接全部放进译码器中

.in_data (output_bits),

.o_data_end (o_data_end),

.over (over), //结束解码

.out_data (out_data),

.outdata_valid (outdata_valid)

);

//复位和时钟产生

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

integer file; // 文件句柄

//测试激励产生

initial begin

// 打开文件,写入模式

file = $fopen("D:\\out_data.txt", "w");

// 确保文件成功打开

if (file == 0) begin

$display("Error opening file!");

$finish;

end

end

always @(posedge clk) begin

if (outdata_valid) begin // 仅在数据有效时写入

$fdisplay(file, "%d", out_data); // 将Ik写入文件

end

end

initial begin

@(posedge rst_n); //等待复位完成

enable <= 1'b0;

@(posedge clk);

input_bit <= 1'b0;

enable <= 1'b1;

o_data_end <= 1'b0;

@(posedge clk);

repeat(8*16) begin //连续输入8 * 16 *4个bit

@(posedge clk);

input_bit <= 1'b1;

input_valid <= 1'b1; //输入数据有效信号

@(posedge clk);

input_bit <= 1'b1;

@(posedge clk);

input_bit <= 1'b0;

@(posedge clk);

input_bit <= 1'b0;

end

input_valid <= 1'b0; //输入数据有效信号

repeat(3) begin

@(posedge clk);

end

o_data_end <= 1'b1;

enable <= 1'b0;

@(posedge clk);

o_data_end <= 1'b0;

#1000000;

$fclose(file); // 关闭文件

$stop;

end

endmodule

1/2CC卷积码编码

module CC2 ( //二分之一码率 多项弿 = 7,5

input clk,

input rst,

input enable, //使能信号

input sink_data, //输入数据

input sink_valid, //数据有效信号

output reg out_valid, //输出数据有效信号

output reg [1:0] out_data //输出数据

);

// sink_data shift_reg[1] shift_reg[0]

// out_data[1] out_data[0] 7 5

reg [1:0] shift_reg; //移位寄存噿

always @(posedge clk) begin

if(!rst) begin

shift_reg <= 2'b0; //初始化为0

out_valid <= 1'b0; //数据输出无效

out_data <= 2'b0;

end else if(enable) begin

if(sink_valid) begin //检测到数据有效信号拉高

out_data[0] <= sink_data + shift_reg[0];

out_data[1] <= sink_data + shift_reg[1] + shift_reg[0];

out_valid <= 1'b1; //拉高数据输出有效信号

shift_reg <= {sink_data,shift_reg[1]}; //移位

end else begin

out_data <= out_data;

out_valid <= 1'b0;

shift_reg <= shift_reg;

end

end else begin

shift_reg <= 2'b0; //将所有寄存器清零

out_valid <= 1'b0; //数据输出无效

out_data <= 2'b0;

end

end

endmodule

1/2CC卷积码译码

module CC2_Decoding

(

input clk,

input rst,

input in_data_valid, //进来的全是有效数据 直接全部放进译码器中

input [ 1:0] in_data,

input o_data_end,

output reg over, //结束解码

output out_data,

output outdata_valid

);

parameter out_data_hop_amount = 8 * 16 * 4; // 输出所有的有效比特数

wire [ 7:0] decoded_data;

reg [15:0] binary_data;

reg data_valid;

reg [ 10:0] out_data_hop_count; //一跳的输出码元计数器

reg flag;

wire s_axis_data_tready;

wire decoded_valid;

assign out_data = decoded_data[0];

Viterbi2CC_Ip u_Viterbi2CC_Ip(

.aclk (clk),

.aresetn (rst), //低电平就是复位

.binary_data (binary_data), // 输入的硬判决编码数据流(16比特宽度)

.data_valid (data_valid), // 输入数据有效信号

.s_axis_data_tready (s_axis_data_tready),

.decoded_data (decoded_data), // 解码后的输出数据

.decoded_valid (decoded_valid) // 解码输出有效信号

);

assign outdata_valid = (out_data_hop_count < out_data_hop_amount) ? decoded_valid : 0;

always @(posedge clk) begin

if(!rst) begin

data_valid <= 'b0;

binary_data <= 'b0;

end else if(in_data_valid && !flag) begin

data_valid <= 1'b1; //调高数据有效信号

binary_data[8] <= in_data[0];

binary_data[0] <= in_data[1];

end else if(flag && s_axis_data_tready && out_data_hop_count <= out_data_hop_amount)begin

data_valid <= 1'b1;

binary_data <= 'b0;

end else begin

data_valid <= 1'b0;

binary_data <= binary_data;

end

end

//对输出的一跳卷积译码码元计数

always @(posedge clk) begin

if(!rst) begin

over <= 1'b0;

out_data_hop_count <= 'b0;

end else if(decoded_valid && out_data_hop_count <= out_data_hop_amount) begin

//此时还在接收64个输出的有效比特数据

over <= 1'b0;

out_data_hop_count <= out_data_hop_count + 2'd1;

end else if(out_data_hop_count <= out_data_hop_amount) begin

over <= 1'b0;

out_data_hop_count <= out_data_hop_count;

end else begin

over <= 1'b1;

out_data_hop_count <= out_data_hop_count;

end

end

always @(posedge clk) begin

if(!rst) begin

flag <= 'b0;

end else if(o_data_end) begin //数据送完了

flag <= 1'b1;

end else begin

flag <= flag;

end

end

endmodule

维特比译码器

module Viterbi2CC_Ip (

input aclk,

input aresetn,

input [15:0] binary_data, // 输入的硬判决编码数据流(16比特宽度)

input data_valid, // 输入数据有效信号

output s_axis_data_tready,

output reg [7:0] decoded_data, // 解码后的输出数据

output reg decoded_valid // 解码输出有效信号

);

reg [15:0] s_axis_data_tdata;

reg s_axis_data_tvalid;

wire [7:0] m_axis_data_tdata;

wire m_axis_data_tvalid;

reg m_axis_data_tready;

viterbi2CC your_instance_name (

.aclk(aclk), // input wire aclk

.aresetn(aresetn), // input wire aresetn

.s_axis_data_tdata(s_axis_data_tdata), // input wire [15 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.m_axis_data_tdata(m_axis_data_tdata), // output wire [7 : 0] m_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready) // input wire m_axis_data_tready

);

always @(posedge aclk) begin

if (!aresetn) begin

// 复位信号处理

s_axis_data_tvalid <= 'b0;

m_axis_data_tready <= 'b0;

decoded_valid <= 'b0;

decoded_data <= 'b0;

end else begin

if (data_valid && s_axis_data_tready) begin

// 输入有效时,将二进制编码数据发送给解码器

s_axis_data_tdata <= binary_data; // 输入16比特的编码数据

s_axis_data_tvalid <= 1'd1; // 表示输入数据有效

end else begin

s_axis_data_tvalid <= 1'd0;

end

// 解码器输出处理

if (m_axis_data_tvalid) begin

decoded_data <= m_axis_data_tdata; // 获取解码后的数据

decoded_valid <= 1'd1; // 标记解码输出有效

end else begin

decoded_valid <= 1'd0;

end

m_axis_data_tready <= 1'd1; // 准备接收更多解码数据

end

end

endmodule

3 仿真结果

这是multisim中的仿真结果,不好看,直接在MATTAB中看解调出来的数据

最后MATLAB中的数据和仿真输入的数据几乎一模一样,只有后四位不一样,这主要是因为卷积码译码回溯的问题,导致最后几位译码会出现问题。不过问题不大