硬件结构

1.冯诺伊曼模型

运算器,控制器,存储器,输入输出设备

2.内存

程序和数据的存储

3.中央处理器

32位:一次可以计算4字节,64位:一次可以计算8字节

4.总线

-

地址总线:指定CPU将要操作的内存地址

-

数据总线:读写内存的数据

-

控制总线:发送和接受信号

5.CPU读写内存的步骤

首先通过地址总线指定内存地址,然后通过控制总线控制读或写命令,最后通过数据总线传输数据

6.程序执行基本过程

CPU根据程序计数器里的内存地址,从内存里把需要执行的指令读取到寄存器里面执行,根据指令长度自增,顺序读取下一条指令,这个循环过程称为CPU指令周期

7.存储器层次结构

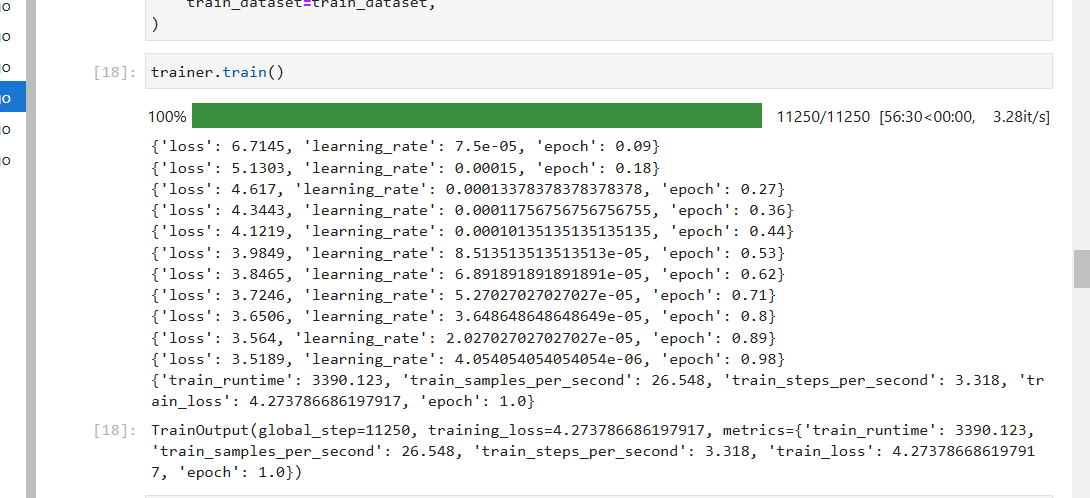

CPU Cache结构

Cache Line是CPU从内存读取数据的基本单位,由Tag(标志)+数据块(Data Block)组成,CPU Cache由多个Cache Line组成,CPU Cache Line除了存放内存中加载的数据以外,还存放有效位,用来标记数据是否有效,若有效位为 0,无论是否有数据都会从内存重新加载。

CPU从CPU Cache 读取数据是读字,因此需要一个偏移量来找Line中的字。

内存的访问地址:组标记,CPU Cache Line索引,偏移量

CPU Cache Line的数据结构:索引,有效位,组标记,数据块

如何让CPU更快

提升缓存命中率

-

数据缓存

按照内存布局顺序访问

-

指令缓存

有规律的条件分支语句让CPU分支预测器发挥作用

8.CPU缓存一致性

为了提升性能,需要使得CPU读取数据尽可能从CPU Cache中读取,少从内存中读取,产生何时需要将Cache中的数据写回内存的问题

-

写直达

如果数据已经在Cache,将数据更新到Cache再写入内存

如果不在Cache,就直接更新到内存

-

写回

发生写操作时,新的数据仅写入Cache Block,只有修改过的Cache Block被替换才写入内存

多核CPU的缓存一致性

满足两点:

-

写传播:也就是当某个 CPU 核心发生写入操作时,需要把该事件广播通知给其他核心

-

事物串行化

MESI协议满足了上述要求,用M(已修改),E(独占),S(共享),I(已失效)四个状态来表示CPU Cache Line

![[Meachines] [Medium] MonitorsThree SQLI+Cacti-CMS-RCE+Duplicati权限提升](https://img-blog.csdnimg.cn/img_convert/ec0a89c20cb3cca3b2df26efab562a59.jpeg)