今天没有具体的数字IC后端lab实验。今天的重点是熟悉掌握静态时序分析STA中的几类timing path以及setup和hold检查机制(包含setup和hold计算公式)。

芯片流片失败的那些故事

数字后端零基础入门系列 | Innovus零基础LAB学习Day5

等大家把今天内容学习完,建议做下下面这道数字后端经典时序计算题,每年秋招必考题目。

对于如下电路图:

1.求出该电路所能达到的最大频率? (10分)

2时钟频率为50M,该电路是否有时序违规?如果有,写出计算过程,并给出修改意见.(10分)

图中Timing参数解释:

Thold Hold time最小时间

TSu Setup time最小时间

TCq Clock-> Q delay

输入IN的Input Delay恒为0.5ns.

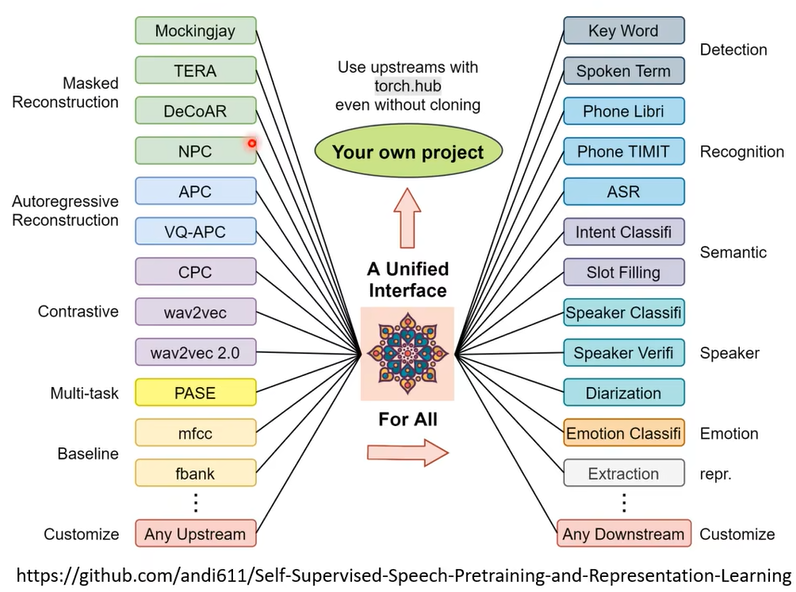

静态时序分析STA中四种基本Timing Path: 静态时序分析时,工具会把设计拆成四种基本path来做时序分析。无论设计有多复杂,也只有这四种情况。它包含in2reg,reg2reg,reg2out,in2out(feedthrough)。

四种基本时序路径

PATH1: 输入端口input-----------> 寄存器的数据输入端 (in2reg path)

PATH2: 寄存器CLK------------> 寄存器的数据输入端 (reg2reg path, 内部路径)

PATH3: 寄存器CLK-------------> 输出端口output (reg2out path)

PATH4: 输入端口input-------------> 输出端口output (feedthrough path,直通路径)

所以,知道了这四种基本timing path后,我们就知道每种路径对应的起点和终点,即timing report中的start point 和endpoint。

EndPoint: 时序path上的终点。

从上面的介绍我们就可以知道有效的endpoint必须是以下几种情况:

1)寄存器/macro的数据输入端

2)输出端口port

StartPoint: 时序path上的起点。

与之对应,startpoint必须是以下几种情况:

1)寄存器/macro的时钟输入引脚(或输出端)

2)输入端口port

Clock Path: 时钟路径,它是指时钟树上的clock tree。

Data Path: 数据路径,它包括数据路径上的组合逻辑。

Clock path和Data path对应的路径已经标注在下图。

从时钟定义端口到寄存器(macro和IP)时钟端的路径,我们称之为时钟路径,即Clock path。

除了clock path外,其他都属于数据路径,即data path。比如上面两个寄存器之间的逻辑路径就是data path。

Launch Flop &Capture Flop:Launch Flop就是指发送数据的寄存器,而Capture Flop是指接收(采样捕捉)数据的寄存器。值得注意的是这是相对某一条path来说的。对于input到reg的时序路径,这颗reg是capture flop,但对从这颗reg到下一个reg的路径来说,这个reg就是launch flop(Flop就是寄存器的意思)。

Launch clock path & Capture clock path:有了上面这些铺垫后,launch clock path和capture clock path就很清晰了。对于下图所示的这条timing path来说,UFF0就是launch Flop,UFF1是capture Flop。

所以,launch clock path就是从CLKM port到UFF0/CK 的路径。capture clock path就是从CLKM port到UFF1/CK的路径(这里是举同步的例子,寄存器的时钟源头都是CLKM)。

那么,自然而然所谓的common clock path就是launch clock path和capture clock path共同的部分,即下图所示的前面两颗clock inverter(buffer)。

Setup Time: 静态时序分析中最基本的就是setup和hold时序分析,其检查的是触发器时钟端CK与数据输入端D之间的时序关系。Setup time是指在时钟有效沿(下图为上升沿)之前,数据输入端信号必须保持稳定的最短时间。setup time值工具是根据查找时序库lib来获取的,它和两个input transition值有关。

Hold time: 它是指在时钟有效沿(下图为上升沿)之后,数据输入端信号必须保持稳定的最短时间。hold time时序检查确保新数据不会在触发器稳定输出初始数据之前过早到达D端而覆盖其初始数据。

Setup & Hold详细分析

以下图电路为例来分析建立时间及保持时间。发送数据的触发器称为Launch flip-flop,接收/捕获数据的触发器称为Capture flip-flop。两触发器时钟端信号为同一时钟。

如下图所示,launch_path为:

CLKM→BUF(launch)→UFF0/CK→UFF0/Q→Comb_logic→UFF1/D;

capture path为: CLKM→BUF(capture)→UFF1/CK;

(1)Setup Time

两触发器间的数据传输通常需要在一个时钟周期内完成。

数据到达UFF1/D所需时间Arrival time为:

Ta = T_launch + T_ck2q + T_dp

满足setup要求时所允许的最长时间Required time为:

Tr = T_capture + T_clk - T_setup

因此setup time要求可表示为:Tr - Ta = T_margin >= 0。

根据setup time要求还可表示为:

T_launch + T_ck2q + T_dp + T_margin + T_setup = T_capture + T_clk

其中:

T_launch:CLKM到UFF0时钟端CK的延时

T_ck2q:UFF0的CK->Q的传输时间

T_dp:组合逻辑延时

T_margin:设计裕量

T_setup:UFF1的setup时间要求

T_capture:CLKM到UFF1时钟端CK的延时

T_clk: 时钟周期

由此可见,setup检查发生在不同时钟边沿,与时钟频率有关。

(2)Hold Time

数据到达UFF1/D所需时间Arrival time为:

Ta = T_launch + T_ck2q + T_dp

满足hold要求时所允许的最短时间Required time为:

Tr = T_capture + T_hold

因此hold time要求可表示为:Ta - Tr = T_margin >= 0。

hold time还可表示为:

T_launch + T_ck2q + T_dp = T_capture + T_hold + T_margin

其中:

T_launch:CLKM到UFF0时钟端CK的延时

T_ck2q:UFF0的CK->Q的传输时间

T_dp:组合逻辑延时

T_hold:UFF1的hold时间要求

T_margin:设计裕量

T_capture:CLKM到UFF1时钟端的延时

T_clk: 时钟周期

由此可见,hold检查发生在同一时钟边沿,与时钟频率无关。