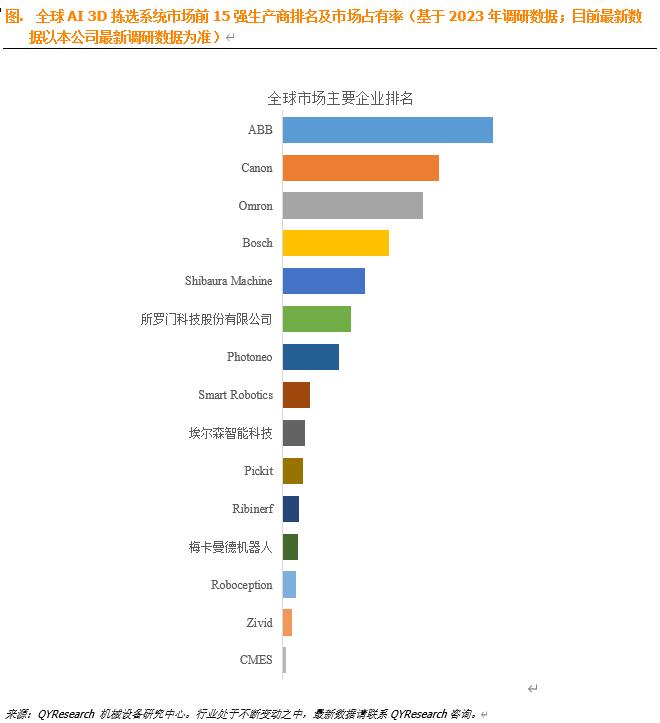

时钟切换电路

- 1.基本概念-相关时钟源和无关时钟源

- 2.基本的时钟切换电路(组合逻辑)

- 2.相关时钟源无毛刺时钟切换电路

- 3.非相关时钟源无毛刺时钟切换电路

1.基本概念-相关时钟源和无关时钟源

相关时钟源:时钟信号源之间存在某种同步或关联的关系。这些信号源之间的频率和相位可能经过精确的调整和匹配,以确保它们能够在特定的应用场景中协同工作;

无关时钟源:时钟信号源之间不存在明确同步或关联的关系。这些时钟源具有不同的频率、相位和抖动特性,因此他们之间的相对关系可能不确定。所以在设计和使用无光时钟源时,需要考虑如何避免或减少由于时钟信号之间的不匹配而可能导致的性能问题。

2.基本的时钟切换电路(组合逻辑)

(1)电路图

(2)原理

通过SELECT信号进行时钟选通;

(3)仿真

分析:可以看出,时钟顺利切换,但是可能存在毛刺;

2.相关时钟源无毛刺时钟切换电路

(1)电路图

(2)原理

SELECT信号为高,CLK1支路导通,输出CLK1;

SELECT信号由高向底发生变化:

Q触发器下降沿触发,保证了时钟脉冲是完整的;

反馈结构,保证了新时钟有效,是在旧时钟失效之后;

SELECT信号为低,CLK0支路导通,输出CLK0;

(3)仿真

(4)注意点

一个支路接入SELECT信号,另外一个支路接入的SELECT信号要取反;

触发器是下降沿触发;

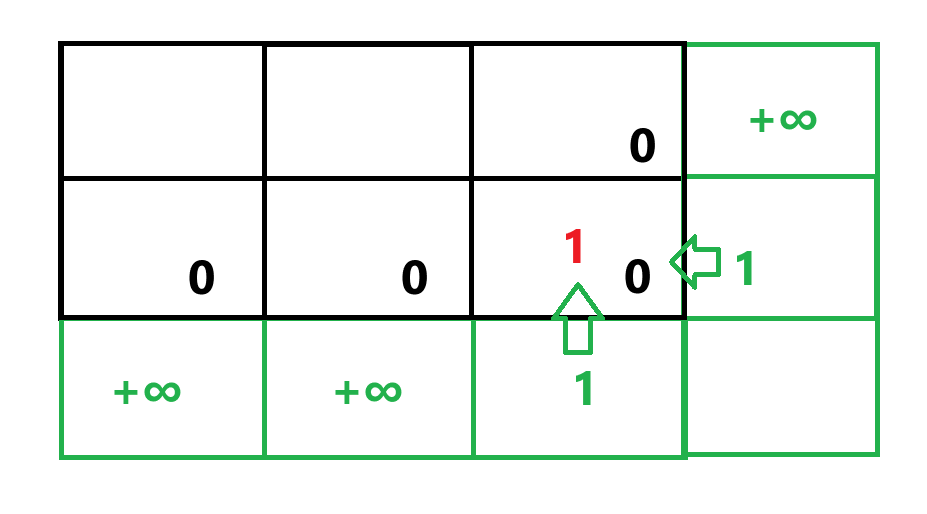

3.非相关时钟源无毛刺时钟切换电路

(1)电路图

(2)原理

增加一级上升沿触发的D触发器,降低非相关时钟存在的亚稳态问题;

(3)仿真

![[含文档+PPT+源码等]精品基于Nodejs实现的医院问诊系统的设计与实现](https://img-blog.csdnimg.cn/img_convert/813da755b48b27014b0d5e96affa1a51.png)