-指令流水线

-基础知识

1.流水线技术通过多个功能部件并行工作来缩短程序执行时间,提高处理器的效率和吞吐率

2.增加流水线级数,可以简化流水线的各级逻辑,进一步提高了处理器的性能

3.以三级流水线分析:

pc代表程序计数器,流水线使用三个阶段,因此指令分为三个阶段执行:

1>取指(从存储器装载一条指令)

2>译码(识别将要执行的指令)

3>执行(处理指令并将结果写入寄存器)

(**注:pc值=当前程序执行位置+8)

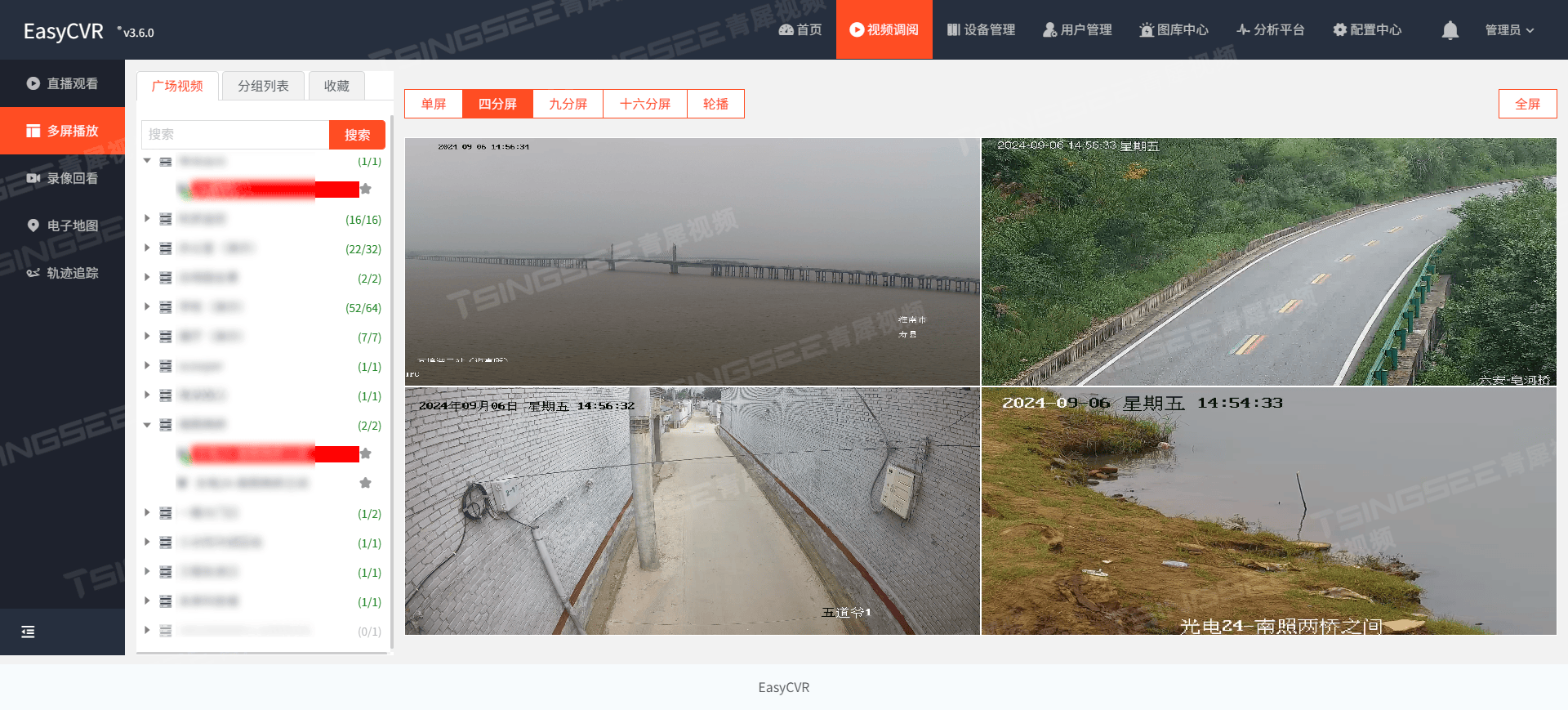

-流水线的几种情况总结

-单周期指令--一步到位

描述:

1.上图仅为处理简单的寄存器操作指令(不包括存储器访问指令和跳转指令)

(存在存储器访问指令,跳转指令的情况下会出现流水线阻断情况,导致流水线的性能下降,上图给出的是流水线的最佳运行情况)

2.上图中的MOV,ADD,SUB...等指令为单周期指令,并且都是简单的寄存器指令

3.上图从T1开始,用3个时钟周期执行了3条命令,指令平均周期数(CPI)等于1个时钟周期

分步指令--有先有后

流水线阻断的原因和过程:仅有一个线作为数据和地址传输,所以执行LDR/STR指令,线被占用,等待LDR指令执行结束,数据/地址总线才会被释放

流水线阻断的原因和过程:仅有一个线作为数据和地址传输,所以执行LDR/STR指令,线被占用,等待LDR指令执行结束,数据/地址总线才会被释放

描述:

对存储器的访问指令LDR就是非单周期指令,这类指令在执行阶段,首先要进行存储器的地址计算,占用控制信号线,而译码的过程同样需要占据控制信号线,所以下一条指令的译码被阻断,并且由于LDR访问存储器和回写寄存器的过程中需要继续占用执行单元,所以下一条的执行也被阻断;由于采用冯.诺依曼体系结构,不能同时访问数据存储器和指令存储器,当LDR处于访存周期的过程中时,EOR指令的取指被切断,因此处理器用8个时钟周期执行了6条指令,指令的平均周期(CPI)=1.35个时钟周期

-分支流水线--跳转指令

(BL执行过程中包括俩个附加操作--写链接寄存器和调整程序指针,这俩个操作仍然占用执行单元,这时处于译码(D)和取指(F)的流水线被阻断)

BL指令:

1.找地址(link)--- 连接相关地址 --- 冯诺依曼一根线被占用

2.跳转(B)--- 跳转到相关位置 --- 冯诺依曼一根线被占用

3.执行完上面俩个步骤后,BL指令才执行结束,此时跳到被连接的指令,SUB和ORR指令被抛弃

-中断(进入异常模式)-- 随时来

(中断发生后,不打断当前正在执行的指令,即等待当前指令执行结束;执行完当前指令再去处理中断)

发生异常后,CPU进入异常模式,硬件执行以下六步:

1.当前指令执行阶段:当有中断发生时,当前指令在执行

2.中断处理入口:当前指令执行结束后,处理中断

3.解码阶段:DI—中断使能,设置相应标志位—进入ARM态—异常向量表的跳转start.S

4.中断处理:EI—中断处理—void do—irq

5.连接(LR寄存器)地址—跳转会ARM指令程序中—LR

6.修正返回地址—pc = lr -4