文章目录

- 前言

- 一、跟着官方文档走一遍

- 二、cache子模块的波形仿真

- 2.1 必要的文件内容解释

- 2.2 cache子模块波形仿真——目前环境没啥问题了,就vcd因为配置问题出不来

- 总结

前言

看了那么久的verilog代码和文档,但还是没怎么接触过Vortex GPGPU全流程跑通与功能模块的波形显示。这一节就开始尝试探索这块内容。

一、跟着官方文档走一遍

已经有博客做了流程尝试,看了是通过容器保存运行环境的,我呢,还是老老实实按照流程走!

主要还是参考这个文档:https://github.com/vortexgpgpu/vortex/blob/master/docs/install_vortex.md

我用的是ubuntu18.04镜像,能在vmware上跑通,但还是有些坑点(苦,用了一晚上从vmware开始搭建环境搭完测试例子,很久没接触了,一堆坑,果然代理还是有必要的),我在下面注释中会提到:

# step 1. 安装依赖

sudo apt-get install build-essential zlib1g-dev libtinfo-dev libncurses5 uuid-dev libboost-serialization-dev libpng-dev libhwloc-dev

# step 2. 升级到g++-11和gcc-11

# 展开一下,ubuntu18.04默认的gcc和g++版本是7.4,没有11的ppa源,因此只能在添加ppa源以后再进行安装

sudo add-apt-repository ppa:ubuntu-toolchain-r/test

sudo apt update & upgrade

sudo apt install gcc-11 g++-11

# 随后修改gcc和g++运行版本

sudo update-alternatives --install /usr/bin/g++ g++ /usr/bin/g++-11 11

# step 3. 下载vortex gpgpu包

git clone --depth=1 --recursive https://github.com/vortexgpgpu/vortex.git

# 多提一嘴,这个步骤有点麻烦,国内下载速度慢

# 我用了proxychains4和socks5通过主机代理加速下载,具体怎么配合不能说太多,我贴个链接

# https://blog.csdn.net/weixin_48915167/article/details/136705698

# 加速器方案自个儿确定

# 在有proxychains4的情况下,使用

proxychains4 git clone --depth=1 --recursive https://github.com/vortexgpgpu/vortex.git

# 可以加速下载

# step4. build vortex

cd vortex

mkdir -p build

cd build

../configure --xlen=32 --tooldir=$HOME/tools

#./ci/toolchain_install.sh --all # 这一步略麻烦,需要下载包,否则不太能成功,建议改为如下:

proxychains4 ./ci/toolchain_install.sh --all

source ./ci/toolchain_env.sh

make -s

# 至此环境搭建完毕

# step 5. 跑一个简单例子——Quick demo running vecadd OpenCL kernel on 2 cores

./ci/blackbox.sh --cores=2 --app=vecadd

跟官网大差不大,差异点只在于国内下载包速度不快而加了proxychains4(快到起飞)以及为gcc/g++升级而多做的事儿!

step 5跑完的结果如下:

root@ubuntu:/home/dention/vortex/vortex/build# ./ci/blackbox.sh --cores=2 --app=vecadd

CONFIGS=-DNUM_CLUSTERS=1 -DNUM_CORES=2 -DNUM_WARPS=4 -DNUM_THREADS=4

running: CONFIGS=-DNUM_CLUSTERS=1 -DNUM_CORES=2 -DNUM_WARPS=4 -DNUM_THREADS=4 make -C ./ci/../runtime/simx

running: make -C ./ci/../tests/opencl/vecadd run-simx

make: Entering directory '/home/dention/vortex/vortex/build/tests/opencl/vecadd'

g++ -std=c++11 -Wall -Wextra -Wfatal-errors -Wno-deprecated-declarations -Wno-unused-parameter -Wno-narrowing -pthread -I/root/tools/pocl/include -O2 -DNDEBUG -c /home/dention/vortex/vortex/tests/opencl/vecadd/main.cc -o main.cc.o

In file included from /root/tools/pocl/include/CL/cl.h:20,

from /root/tools/pocl/include/CL/opencl.h:24,

from /home/dention/vortex/vortex/tests/opencl/vecadd/main.cc:5:

/root/tools/pocl/include/CL/cl_version.h:22:104: note: ‘#pragma message: cl_version.h: CL_TARGET_OPENCL_VERSION is not defined. Defaulting to 300 (OpenCL 3.0)’

22 | TARGET_OPENCL_VERSION is not defined. Defaulting to 300 (OpenCL 3.0)")

| ^

g++ -std=c++11 -Wall -Wextra -Wfatal-errors -Wno-deprecated-declarations -Wno-unused-parameter -Wno-narrowing -pthread -I/root/tools/pocl/include -O2 -DNDEBUG main.cc.o -Wl,-rpath,/root/tools/llvm-vortex/lib -L/home/dention/vortex/vortex/build/runtime -lvortex -L/root/tools/pocl/lib -lOpenCL -o vecadd

cp /home/dention/vortex/vortex/tests/opencl/vecadd/kernel.cl kernel.cl

LD_LIBRARY_PATH=/root/tools/pocl/lib:/home/dention/vortex/vortex/build/runtime:/root/tools/llvm-vortex/lib: POCL_VORTEX_XLEN=32 LLVM_PREFIX=/root/tools/llvm-vortex POCL_VORTEX_BINTOOL="OBJCOPY=/root/tools/llvm-vortex/bin/llvm-objcopy /home/dention/vortex/vortex/kernel/scripts/vxbin.py" POCL_VORTEX_CFLAGS="-march=rv32imaf -mabi=ilp32f -O3 -mcmodel=medany --sysroot=/root/tools/riscv32-gnu-toolchain/riscv32-unknown-elf --gcc-toolchain=/root/tools/riscv32-gnu-toolchain -fno-rtti -fno-exceptions -nostartfiles -nostdlib -fdata-sections -ffunction-sections -I/home/dention/vortex/vortex/build/hw -I/home/dention/vortex/vortex/kernel/include -DXLEN_32 -DNDEBUG -Xclang -target-feature -Xclang +vortex -Xclang -target-feature -Xclang +zicond -mllvm -disable-loop-idiom-all" POCL_VORTEX_LDFLAGS="-Wl,-Bstatic,--gc-sections,-T/home/dention/vortex/vortex/kernel/scripts/link32.ld,--defsym=STARTUP_ADDR=0x80000000 /home/dention/vortex/vortex/build/kernel/libvortex.a -L/root/tools/libc32/lib -lm -lc /root/tools/libcrt32/lib/baremetal/libclang_rt.builtins-riscv32.a" VORTEX_DRIVER=simx ./vecadd -n64

Workload size=64

Create context

Allocate device buffers

Create program from kernel source

Upload source buffers

Execute the kernel

Elapsed time: 210 ms

Download destination buffer

Verify result

PASSED!

PERF: core0: instrs=5000, cycles=11921, IPC=0.419428

PERF: core1: instrs=5000, cycles=11922, IPC=0.419393

PERF: instrs=10000, cycles=11922, IPC=0.838785

make: Leaving directory '/home/dention/vortex/vortex/build/tests/opencl/vecadd'

官网的其他md还有一些测试例子,不举例了。但总结下来会发现,这些都是系统层面测试的例子(看结果出现了系统profiler的常见类型的结果),后面可能有探索的必要,先赊账。

目前先看verilog子模块的功能实现。

二、cache子模块的波形仿真

这个没啥.md文件当作参考了,只能看看unittest中有无线索。看一下文件结构:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# tree

.

├── cache

│ ├── cachesim.cpp

│ ├── cachesim.h

│ ├── Makefile

│ ├── ram.h

│ └── testbench.cpp

├── cache_top

│ ├── main.cpp

│ └── Makefile

├── common

│ └── vl_simulator.h

├── common.mk

├── core_top

│ ├── main.cpp

│ └── Makefile

├── generic_queue

│ ├── main.cpp

│ └── Makefile

├── issue_top

│ ├── main.cpp

│ └── Makefile

├── Makefile

└── mem_streamer

├── Makefile

├── memsim.cpp

├── memsim.h

├── ram.cpp

└── ram.h

7 directories, 21 files

2.1 必要的文件内容解释

主文件下的Makefile定义了项目的构建目标(如all、clean、run等)和一些特定的构建规则,通常包含了项目的构建逻辑,并且会调用其他Makefile或mk文件来包含共用的构建规则。其内容:

all:

$(MAKE) -C cache

$(MAKE) -C generic_queue

$(MAKE) -C mem_streamer

$(MAKE) -C cache_top

$(MAKE) -C core_top

$(MAKE) -C issue_top

run:

$(MAKE) -C cache run

$(MAKE) -C generic_queue run

$(MAKE) -C mem_streamer run

$(MAKE) -C cache_top run

$(MAKE) -C core_top run

$(MAKE) -C issue_top run

clean:

$(MAKE) -C cache clean

$(MAKE) -C generic_queue clean

$(MAKE) -C mem_streamer clean

$(MAKE) -C cache_top clean

$(MAKE) -C core_top clean

$(MAKE) -C issue_top clean

很符合一般的Makefile编写规则,这里的$(MAKE)表示这里的make规则应该有自定义部分。在Makefile中使用$(MAKE)而不是直接写make有几个好处:

1. 可移植性:如果需要在不同的构建系统或环境中使用Makefile,可以通过改变MAKE变量的值来适应不同的构建工具。

2. 灵活性:可以在Makefile中定义MAKE变量的值,例如添加特定的参数或选项,以控制make的行为。

(这部分参考kimichat的回答。kimichat,打广告费,>.<)

接下来看下主文件夹下的common.mk,带注释的代码如下:

# 设置默认的安装目录为当前目录

DESTDIR ?= .

# 配置和参数变量为空,可以在其他地方追加

CONFIGS +=

PARAMS +=

# 设置C++编译器标志

CXXFLAGS += -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds

# 启用位置无关代码生成,关闭某些警告

CXXFLAGS += -fPIC -Wno-maybe-uninitialized

# 添加配置标志

CXXFLAGS += $(CONFIGS)

# 链接器标志为空

LDFLAGS +=

# RTL包为空

RTL_PKGS +=

# RTL包含路径为空

RTL_INCLUDE +=

# 定义调试标志

DBG_FLAGS += -DDEBUG_LEVEL=$(DEBUG) -DVCD_OUTPUT $(DBG_TRACE_FLAGS)

# 定义Verilator的标志

VL_FLAGS = --exe

# 使用Verilog 2009标准,启用断言和所有警告

VL_FLAGS += --language 1800-2009 --assert -Wall -Wpedantic

# 禁用某些警告

VL_FLAGS += -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED

# 设置X初始化策略

VL_FLAGS += --x-initial unique --x-assign unique

# 定义模拟和SV DPI宏

VL_FLAGS += -DSIMULATION -DSV_DPI

# 添加配置和参数

VL_FLAGS += $(CONFIGS)

VL_FLAGS += $(PARAMS)

# 添加RTL包含路径

VL_FLAGS += $(RTL_INCLUDE)

# 添加RTL包

VL_FLAGS += $(RTL_PKGS)

# 指定顶层模块

VL_FLAGS += --cc $(TOP) --top-module $(TOP)

# 启用Verilator多线程模拟

THREADS ?= $(shell python -c 'import multiprocessing as mp; print(mp.cpu_count())')

VL_FLAGS += -j $(THREADS)

#VL_FLAGS += --threads $(THREADS) # 另一种多线程选项

# 调试配置

ifdef DEBUG

# 启用Verilator跟踪和结构跟踪

VL_FLAGS += --trace --trace-structs $(DBG_FLAGS)

# 添加调试信息和优化级别

CXXFLAGS += -g -O0 $(DBG_FLAGS)

else

# 定义NDEBUG宏

VL_FLAGS += -DNDEBUG

# 设置优化级别

CXXFLAGS += -O2 -DNDEBUG

endif

# 性能计数器配置

ifdef PERF

VL_FLAGS += -DPERF_ENABLE

CXXFLAGS += -DPERF_ENABLE

endif

# 默认目标,构建项目

all: $(DESTDIR)/$(PROJECT)

# 构建项目目标

$(DESTDIR)/$(PROJECT): $(SRCS)

# 使用Verilator构建项目

# $@ 是一个自动变量,它代表当前规则中的目标(target)文件名。当你在编写规则时,可以使用 $@ 来引用这个目标。

# $< 是一个自动变量,它代表当前规则中的第一个依赖(dependency)文件名。在规则中使用 $< 可以引用规则依赖列表中的第一个文件。

verilator --build $(VL_FLAGS) $^ -CFLAGS '$(CXXFLAGS)' -o ../$@

# 运行项目目标

run: $(DESTDIR)/$(PROJECT)

# 运行项目

$(DESTDIR)/$(PROJECT)

# 波形查看目标

waves: trace.vcd

# 使用GTKwave查看波形

gtkwave -o trace.vcd

# 清理目标

clean:

# 清理构建产物

rm -rf *.vcd obj_dir $(DESTDIR)/$(PROJECT)

所以需要在ubuntu下安装gtkwave和verilator。

接下来看下主文件夹下的cache子文件夹,如下:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest/cache# tree

.

├── cachesim.cpp

├── cachesim.h

├── Makefile

├── ram.h

└── testbench.cpp

0 directories, 5 files

看一下这里的Makefile:

# 获取工程的根目录,即上两级目录的绝对路径

ROOT_DIR := $(realpath ../../..)

# 包含根目录下的配置文件

include $(ROOT_DIR)/config.mk

# 定义项目名称

PROJECT := cache

# 定义RTL源代码目录

RTL_DIR := $(VORTEX_HOME)/hw/rtl

# 定义DPI源代码目录

DPI_DIR := $(VORTEX_HOME)/hw/dpi

# 定义单元测试源代码目录

SRC_DIR := $(VORTEX_HOME)/hw/unittest/$(PROJECT)

# 设置C++编译器标志,包括头文件的搜索路径

CXXFLAGS := -I$(SRC_DIR) -I$(VORTEX_HOME)/hw/unittest/common -I$(VORTEX_HOME)/sim/common

# 添加硬件源代码目录到头文件搜索路径

CXXFLAGS += -I$(ROOT_DIR)/hw

# 定义源文件列表

SRCS := $(DPI_DIR)/util_dpi.cpp

SRCS += $(SRC_DIR)/cachesim.cpp $(SRC_DIR)/testbench.cpp

# 定义调试跟踪标志

DBG_TRACE_FLAGS := -DDBG_TRACE_CACHE

# 定义RTL包路径

RTL_PKGS := $(RTL_DIR)/VX_gpu_pkg.sv

# 设置RTL代码的头文件搜索路径

RTL_INCLUDE := -I$(RTL_DIR) -I$(DPI_DIR) -I$(RTL_DIR)/libs

RTL_INCLUDE += -I$(RTL_DIR)/interfaces -I$(RTL_DIR)/mem -I$(RTL_DIR)/cache

# 定义顶层模块名称

TOP := VX_cache_top

# 包含通用构建规则和变量定义

include ../common.mk

每个子模块下的Makefile都include了common.mk和根目录下的config.mk,都用于配置编译选项和指定依赖。所以比较直观的是,这些约束都用于unittest主文件下的Makefile文件。我们为了方便,减少编译内容,将Makefile削减为:

all:

$(MAKE) -C cache

#$(MAKE) -C generic_queue

#$(MAKE) -C mem_streamer

#$(MAKE) -C cache_top

#$(MAKE) -C core_top

#$(MAKE) -C issue_top

run:

$(MAKE) -C cache run

#$(MAKE) -C generic_queue run

#$(MAKE) -C mem_streamer run

#$(MAKE) -C cache_top run

#$(MAKE) -C core_top run

#$(MAKE) -C issue_top run

clean:

$(MAKE) -C cache clean

#$(MAKE) -C generic_queue clean

#$(MAKE) -C mem_streamer clean

#$(MAKE) -C cache_top clean

#$(MAKE) -C core_top clean

#$(MAKE) -C issue_top clean

只仿真cache模块。

2.2 cache子模块波形仿真——目前环境没啥问题了,就vcd因为配置问题出不来

先在ubuntu安装gtkwave和verilator:

sudo apt-get install gtkwave verilator

改东西,先回到主目录:

root@ubuntu:/home/dention/vortex/vortex# tree -L 1

.

├── blackbox.simx.cache

├── build

├── ci

├── config.mk.in

├── configure

├── docs

├── hw

├── kernel

├── LICENSE

├── Makefile.in

├── miscs

├── perf

├── README.md

├── runtime

├── sim

├── tests

└── third_party

11 directories, 6 files

修改俩文件名:

mv config.mk.in config.mk

mv Makefile.in Makefile

随后在./vortex/hw/unittest下运行makefile,报错:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make all

make -C cache

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

make[1]: *** No rule to make target '@VORTEX_HOME@/hw/dpi/util_dpi.cpp', needed by 'cache'. Stop.

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

Makefile:2: recipe for target 'all' failed

make: *** [all] Error 2

原因是DPI_DIR变量使用了$(VORTEX_HOME),但错误信息显示@VORTEX_HOME@,这意味着 VORTEX_HOME没有被正确替换。接着改:

# 在cache目录下的Makefile中定义VORTEX_HOME

# 定义 VORTEX_HOME

VORTEX_HOME := $(ROOT_DIR)

# 测试一下路径

info-roots:

@echo "ROOT_DIR is set to $(ROOT_DIR)"

直接在cache子目录下运行make即可:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest/cache# vim Makefile

root@ubuntu:/home/dention/vortex/vortex/hw/unittest/cache# make

ROOT_DIR is set to /home/dention/vortex/vortex

好了,没问题了,能找到!接着下一步!

make all

结果是:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make all

make -C cache

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

ROOT_DIR is set to /home/dention/vortex/vortex

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

#make -C generic_queue

#make -C mem_streamer

#make -C cache_top

#make -C core_top

#make -C issue_top

最起码不报错了,这一步应该输出不了什么东西!

接着运行make run:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make run

make -C cache run

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

verilator --build --exe --language 1800-2009 --assert -Wall -Wpedantic -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -j 1 -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG' -o ../cache

%Error: Invalid Option: --build

%Error: Command Failed /usr/bin/verilator_bin --build --exe --language 1800-2009 --assert -Wall -Wpedantic -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -j 1 -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG' -o ../cache

../common.mk:50: recipe for target 'cache' failed

make[1]: *** [cache] Error 10

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

Makefile:10: recipe for target 'run' failed

make: *** [run] Error 2

经过若干次对vortex/hw/unittest/common.mk的修改之后:

DESTDIR ?= .

CONFIGS +=

PARAMS +=

CXXFLAGS += -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds

CXXFLAGS += -fPIC -Wno-maybe-uninitialized

CXXFLAGS += $(CONFIGS)

LDFLAGS +=

RTL_PKGS +=

RTL_INCLUDE +=

DBG_FLAGS += -DDEBUG_LEVEL=$(DEBUG) -DVCD_OUTPUT $(DBG_TRACE_FLAGS)

VL_FLAGS = --exe

VL_FLAGS += --language 1800-2009 --assert

VL_FLAGS += -Wno-DECLFILENAME -Wno-REDEFMACRO

VL_FLAGS += --x-initial unique --x-assign unique

VL_FLAGS += -DSIMULATION -DSV_DPI

VL_FLAGS += $(CONFIGS)

VL_FLAGS += $(PARAMS)

VL_FLAGS += $(RTL_INCLUDE)

VL_FLAGS += $(RTL_PKGS)

VL_FLAGS += --cc $(TOP) --top-module $(TOP)

# Enable Verilator multithreaded simulation

THREADS ?= $(shell python -c 'import multiprocessing as mp; print(mp.cpu_count())')

# Debugging

ifdef DEBUG

VL_FLAGS += --trace --trace-structs $(DBG_FLAGS)

CXXFLAGS += -g -O0 $(DBG_FLAGS)

else

VL_FLAGS += -DNDEBUG

CXXFLAGS += -O2 -DNDEBUG

endif

# Enable perf counters

ifdef PERF

VL_FLAGS += -DPERF_ENABLE

CXXFLAGS += -DPERF_ENABLE

endif

all: $(DESTDIR)/$(PROJECT)

$(DESTDIR)/$(PROJECT): $(SRCS)

verilator $(VL_FLAGS) $^ -CFLAGS '$(CXXFLAGS)' --output-split 20000

@$(MAKE) -C obj_dir -f V$(TOP).mk -j $(THREADS)

run: $(DESTDIR)/$(PROJECT)

$(DESTDIR)/$(PROJECT)

waves: trace.vcd

gtkwave -o trace.vcd

clean:

rm -rf *.vcd obj_dir $(DESTDIR)/$(PROJECT)

还是报错:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make run

make -C cache run

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

verilator --exe --language 1800-2009 --assert -Wno-DECLFILENAME -Wno-REDEFMACRO --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG' --output-split 20000

%Error: /home/dention/vortex/vortex/hw/rtl/libs/VX_find_first.sv:31: Unknown verilator lint message code: IMPORTSTAR, in /*verilator lint_off IMPORTSTAR*/

%Error: /home/dention/vortex/vortex/hw/rtl/libs/VX_find_first.sv:34: Unknown verilator lint message code: IMPORTSTAR, in /*verilator lint_on IMPORTSTAR*/

%Error: Exiting due to 2 error(s)

%Error: Command Failed /usr/bin/verilator_bin --exe --language 1800-2009 --assert -Wno-DECLFILENAME -Wno-REDEFMACRO --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG' --output-split 20000

../common.mk:48: recipe for target 'cache' failed

make[1]: *** [cache] Error 10

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

Makefile:10: recipe for target 'run' failed

make: *** [run] Error 2

这里报错原因大概率就是verilator版本不对了,嗐,查一下已安装的verilator版本:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# verilator -V

Verilator 3.916 2017-11-25 rev verilator_3_914-65-g0478dbd

Copyright 2003-2017 by Wilson Snyder. Verilator is free software; you can

redistribute it and/or modify the Verilator internals under the terms of

either the GNU Lesser General Public License Version 3 or the Perl Artistic

License Version 2.0.

See http://www.veripool.org/verilator for documentation

Summary of configuration:

Compiled in defaults if not in environment:

SYSTEMC =

SYSTEMC_ARCH =

SYSTEMC_INCLUDE =

SYSTEMC_LIBDIR =

VERILATOR_ROOT = /usr/share/verilator

Environment:

PERL =

SYSTEMC =

SYSTEMC_ARCH =

SYSTEMC_INCLUDE =

SYSTEMC_LIBDIR =

VERILATOR_ROOT =

VERILATOR_BIN =

这版本太过古老,vortex gpgpu最新版(截止到2024-10-01)都有差不多快7年的差距了。卸了老版本的verilator,改用新版本的verilator,参考:https://verilator.org/guide/latest/install.html

# Prerequisites:

sudo apt-get install git help2man perl python3 make autoconf g++ flex bison ccache

sudo apt-get install libgoogle-perftools-dev numactl perl-doc

sudo apt-get install libfl2 # Ubuntu only (ignore if gives error)

sudo apt-get install libfl-dev # Ubuntu only (ignore if gives error)

sudo apt-get install zlibc zlib1g zlib1g-dev # Ubuntu only (ignore if gives error)

git clone https://github.com/verilator/verilator # Only first time

# Every time you need to build:

unsetenv VERILATOR_ROOT # For csh; ignore error if on bash

unset VERILATOR_ROOT # For bash

cd verilator

git pull # Make sure git repository is up-to-date

git tag # See what versions exist

#git checkout master # Use development branch (e.g. recent bug fixes)

#git checkout stable # Use most recent stable release

#git checkout v{version} # Switch to specified release version

autoconf # Create ./configure script

./configure # Configure and create Makefile

make -j `nproc` # Build Verilator itself (if error, try just 'make')

sudo make install

安装完后再测试一下版本

root@ubuntu:/home/dention/verilator# verilator -V

Verilator 5.029 devel rev v5.028-158-g03012da11

Copyright 2003-2024 by Wilson Snyder. Verilator is free software; you can

redistribute it and/or modify the Verilator internals under the terms of

either the GNU Lesser General Public License Version 3 or the Perl Artistic

License Version 2.0.

See https://verilator.org for documentation

Summary of configuration:

Compiled in defaults if not in environment:

SYSTEMC =

SYSTEMC_ARCH =

SYSTEMC_INCLUDE =

SYSTEMC_LIBDIR =

VERILATOR_ROOT = /usr/local/share/verilator

SystemC system-wide = 0

Environment:

MAKE =

PERL =

PYTHON3 =

SYSTEMC =

SYSTEMC_ARCH =

SYSTEMC_INCLUDE =

SYSTEMC_LIBDIR =

VERILATOR_BIN =

VERILATOR_ROOT = /usr/local/share/verilator

Supported features (compiled-in or forced by environment):

COROUTINES = 1

SYSTEMC =

ok,接下来回到原版的common.mk文件,重新运行,还是出现报错:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make run

make -C cache run

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

verilator --build --exe --language 1800-2009 --assert -Wall -Wpedantic -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -j 1 -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG' -o ../cache

make[2]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache/obj_dir'

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -O2 -DNDEBUG -Os -c -o cachesim.o /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp

In file included from /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp:14:

/home/dention/vortex/vortex/hw/unittest/cache/cachesim.h:24:10: fatal error: VX_config.h: No such file or directory

24 | #include <VX_config.h>

| ^~~~~~~~~~~~~

compilation terminated.

VVX_cache_top.mk:69: recipe for target 'cachesim.o' failed

make[2]: *** [cachesim.o] Error 1

make[2]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache/obj_dir'

%Error: make -C obj_dir -f VVX_cache_top.mk -j 1 exited with 2

%Error: Command Failed ulimit -s unlimited 2>/dev/null; exec /usr/local/share/verilator/bin/verilator_bin --build --exe --language 1800-2009 --assert -Wall -Wpedantic -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -j 1 -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS -I/home/dention/vortex/vortex/hw/unittest/cache\ -I/home/dention/vortex/vortex/hw/unittest/common\ -I/home/dention/vortex/vortex/sim/common\ -I/home/dention/vortex/vortex/hw\ -std=c++17\ -Wall\ -Wextra\ -Wfatal-errors\ -Wno-array-bounds\ -fPIC\ -Wno-maybe-uninitialized\ \ -O2\ -DNDEBUG -o ../cache

../common.mk:50: recipe for target 'cache' failed

make[1]: *** [cache] Error 2

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

Makefile:10: recipe for target 'run' failed

make: *** [run] Error 2

错误信息显示编译过程中找不到文件VX_config.h,不过很简单用find命令确定一下是否存在:

find /home/<user_name>/vortex/vortex/ -name VX_config.h

我这边实际显示是:

/home/dention/vortex/vortex/build/hw/VX_config.h

那接下来很容易,就是.mk中指定该文件的地址,完整内容是:

DESTDIR ?= .

CONFIGS +=

PARAMS +=

# 添加 VX_config.h 文件的路径

CXXFLAGS += -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds

CXXFLAGS += -fPIC -Wno-maybe-uninitialized

CXXFLAGS += -I/home/dention/vortex/vortex/build/hw # 添加包含路径

CXXFLAGS += $(CONFIGS)

LDFLAGS +=

RTL_PKGS +=

RTL_INCLUDE +=

DBG_FLAGS += -DDEBUG_LEVEL=$(DEBUG) -DVCD_OUTPUT $(DBG_TRACE_FLAGS)

VL_FLAGS = --exe

VL_FLAGS += --language 1800-2009 --assert -Wall -Wpedantic

VL_FLAGS += -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED

VL_FLAGS += --x-initial unique --x-assign unique

VL_FLAGS += -DSIMULATION -DSV_DPI

VL_FLAGS += $(CONFIGS)

VL_FLAGS += $(PARAMS)

VL_FLAGS += $(RTL_INCLUDE)

VL_FLAGS += $(RTL_PKGS)

VL_FLAGS += --cc $(TOP) --top-module $(TOP)

# Enable Verilator multithreaded simulation

THREADS ?= $(shell python -c 'import multiprocessing as mp; print(mp.cpu_count())')

VL_FLAGS += -j $(THREADS)

# Debugging

ifdef DEBUG

VL_FLAGS += --trace --trace-structs $(DBG_FLAGS)

CXXFLAGS += -g -O0 $(DBG_FLAGS)

else

VL_FLAGS += -DNDEBUG

CXXFLAGS += -O2 -DNDEBUG

endif

# Enable perf counters

ifdef PERF

VL_FLAGS += -DPERF_ENABLE

CXXFLAGS += -DPERF_ENABLE

endif

all: $(DESTDIR)/$(PROJECT)

$(DESTDIR)/$(PROJECT): $(SRCS)

verilator --build $(VL_FLAGS) $^ -CFLAGS '$(CXXFLAGS)' -o ../$@

run: $(DESTDIR)/$(PROJECT)

$(DESTDIR)/$(PROJECT)

waves: trace.vcd

gtkwave -o trace.vcd

clean:

rm -rf *.vcd obj_dir $(DESTDIR)/$(PROJECT)

接着

make clean

make run

当然了,不出意外还是报错,不过幸运的是不是配置问题:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest# make run

make -C cache run

make[1]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache'

verilator --build --exe --language 1800-2009 --assert -Wall -Wpedantic -Wno-DECLFILENAME -Wno-REDEFMACRO -Wno-GENUNNAMED --x-initial unique --x-assign unique -DSIMULATION -DSV_DPI -I/home/dention/vortex/vortex/hw/rtl -I/home/dention/vortex/vortex/hw/dpi -I/home/dention/vortex/vortex/hw/rtl/libs -I/home/dention/vortex/vortex/hw/rtl/interfaces -I/home/dention/vortex/vortex/hw/rtl/mem -I/home/dention/vortex/vortex/hw/rtl/cache /home/dention/vortex/vortex/hw/rtl/VX_gpu_pkg.sv --cc VX_cache_top --top-module VX_cache_top -j 1 -DNDEBUG /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp -CFLAGS '-I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG' -o ../cache

make[2]: Entering directory '/home/dention/vortex/vortex/hw/unittest/cache/obj_dir'

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -Os -c -o util_dpi.o /home/dention/vortex/vortex/hw/dpi/util_dpi.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -Os -c -o cachesim.o /home/dention/vortex/vortex/hw/unittest/cache/cachesim.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -Os -c -o testbench.o /home/dention/vortex/vortex/hw/unittest/cache/testbench.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -c -o verilated.o /usr/local/share/verilator/include/verilated.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -c -o verilated_dpi.o /usr/local/share/verilator/include/verilated_dpi.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -c -o verilated_threads.o /usr/local/share/verilator/include/verilated_threads.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -x c++-header VVX_cache_top__pch.h -o VVX_cache_top__pch.h.fast.gch

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top.o VVX_cache_top.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024root__DepSet_h9edbfabb__0.o VVX_cache_top___024root__DepSet_h9edbfabb__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024root__DepSet_h9edbfabb__1.o VVX_cache_top___024root__DepSet_h9edbfabb__1.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024root__DepSet_h763c9220__0.o VVX_cache_top___024root__DepSet_h763c9220__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024root__DepSet_h763c9220__1.o VVX_cache_top___024root__DepSet_h763c9220__1.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024root__DepSet_h763c9220__2.o VVX_cache_top___024root__DepSet_h763c9220__2.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top___024unit__DepSet_ha36da8de__0.o VVX_cache_top___024unit__DepSet_ha36da8de__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0.o VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0.o VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_hc66bcb2d__0.o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_hc66bcb2d__0.cpp

ccache g++ -Os -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.fast -c -o VVX_cache_top__Dpi.o VVX_cache_top__Dpi.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -x c++-header VVX_cache_top__pch.h -o VVX_cache_top__pch.h.slow.gch

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top__ConstPool_0.o VVX_cache_top__ConstPool_0.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024root__Slow.o VVX_cache_top___024root__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024root__DepSet_h9edbfabb__0__Slow.o VVX_cache_top___024root__DepSet_h9edbfabb__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024root__DepSet_h763c9220__0__Slow.o VVX_cache_top___024root__DepSet_h763c9220__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024root__DepSet_h763c9220__1__Slow.o VVX_cache_top___024root__DepSet_h763c9220__1__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024unit__Slow.o VVX_cache_top___024unit__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top___024unit__DepSet_h89ae607b__0__Slow.o VVX_cache_top___024unit__DepSet_h89ae607b__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_mem_bus_if__D4_T10__Slow.o VVX_cache_top_VX_mem_bus_if__D4_T10__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0__Slow.o VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_mem_bus_if__D40_T6__Slow.o VVX_cache_top_VX_mem_bus_if__D40_T6__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0__Slow.o VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__Slow.o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_h9ab0d52c__0__Slow.o VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_h9ab0d52c__0__Slow.cpp

ccache g++ -I. -MMD -I/usr/local/share/verilator/include -I/usr/local/share/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TIMING=0 -DVM_TRACE=0 -DVM_TRACE_FST=0 -DVM_TRACE_VCD=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-shadow -Wno-sign-compare -Wno-tautological-compare -Wno-uninitialized -Wno-unused-but-set-parameter -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -I/home/dention/vortex/vortex/hw/unittest/cache -I/home/dention/vortex/vortex/hw/unittest/common -I/home/dention/vortex/vortex/sim/common -I/home/dention/vortex/vortex/hw -std=c++17 -Wall -Wextra -Wfatal-errors -Wno-array-bounds -fPIC -Wno-maybe-uninitialized -I/home/dention/vortex/vortex/build/hw -O2 -DNDEBUG -include VVX_cache_top__pch.h.slow -c -o VVX_cache_top__Syms.o VVX_cache_top__Syms.cpp

echo "" > VVX_cache_top__ALL.verilator_deplist.tmp

g++ util_dpi.o cachesim.o testbench.o verilated.o verilated_dpi.o verilated_threads.o VVX_cache_top__ALL.a -pthread -lpthread -latomic -o ../cache

rm VVX_cache_top__ALL.verilator_deplist.tmp

make[2]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache/obj_dir'

- V e r i l a t i o n R e p o r t: Verilator 5.029 devel rev v5.028-158-g03012da11

- Verilator: Built from 0.525 MB sources in 44 modules, into 8.925 MB in 25 C++ files needing 0.151 MB

- Verilator: Walltime 56.544 s (elab=0.371, cvt=2.312, bld=53.396); cpu 3.058 s on 1 threads; alloced 330.363 MB

./cache

[1] %Error: VX_cache_mshr.sv:224: Assertion failed in TOP.VX_cache_top.cache.banks[0].bank.cache_mshr: 1: *** -bank0-mshr invalid release: addr=0x7d3b9c00, id=7 (#0)

%Error: /home/dention/vortex/vortex/hw/rtl/cache/VX_cache_mshr.sv:224: Verilog $stop

Aborting...

../common.mk:54: recipe for target 'run' failed

make[1]: *** [run] Aborted (core dumped)

make[1]: Leaving directory '/home/dention/vortex/vortex/hw/unittest/cache'

Makefile:10: recipe for target 'run' failed

make: *** [run] Error 2

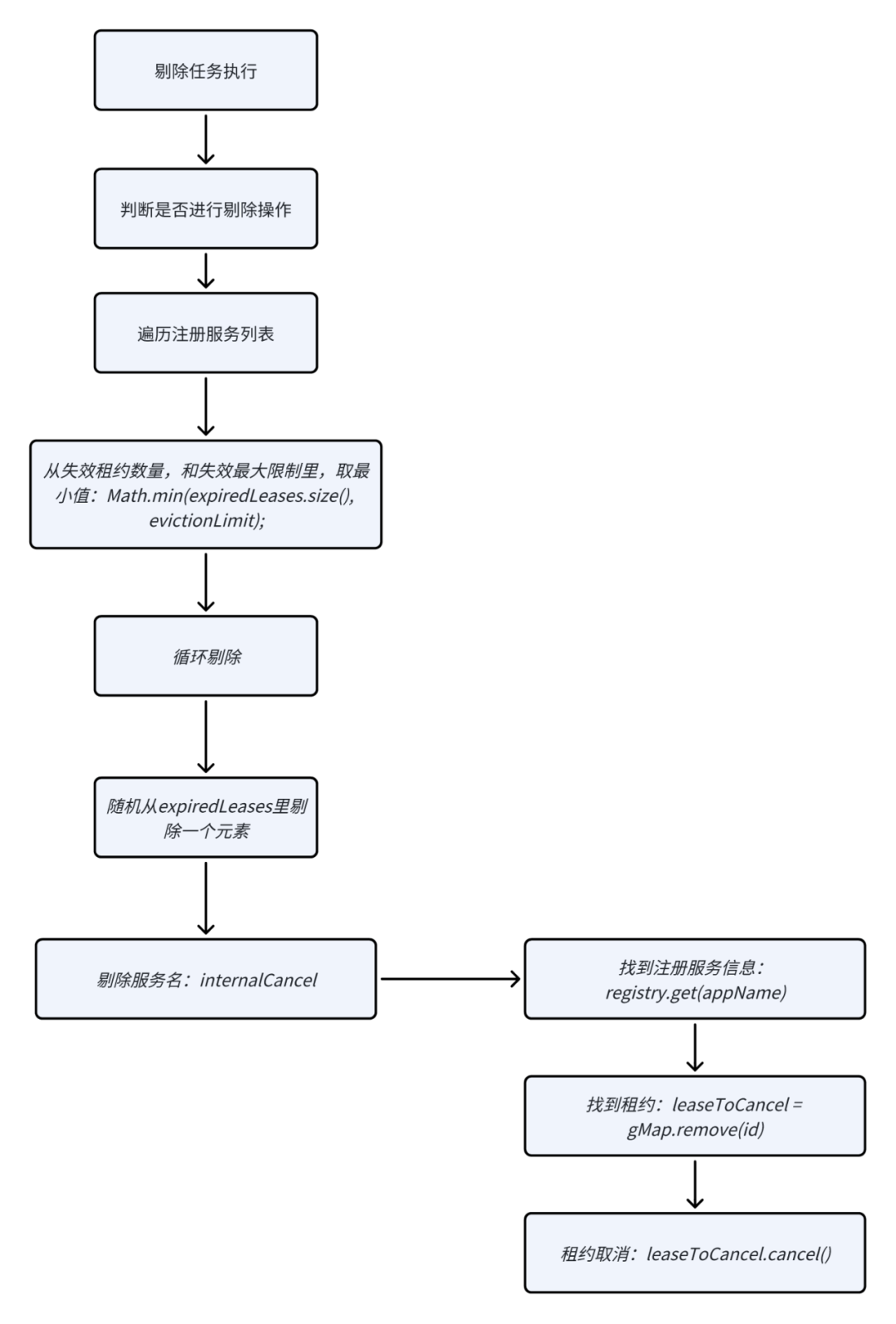

在VX_cache_mshr.sv的第224行,有一个断言检查失败,导致模拟程序终止。看下该文件:

// Copyright © 2019-2023

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

`include "VX_cache_define.vh"

// This is an implementation of a MSHR for pipelined multi-banked cache.

// We allocate a free slot from the MSHR before processing a core request

// and release the slot when we get a cache hit. This ensure that we do not

// enter the cache bank pipeline when the MSHR is full.

// During a memory fill response, we initiate the replay sequence

// and dequeue all pending entries for the given cache line.

//

// Pending core requests stored in the MSHR are sorted by the order of

// arrival and are dequeued in the same order.

// Each entry has a next pointer to the next entry pending for the same cache line.

//

// During the fill operation, the MSHR will release the MSHR entry at fill_id

// which represents the first request in the pending list that initiated the memory fill.

//

// The dequeue operation directly follows the fill operation and will release

// all the subsequent entries linked to fill_id (pending the same cache line).

//

// During the allocation operation, the MSHR will allocate the next free slot

// for the incoming core request. We return the allocated slot id as well as

// the slot id of the previous entry for the same cache line. This is used to

// link the new entry to the pending list during finalization.

//

// The lookup operation is used to find all pending entries for a given cache line.

// This is used to by the cache bank to determine if a cache miss is already pending

// and therefore avoid issuing a memory fill request.

//

// The finalize operation is used to release the allocated MSHR entry if we had a hit.

// If we had a miss and finalize_pending is true, we link the allocated entry to

// its corresponding pending list (via finalize_prev).

//

// Warning: This MSHR implementation is strongly coupled with the bank pipeline

// and as such changes to either module requires careful evaluation.

//

// This architecture implements three pipeline stages:

// - Arbitration: cache bank arbitration before entering pipeline.

// fill and dequeue operations are executed at this stage.

// - stage 0: cache bank tag access stage.

// allocate and lookup operations are executed at this stage.

// - stage 1: cache bank tdatag access stage.

// finalize operation is executed at this stage.

//

module VX_cache_mshr #(

parameter `STRING INSTANCE_ID= "",

parameter BANK_ID = 0,

// Size of line inside a bank in bytes

parameter LINE_SIZE = 16,

// Number of banks

parameter NUM_BANKS = 1,

// Miss Reserv Queue Knob

parameter MSHR_SIZE = 4,

// Request debug identifier

parameter UUID_WIDTH = 0,

// MSHR parameters

parameter DATA_WIDTH = 1,

parameter MSHR_ADDR_WIDTH = `LOG2UP(MSHR_SIZE)

) (

input wire clk,

input wire reset,

`IGNORE_UNUSED_BEGIN

input wire[`UP(UUID_WIDTH)-1:0] deq_req_uuid,

input wire[`UP(UUID_WIDTH)-1:0] lkp_req_uuid,

input wire[`UP(UUID_WIDTH)-1:0] fin_req_uuid,

`IGNORE_UNUSED_END

// memory fill

input wire fill_valid,

input wire [MSHR_ADDR_WIDTH-1:0] fill_id,

output wire [`CS_LINE_ADDR_WIDTH-1:0] fill_addr,

// dequeue

output wire dequeue_valid,

output wire [`CS_LINE_ADDR_WIDTH-1:0] dequeue_addr,

output wire dequeue_rw,

output wire [DATA_WIDTH-1:0] dequeue_data,

output wire [MSHR_ADDR_WIDTH-1:0] dequeue_id,

input wire dequeue_ready,

// allocate

input wire allocate_valid,

input wire [`CS_LINE_ADDR_WIDTH-1:0] allocate_addr,

input wire allocate_rw,

input wire [DATA_WIDTH-1:0] allocate_data,

output wire [MSHR_ADDR_WIDTH-1:0] allocate_id,

output wire [MSHR_ADDR_WIDTH-1:0] allocate_prev,

output wire allocate_ready,

// lookup

input wire lookup_valid,

input wire [`CS_LINE_ADDR_WIDTH-1:0] lookup_addr,

output wire [MSHR_SIZE-1:0] lookup_pending,

output wire [MSHR_SIZE-1:0] lookup_rw,

// finalize

input wire finalize_valid,

input wire finalize_release,

input wire finalize_pending,

input wire [MSHR_ADDR_WIDTH-1:0] finalize_id,

input wire [MSHR_ADDR_WIDTH-1:0] finalize_prev

);

`UNUSED_PARAM (BANK_ID)

reg [`CS_LINE_ADDR_WIDTH-1:0] addr_table [MSHR_SIZE-1:0];

reg [MSHR_ADDR_WIDTH-1:0] next_index [MSHR_SIZE-1:0];

reg [MSHR_SIZE-1:0] valid_table, valid_table_n;

reg [MSHR_SIZE-1:0] next_table, next_table_x, next_table_n;

reg [MSHR_SIZE-1:0] write_table;

reg allocate_rdy, allocate_rdy_n;

reg [MSHR_ADDR_WIDTH-1:0] allocate_id_r, allocate_id_n;

reg dequeue_val, dequeue_val_n;

reg [MSHR_ADDR_WIDTH-1:0] dequeue_id_r, dequeue_id_n;

wire [MSHR_ADDR_WIDTH-1:0] prev_idx;

wire allocate_fire = allocate_valid && allocate_ready;

wire dequeue_fire = dequeue_valid && dequeue_ready;

wire [MSHR_SIZE-1:0] addr_matches;

for (genvar i = 0; i < MSHR_SIZE; ++i) begin

assign addr_matches[i] = valid_table[i] && (addr_table[i] == lookup_addr);

end

VX_lzc #(

.N (MSHR_SIZE),

.REVERSE (1)

) allocate_sel (

.data_in (~valid_table_n),

.data_out (allocate_id_n),

.valid_out (allocate_rdy_n)

);

VX_onehot_encoder #(

.N (MSHR_SIZE)

) prev_sel (

.data_in (addr_matches & ~next_table_x),

.data_out (prev_idx),

`UNUSED_PIN (valid_out)

);

always @(*) begin

valid_table_n = valid_table;

next_table_x = next_table;

dequeue_val_n = dequeue_val;

dequeue_id_n = dequeue_id;

if (fill_valid) begin

dequeue_val_n = 1;

dequeue_id_n = fill_id;

end

if (dequeue_fire) begin

valid_table_n[dequeue_id] = 0;

if (next_table[dequeue_id]) begin

dequeue_id_n = next_index[dequeue_id];

end else begin

dequeue_val_n = 0;

end

end

if (finalize_valid) begin

if (finalize_release) begin

valid_table_n[finalize_id] = 0;

end

if (finalize_pending) begin

next_table_x[finalize_prev] = 1;

end

end

next_table_n = next_table_x;

if (allocate_fire) begin

valid_table_n[allocate_id] = 1;

next_table_n[allocate_id] = 0;

end

end

always @(posedge clk) begin

if (reset) begin

valid_table <= '0;

allocate_rdy <= 0;

dequeue_val <= 0;

end else begin

valid_table <= valid_table_n;

allocate_rdy <= allocate_rdy_n;

dequeue_val <= dequeue_val_n;

end

if (allocate_fire) begin

addr_table[allocate_id] <= allocate_addr;

write_table[allocate_id] <= allocate_rw;

end

if (finalize_valid && finalize_pending) begin

next_index[finalize_prev] <= finalize_id;

end

dequeue_id_r <= dequeue_id_n;

allocate_id_r <= allocate_id_n;

next_table <= next_table_n;

end

`RUNTIME_ASSERT((~allocate_fire || ~valid_table[allocate_id_r]), ("%t: *** %s inuse allocation: addr=0x%0h, id=%0d (#%0d)", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(allocate_addr, BANK_ID), allocate_id_r, lkp_req_uuid))

`RUNTIME_ASSERT((~finalize_valid || valid_table[finalize_id]), ("%t: *** %s invalid release: addr=0x%0h, id=%0d (#%0d)", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(addr_table[finalize_id], BANK_ID), finalize_id, fin_req_uuid))

`RUNTIME_ASSERT((~fill_valid || valid_table[fill_id]), ("%t: *** %s invalid fill: addr=0x%0h, id=%0d", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(addr_table[fill_id], BANK_ID), fill_id))

VX_dp_ram #(

.DATAW (DATA_WIDTH),

.SIZE (MSHR_SIZE),

.LUTRAM (1)

) entries (

.clk (clk),

.reset (reset),

.read (1'b1),

.write (allocate_valid),

.wren (1'b1),

.waddr (allocate_id_r),

.wdata (allocate_data),

.raddr (dequeue_id_r),

.rdata (dequeue_data)

);

assign fill_addr = addr_table[fill_id];

assign allocate_ready = allocate_rdy;

assign allocate_id = allocate_id_r;

assign allocate_prev = prev_idx;

assign dequeue_valid = dequeue_val;

assign dequeue_addr = addr_table[dequeue_id_r];

assign dequeue_rw = write_table[dequeue_id_r];

assign dequeue_id = dequeue_id_r;

// return pending entries for the given cache line

assign lookup_pending = addr_matches;

assign lookup_rw = write_table;

`UNUSED_VAR (lookup_valid)

`ifdef DBG_TRACE_CACHE

reg show_table;

always @(posedge clk) begin

if (reset) begin

show_table <= 0;

end else begin

show_table <= allocate_fire || lookup_valid || finalize_valid || fill_valid || dequeue_fire;

end

if (allocate_fire)

`TRACE(3, ("%d: %s allocate: addr=0x%0h, prev=%0d, id=%0d (#%0d)\n", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(allocate_addr, BANK_ID), allocate_prev, allocate_id, lkp_req_uuid));

if (lookup_valid)

`TRACE(3, ("%d: %s lookup: addr=0x%0h, matches=%b (#%0d)\n", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(lookup_addr, BANK_ID), lookup_pending, lkp_req_uuid));

if (finalize_valid)

`TRACE(3, ("%d: %s finalize release=%b, pending=%b, prev=%0d, id=%0d (#%0d)\n", $time, INSTANCE_ID,

finalize_release, finalize_pending, finalize_prev, finalize_id, fin_req_uuid));

if (fill_valid)

`TRACE(3, ("%d: %s fill: addr=0x%0h, addr=0x%0h, id=%0d\n", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(addr_table[fill_id], BANK_ID), `CS_LINE_TO_FULL_ADDR(fill_addr, BANK_ID), fill_id));

if (dequeue_fire)

`TRACE(3, ("%d: %s dequeue: addr=0x%0h, id=%0d (#%0d)\n", $time, INSTANCE_ID,

`CS_LINE_TO_FULL_ADDR(dequeue_addr, BANK_ID), dequeue_id_r, deq_req_uuid));

if (show_table) begin

`TRACE(3, ("%d: %s table", $time, INSTANCE_ID));

for (integer i = 0; i < MSHR_SIZE; ++i) begin

if (valid_table[i]) begin

`TRACE(3, (" %0d=0x%0h", i, `CS_LINE_TO_FULL_ADDR(addr_table[i], BANK_ID)));

if (write_table[i])

`TRACE(3, ("(w)"));

else

`TRACE(3, ("(r)"));

if (next_table[i])

`TRACE(3, ("->%0d", next_index[i]));

end

end

`TRACE(3, ("\n"));

end

end

`endif

endmodule

大概率是这里的参数配置出了问题,后面琢磨一下。

可以看下输出文件的结构:

root@ubuntu:/home/dention/vortex/vortex/hw/unittest/cache# tree

.

├── cache

├── cachesim.cpp

├── cachesim.h

├── Makefile

├── obj_dir

│ ├── cachesim.d

│ ├── cachesim.o

│ ├── testbench.d

│ ├── testbench.o

│ ├── util_dpi.d

│ ├── util_dpi.o

│ ├── verilated.d

│ ├── verilated_dpi.d

│ ├── verilated_dpi.o

│ ├── verilated.o

│ ├── verilated_threads.d

│ ├── verilated_threads.o

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0.cpp

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0.d

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0.o

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0__Slow.cpp

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0__Slow.d

│ ├── VVX_cache_top___024root__DepSet_h763c9220__0__Slow.o

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1.cpp

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1.d

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1.o

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1__Slow.cpp

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1__Slow.d

│ ├── VVX_cache_top___024root__DepSet_h763c9220__1__Slow.o

│ ├── VVX_cache_top___024root__DepSet_h763c9220__2.cpp

│ ├── VVX_cache_top___024root__DepSet_h763c9220__2.d

│ ├── VVX_cache_top___024root__DepSet_h763c9220__2.o

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0.cpp

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0.d

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0.o

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0__Slow.cpp

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0__Slow.d

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__0__Slow.o

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__1.cpp

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__1.d

│ ├── VVX_cache_top___024root__DepSet_h9edbfabb__1.o

│ ├── VVX_cache_top___024root.h

│ ├── VVX_cache_top___024root__Slow.cpp

│ ├── VVX_cache_top___024root__Slow.d

│ ├── VVX_cache_top___024root__Slow.o

│ ├── VVX_cache_top___024unit__DepSet_h89ae607b__0__Slow.cpp

│ ├── VVX_cache_top___024unit__DepSet_h89ae607b__0__Slow.d

│ ├── VVX_cache_top___024unit__DepSet_h89ae607b__0__Slow.o

│ ├── VVX_cache_top___024unit__DepSet_ha36da8de__0.cpp

│ ├── VVX_cache_top___024unit__DepSet_ha36da8de__0.d

│ ├── VVX_cache_top___024unit__DepSet_ha36da8de__0.o

│ ├── VVX_cache_top___024unit.h

│ ├── VVX_cache_top___024unit__Slow.cpp

│ ├── VVX_cache_top___024unit__Slow.d

│ ├── VVX_cache_top___024unit__Slow.o

│ ├── VVX_cache_top__ALL.a

│ ├── VVX_cache_top_classes.mk

│ ├── VVX_cache_top__ConstPool_0.cpp

│ ├── VVX_cache_top__ConstPool_0.d

│ ├── VVX_cache_top__ConstPool_0.o

│ ├── VVX_cache_top.cpp

│ ├── VVX_cache_top.d

│ ├── VVX_cache_top__Dpi.cpp

│ ├── VVX_cache_top__Dpi.d

│ ├── VVX_cache_top__Dpi.h

│ ├── VVX_cache_top__Dpi.o

│ ├── VVX_cache_top.h

│ ├── VVX_cache_top.mk

│ ├── VVX_cache_top.o

│ ├── VVX_cache_top__pch.h

│ ├── VVX_cache_top__pch.h.fast.d

│ ├── VVX_cache_top__pch.h.fast.gch

│ ├── VVX_cache_top__pch.h.slow.d

│ ├── VVX_cache_top__pch.h.slow.gch

│ ├── VVX_cache_top__Syms.cpp

│ ├── VVX_cache_top__Syms.d

│ ├── VVX_cache_top__Syms.h

│ ├── VVX_cache_top__Syms.o

│ ├── VVX_cache_top__ver.d

│ ├── VVX_cache_top__verFiles.dat

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0.d

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0.o

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0__Slow.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0__Slow.d

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__DepSet_hd3f6db6d__0__Slow.o

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6.h

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__Slow.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__Slow.d

│ ├── VVX_cache_top_VX_mem_bus_if__D40_T6__Slow.o

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0.d

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0.o

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0__Slow.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0__Slow.d

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__DepSet_hb15d137d__0__Slow.o

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10.h

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__Slow.cpp

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__Slow.d

│ ├── VVX_cache_top_VX_mem_bus_if__D4_T10__Slow.o

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_h9ab0d52c__0__Slow.cpp

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_h9ab0d52c__0__Slow.d

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_h9ab0d52c__0__Slow.o

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_hc66bcb2d__0.cpp

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_hc66bcb2d__0.d

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__DepSet_hc66bcb2d__0.o

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1.h

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__Slow.cpp

│ ├── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__Slow.d

│ └── VVX_cache_top_VX_sp_ram__D15_S10_N1_R1__Slow.o

├── ram.h

└── testbench.cpp

1 directory, 111 files

root@ubuntu:/home/dention/vortex/vortex/hw/unittest/cache# ls

cache cachesim.cpp cachesim.h Makefile obj_dir ram.h testbench.cpp

篇幅已经比较长了,博客继续输出已经开始卡住了。放在下一篇琢磨。

总结

本篇比较丝滑地跑通官网demo,但意义不大。目前还是想看清楚各个子模块的功能及其波形。