目录

感悟

一、存储系统的层次结构

存储器系统

二、内存管理单元

三、RAM和ROM的种类与选型

1、RAM

RAM分类

2、ROM

ROM分类

四、高速缓存Cache

五、其他存储设备

flechazo![]() https://www.zhihu.com/people/jiu_sheng

https://www.zhihu.com/people/jiu_sheng

小柴冲刺软考中级嵌入式系统设计师系列总目录![]() https://zhuanlan.zhihu.com/p/705451211

https://zhuanlan.zhihu.com/p/705451211

感悟

兄弟们,最近道心有些不稳。

五官和三观,务虚和务实。

先无论自己水平如何,先能说服别人拥有门槛才是第一步!

而这一步需要的是五官,职场中对应的是务虚了!

临时的口才与知识点的背诵可能大于踏踏实实地学习了。

嗯,是时候做出一些改变了。

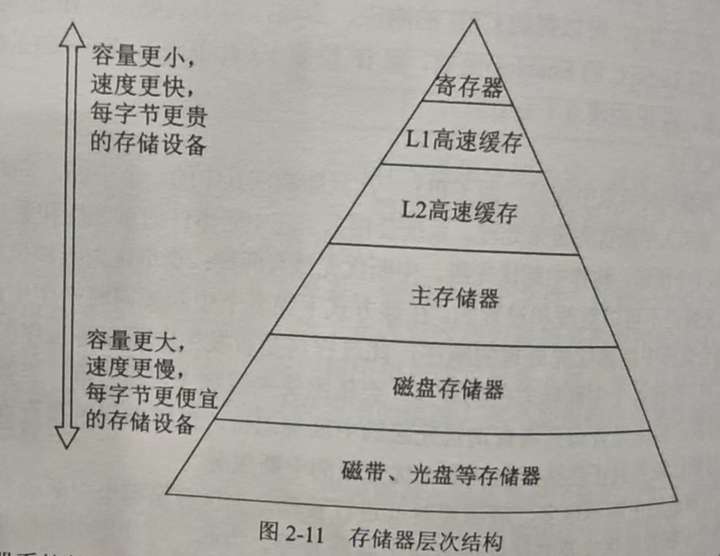

一、存储系统的层次结构

冯诺依曼计算机机构中,一个非常重要的部件就是存储器。

在理想情形下,存储器应该具备执行快、容量足和价格便宜等特点。但目前技术无法同时满足这三个目标。

添加图片注释,不超过 140 字(可选)

存储器系统

-

寄存器:顶层是CPU的寄存器,其速度与CPU速度相当。

-

L1高速缓存:Cache,和CPU速度接近。

-

L2高速缓存:Cache

-

主存储器:也称为内部存储器或者RAM(Random Access Memory)

-

磁盘

-

磁带、光盘

二、内存管理单元

存储管理单元(Memory Management Unit,MMU),提供内存保护的硬件机制。操作系统通常利用MMU来实现系统内核与应用程序的隔离,以及应用程序与应用程序之间的隔离。一是防止地址越界,每个应用程序都有自己独立的地址空间。二是防止操作越权。

三、RAM和ROM的种类与选型

内部存储器-外部存储器

易失性存储器-非易失性存储器

1、RAM

易失性存储器的代表是随机存取存储器(Random Access Memory,RAM)RAM是与CPU直接交换数据的内部存储器,也叫主存或内存

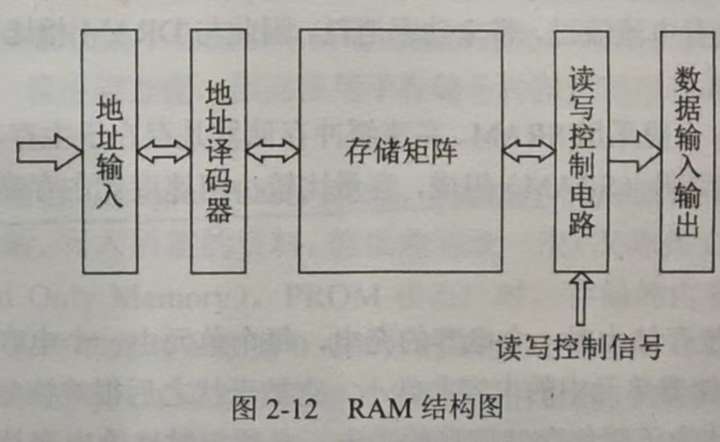

添加图片注释,不超过 140 字(可选)

RAM电路由地址译码器、存储矩阵、读写控制电路三部分组成。

-

随机读写

-

读写速度很快

-

断电时丢失数据

RAM分类

-

SRAM

-

静态存储单元是在静态触发器的基础上附加门控管构成的。因此它是靠触发器的自保功能存储数据的。SRAM将每个位存储在一个双稳态存储单元,每个单元用一个六晶体管电路实现。

-

在工作时,只要保持在加电的状态,就会有电流流过,带来功率消耗。因此比DRAM功耗大,集成度做不到很高。

-

高速缓存Cache一般采用SRAM。

-

-

DRAM

-

DRAM将每个位存储为对一个电容的充电,每个单元由一个电容和一个访问晶体管组成。电容会漏电,因此需要定时刷新充电,所以DRAM内部要有刷新控制电路,其操作比SRAM复杂,但是存储单元结构非常简单,元器件少且功耗低,一次可以制造得很密集,成为大容量RAM的主流产品。

-

DRAM的存储矩阵由动态MOS存储单元组成

-

常说的内存条就是DRAM构成

-

-

DDR SDRAM

-

双倍速率同步动态随机存储器(Double Data Rate SDRAM)内存主频和CPU主频一样

-

2、ROM

只读存储器(Read-Only Memory,ROM),特点是数据掉电不丢失。

ROM分类

-

PROM

-

可编程只读存储器Programmable ROM,内部有行列式熔丝,需要利用电流将其烧断,只能写入一次

-

-

EPROM

-

可抹除可编程只读存储器Erasable Programmable Read Only Memory,是目前使用最广泛的ROM。

-

利用高电压电流将资料编程写入,抹除时将线路曝光于紫外线下即可清空资料

-

-

EEPROM

-

电子可抹除可编程只读存储器Electrically Erasable Programmable Read Only Memory,EEPROM

-

四、高速缓存Cache

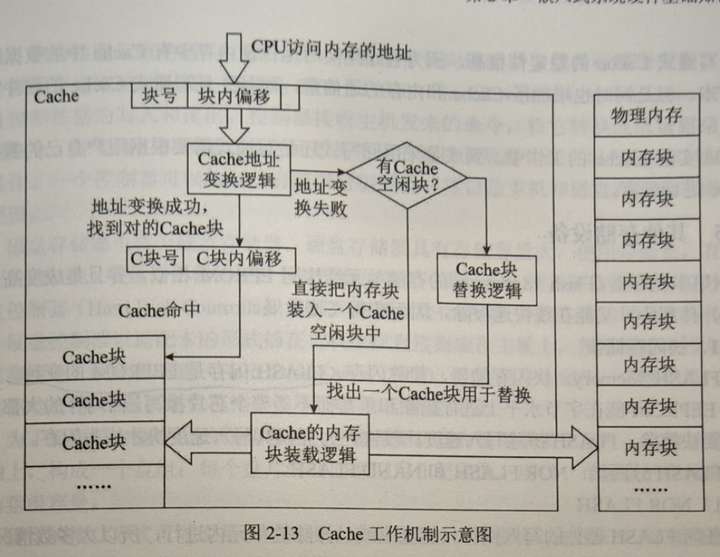

Cache逻辑工作示意图

添加图片注释,不超过 140 字(可选)

根据Cache的工作机制,可以分类为:

-

回写式Cache

-

当CPU执行写数据操作时,回写式Cache只把该数据写入其数据地址对应的Cache中,不直接写入内存。仅当该Cache块需要替换时,才把Cache块写入内存。

-

-

写通式Cache

-

写操作时直接写入内存

-

五、其他存储设备

-

快闪存储器(闪存)

-

NOR FLASH

-

NAND FLASH

-

磁盘、光盘等存储介质

-

磁盘

-

光盘

-

CF

-

SD