一、基础知识

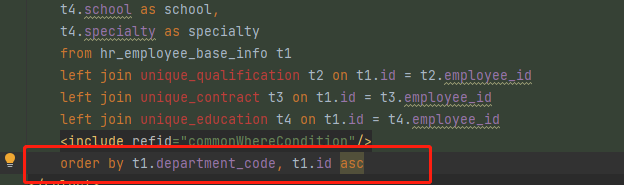

01 dram基本存储单元

当需要将一位数据存储到DRAM中时,晶体管会充电或放电电容。充电的电容表示逻辑高(1),放电的电容表示逻辑低(0)。由于电容会随着时间泄漏电荷,因此需要定期刷新电容中的数据,以确保数据不会丢失。

- wordline(字线):决定了晶体管的导通或截止,控制对存储电容的访问

- bitline(位线):外界可以通过bitline对存储电容进行读取或者写入操作

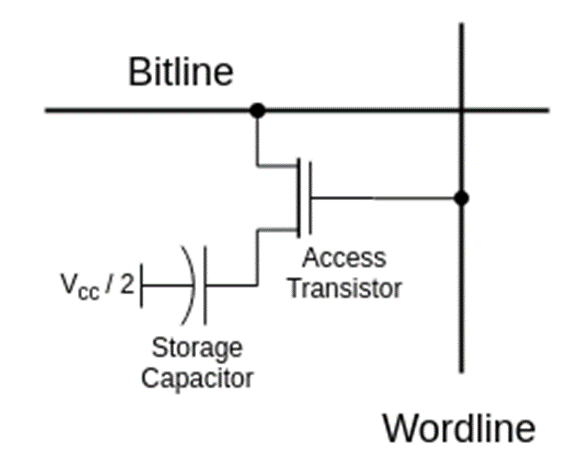

dram内部结构:

02 DDR概念

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步、动态、随机是其性能特点的外在说明:

- 同步(Synchronous )是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准

- 动态(Dynamic )是指存储阵列 需要不断的刷新来保证数据不丢失

- 随机(Random )是指数据不是线性依次存储,而是自由指定地址进行数据读写

SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于SDRAM内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作;同时在读写过程中 需要考虑行列管理、各种操作延时等,由此导致了其控制逻辑复杂的特点。

SDRAM 内部可以理解为一个存储阵列,表格中的每一个单元格可以类比为存储阵列的单个存储单元。若想要实现存储阵列中的某一存储单元的数据读写操作,可以通过行地址(Row Address)和列地址 (Column Address)(先行后列)精确定位到这一存储单元,进而进行数据的读写操作,这就是所谓的随机地址存取.

- SDRAM:同步动态随机通道存储器

- SDR:1倍prefetch,IO速率和内部工作速率一致

- DDR:2倍prefetch,改进了IO采样为双沿采样,io时钟频率相比于sdr不变

- DDR2: 4倍prefetch,io时钟频率翻倍,结合双沿,实现4倍预取

- DDR3:8倍prefetch,io时钟频率相比于sdr提升4倍,结合双沿,实现8倍预取

| Specifications | LPDDR1 | LPDDR2 | LPDDR3 | LPDDR4 | LPDDR5 | LPDDR5X |

|---|---|---|---|---|---|---|

| I/O bus clock frequency (MHz) | 200, 266.7 (For LPDDR-1E) | 400, 533.3 (For LPDDR-2E) | 800, 1067 (For LPDDR-3E) | 1600, 2133 (For LPDDR-4X) | 3200 | 3750/4266.5 |

| Prefetch size | 2n | 4/2n | 8n | 16n | 16n | 16n |

| Data transfer rate or speed in Mbps | 400, 533.3 (for LPDDR-1E) | 800, 1067 (for LPDDR-2E) | 1600, 2133 (for LPDDR-3E) | 3200, 4267 (for LPDDR-4X) | 6400 | 8533 |

| Supply voltage | 1.8 V | 1.2, 1.8 V | 1.2, 1.8 | 1.1, 1.8 V | I/O voltage: 0.6V | 1.05, 0.9 |

| Die Density | 128Mb – 2Gb | 256Mb – 2Gb | 1Gb – 8Gb | 4Gb – 24Gb | 4Gb – 24Gb | 8Gb – 24Gb |

| Memory Clock | 200, 1E-266.7 | 200, 2E-266.7 | 200, 3E-266.7 | 200, 4X-266.7 | 400 | 400 |

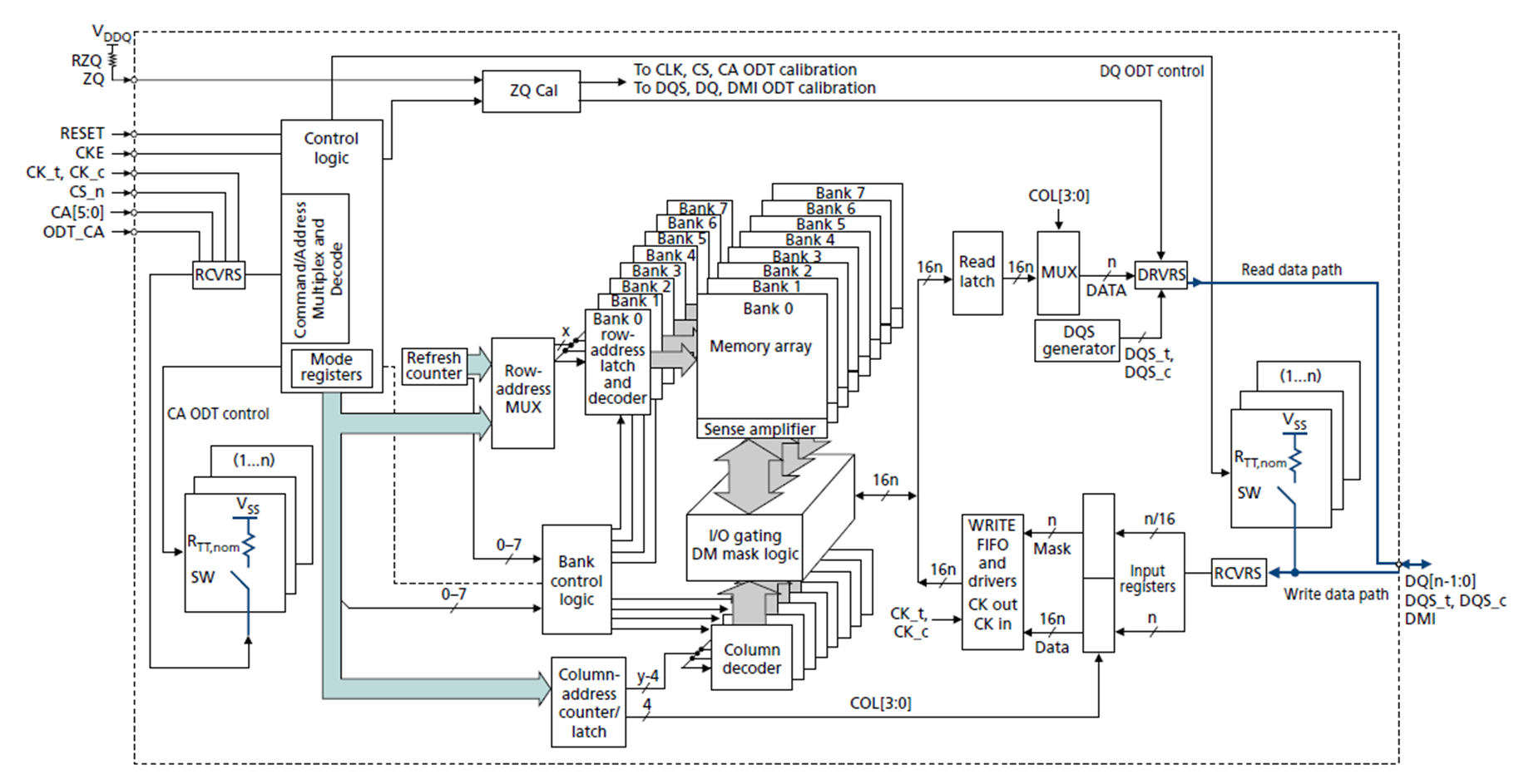

LPDDR4: 16-n prefetch

IO bus data 传输速率 / 16 = DRAM core clock

IO bus data 传输速率 / 2 = IO bus clock

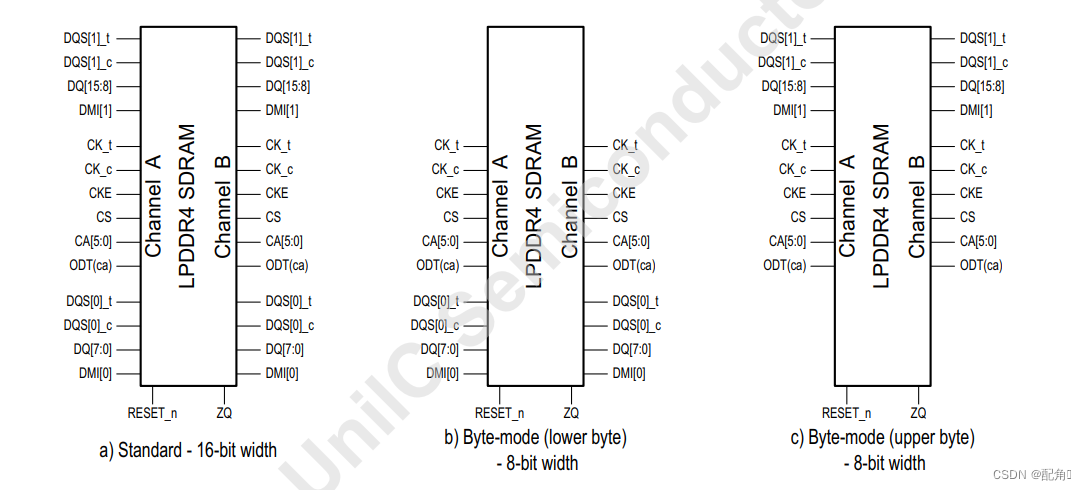

二、颗粒类型

六种颗粒类型:

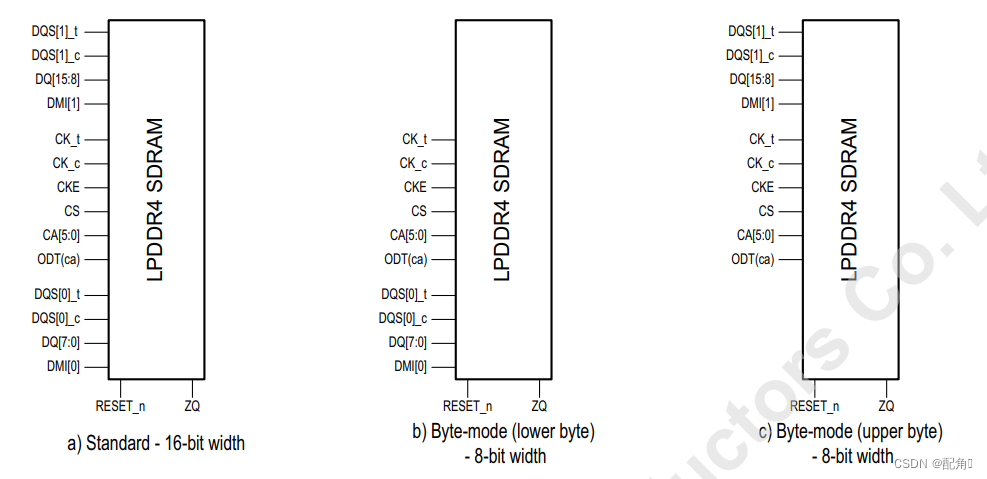

双通道:

单通道:

两个单byte模式均可以拼接成一个标准模式。

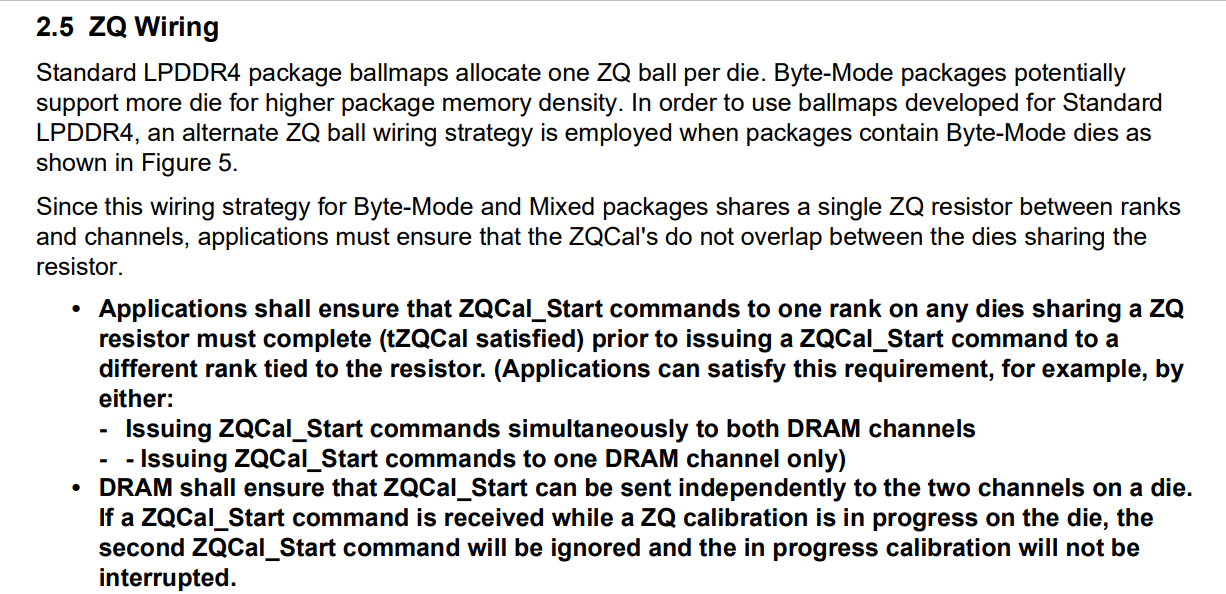

三、ZQ wiring

阻抗校准:

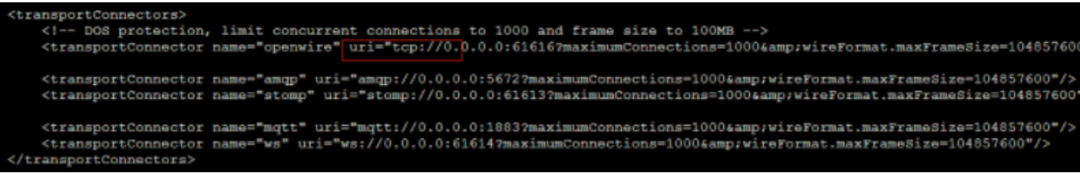

当共用zq校准电阻时,必须确保zq校准命令到任意一个die是不是重叠的,否则可能会导致不同的个die同时进行zq校准而它们可能share同一个zq resistor。甚至对于双通道die也要保证zq校准start命令可以独立的到达两个channel。

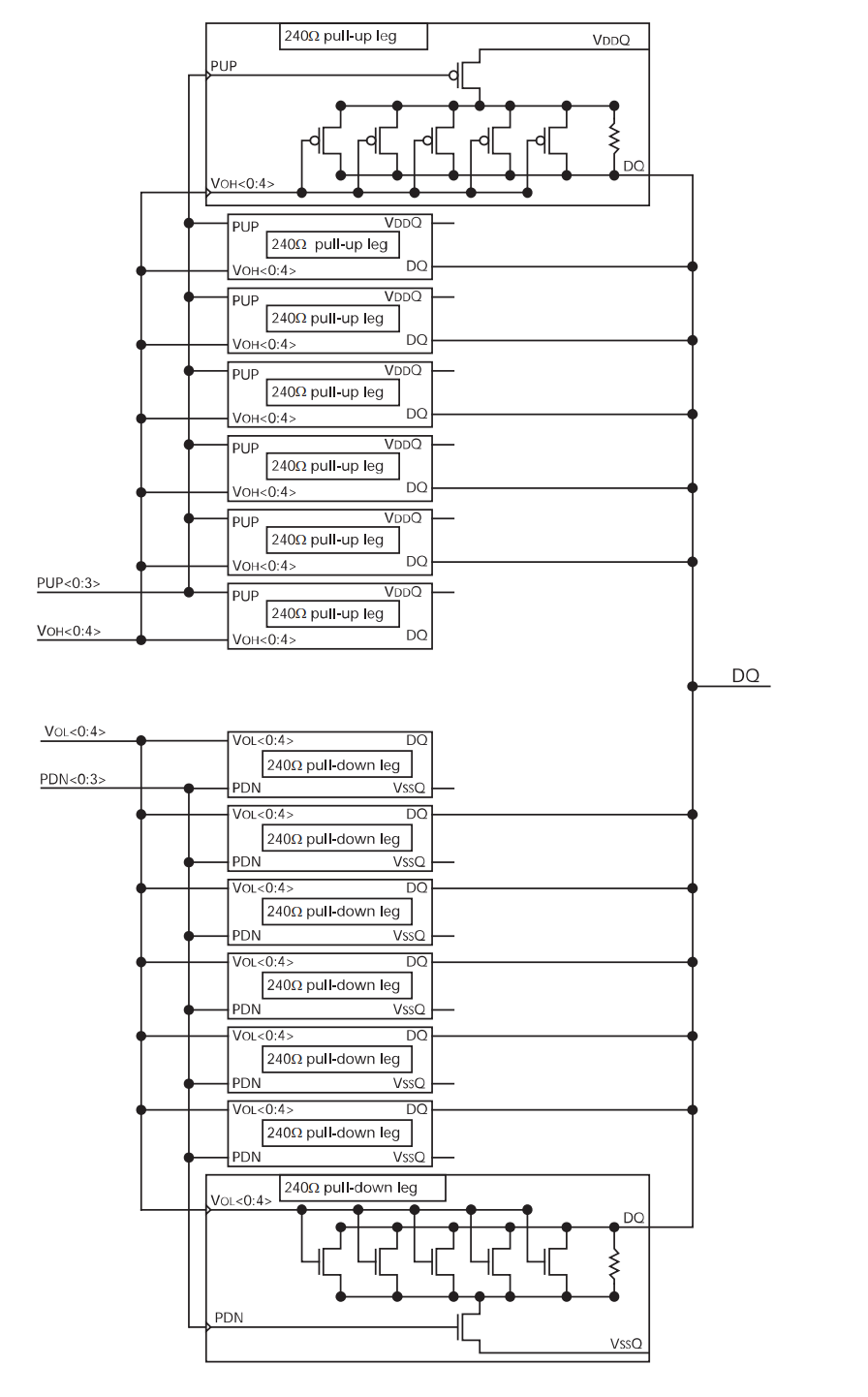

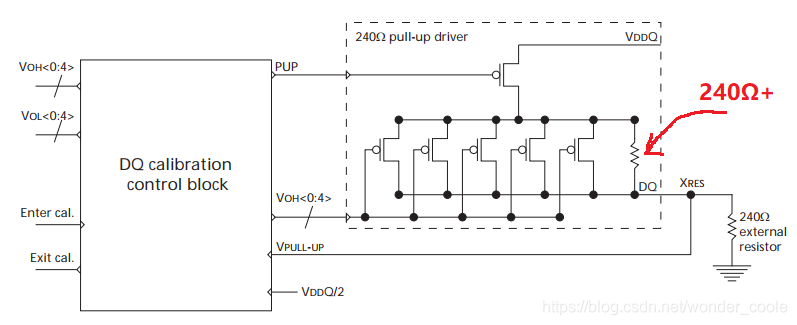

校准电路:

具体校准过程如下:

- 收到ZQ校准命令后,PUP会被驱动为低电平,使和VDDQ连接的PMOS开关打开

- 校准控制模块通过调整VOH[0:4], 来使不同的P Channel device导通

- 比较VPULL-UP和VDDQ/2的电压,当二者相等时,DQ上下两侧的电阻相等,均为240Ω,校准完成

- 记录下该电阻的VOH[0:4]的值

- 对每个上拉电阻进行校准,记录下每个电阻对应的VOH[0:4]值

- 下拉电阻校准过程类似,不多赘述。不同的是和240Ω+电阻并联的是N Channel device。

参考:

LPDDR4的训练(training)和校准(calibration)–ZQ校准(Calibration)_zq calibration-CSDN博客

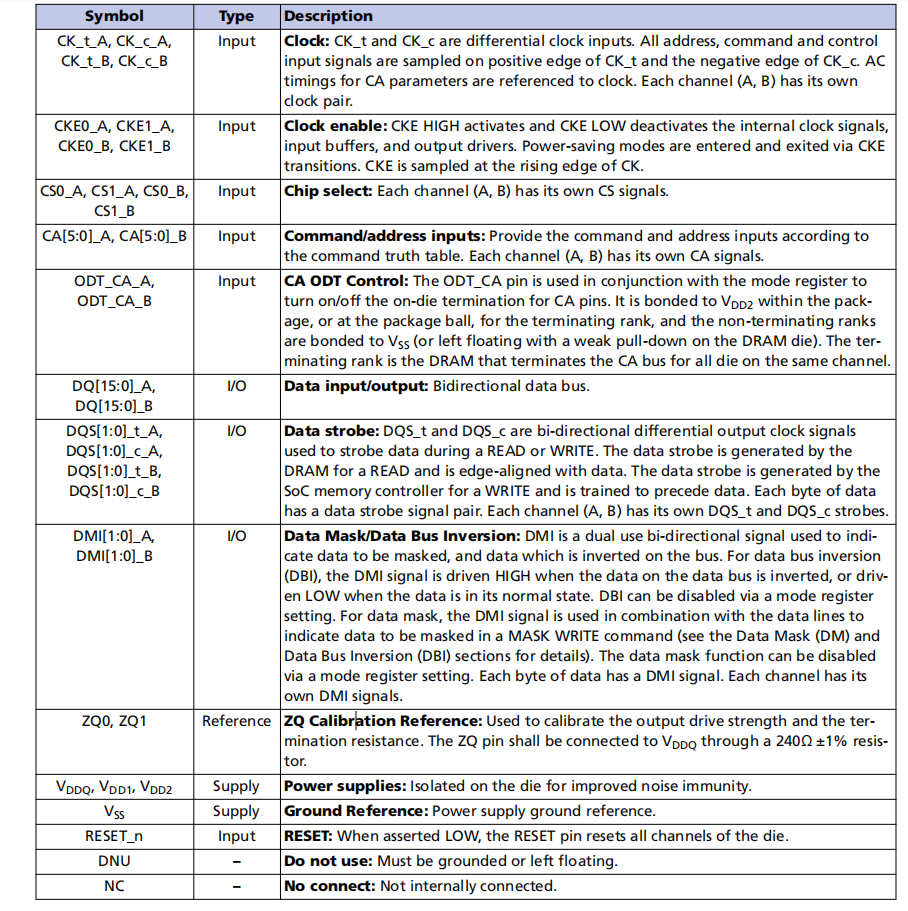

四、引脚定义

- CK_A,CK_An,CK_b,CK_bn

时钟:CK和CKn是差分时钟输入。所有地址、命令和控制输入信号都在CK的上升沿和CKn的下降沿交叉采样。CA参数的交流时序参考CK。每个通道(A和B)都有自己的时钟对。

- CKE_A,CKE_B

时钟使能:CKE高电平激活并且CKE低电平停用内部时钟电路、输入缓冲器和输出驱动器。通过CKE的转换进入和退出省电模式。CKE是命令代码的一部分。每个通道(A和B)都有自己的CKE信号。

- CS_A,CS_B

芯片选择:CS是命令代码的一部分。每个通道(A和B)都有自己的CS信号。

- CA[5:0]_A,CA[5:0]_B

命令/地址输入:CA信号根据命令真值表提供命令和地址输入。每个通道(A和B)都有自己的CA信号。

CS引脚用于选择特定的内存芯片。当CS信号为低电平时,所选芯片被激活,允许读写操作

- DQ[15:0]_A,DQ[15:0]_B

数据总线:双向数据总线。负责在内存和控制器之间传输实际的数据位

- DQS[1:0]_A DQS[1:0]_An,DQS[1:0]_B,DQS[1:0]_Bn

数据使能:DQS和DQSn是用于在读取或写入期间对数据进行节拍的双向差分输出时钟信号。数据使能由DRAM在读取操作中生成,并与数据边沿对齐。数据使能由内存控制器在写入操作中生成,并且必须在数据之前到达。每个数据字节都有一个数据使能信号对。每个通道(A和B)都有自己的DQS使能信号。

作为数据传输的时钟信号,确保数据在正确的时间被读取或写入

- ODT_CA_A,ODT_CA_B

CA ODT控制:LPDDR4X设备忽略ODT_CA引脚。ODT-CS/CA/CK功能完全通过MR11和MR22进行控制。ODT_CA引脚应连接到VDD2或VSS

- DMI[1:0]_ADMI[1:0]_B

数据掩码反转:DMI是一个双向信号,当数据总线上的数据被反转时,它被驱动为高电平;当数据处于正常状态时,它被驱动为低电平。可以通过模式寄存器设置禁用数据反转。每个数据字节都有一个DMI信号。每个通道(A和B)都有自己的DMI信号。该信号还与DQ信号一起用于向DRAM提供写数据屏蔽信息。DMI引脚的功能(数据反转或数据屏蔽)取决于模式寄存器的设置。

- ZQ

校准参考:用于校准输出驱动强度和终端电阻。每个芯片有一个ZQ引脚。ZQ引脚应通过240Ω ± 1%电

- VDD1

电源供应1:核心电源dram的core供电的,即dram内部的analog电路

- VDD2

电源供应2:核心电源dram的core供电的,即dram内部的analog电路

- VDDQ

DQ电源供应:隔离在芯片上,以提高抗干扰能力。dram的IO上供电的,如DQ/CA等IO的电路,需要的电压比较小

- VSS,VSSQ

地线

- RESET

复位:当RESETn信号为低电平时,将复位芯片的两个通道