文章目录

- 前言

- 一 CubeMx配置

- 1.1 TIM1 Mode and Configuration

- 1.2 Paramter Settings

- 二 程序代码

- 三 仿真分析

- 总结

前言

互补 PWM(Complementary PWM)是指一对逻辑状态互为反相的 PWM(脉冲宽度调制)信号。这种信号配置常见于电机控制领域,通过精确地控制桥臂上的功率晶体管(如 MOSFET 或 IGBT)的开关,来调节电机的转速和方向。

本文通过一个具体实例,详细阐述了STM32高级定时器产生互补PWM信号的原理。文章提供了生成互补PWM所需的代码实现,并利用Keil模拟器中的逻辑分析仪工具对生成的PWM信号进行了验证和分析。

一 CubeMx配置

本章将逐步引导您通过STM32CubeMX软件配置高级定时器,并在此过程中详细介绍高级定时器生成互补PWM信号的工作原理

1.1 TIM1 Mode and Configuration

(1)计数器时钟源选择:

- Internal Clock(内部时钟): APB×总线时钟,具体时钟频率可见Clock Configuration配置。

- ETR2(外部触发输入): 用于同步定时器的计数操作,可以是其他定时器输出。

这里我们选择内部时钟Internal Clock。

(2)计数器通道配置

- Output Compare(输出比较模式)

在输出比较模式下,定时器的输出比较通道可以在计数值与比较值(CCRx)相等时触发电平变化。这种模式通常用于生成具有特定频率和相位差的脉冲序列,其中 ARR 值决定了脉冲的频率,而 CCRx 值决定了脉冲的相位。

- PWM Generation(PWM模式)

在 PWM 模式下,定时器生成连续的PWM波形,其中 ARR 值决定了PWM信号的频率,CCR 值决定了信号的占空比。当定时器的计数值(CNT)小于 CCR 值时,输出高电平;当 CNT 大于 CCR 值时,输出低电平。

两者的区别可见博客链接:STM32单片机PWM模式和输出比较模式对比

这里我们选择PWM Generation CH1 CH1N,即互补PWM输出

(3)激活刹车输入

当刹车引脚输出有效电平时,PWM输出关闭。

这里我们暂且选择不激活刹车输入

1.2 Paramter Settings

(1)Counter Settings

- Prescaler(预分频系数): 对定时器总线时钟进行分频,分频后的定时器的时钟频率为: f T I M = T c l k / ( p s c + 1 ) f_{TIM}=T_{clk}/(psc+1) fTIM=Tclk/(psc+1)

- Counter Mode(计数模式):

- Center-aligned mode 1: 向下计数时产生比较中断

- Center-aligned mode 2: 向上计数时产生比较中断

- Center-aligned mode 3: 上下计数时产生比较中断

- Counter Period(计数器周期): 即计数值arr,计数范围为0~65535

定时器溢出时间:

T o u t = ( a r r + 1 ) ∗ ( p s c + 1 ) / T c l k T_{out}=(arr+1)*(psc+1)/T_{clk} Tout=(arr+1)∗(psc+1)/Tclk (向上/向下计数模式)

T o u t = ( a r r ) ∗ ( p s c + 1 ) / T c l k T_{out}=(arr)*(psc+1)/T_{clk} Tout=(arr)∗(psc+1)/Tclk (中心计数模式)

- CKD(内部时钟分频因子): 它用于进一步细分定时器的时钟频率。CKD 允许你设置时钟分频的比例,从而影响定时器的计数速度和事件触发频率。定时器最终时钟频率实际上为:

f

T

I

M

=

T

c

l

k

/

(

(

p

s

c

+

1

)

∗

C

K

D

)

f_{TIM}=T_{clk}/((psc+1)*CKD)

fTIM=Tclk/((psc+1)∗CKD)

- No Division: 不分频

- Division by 2: 二分频

- Division by 4: 四分频

- Repetition Counter(重复计数器): 当计数器发生TIMx_RCR+1次溢出事件(计数器上溢或下溢),会触发更新事件。

- auto-reload-preload (自动重装载):

- 开启预装功能: 此时影子寄存器的数据更新必须且只能通过更新事件实现从预装寄存器到影子寄存器的数据拷贝。

- 关闭预装功能: 此时用户修改预装寄存器的数据后会立即被拷贝进影子寄存器【实际寄存器】。也就是说,此时我们用户操作预装寄存器就相当于访问实际影子寄存器。

我们配置定时器的预分频系数(Prescaler)为 64 - 1,并且选择内部时钟分频因子(CKD)为不分频模式。假设定时器的 APB1 总线时钟频率( T c l k T_{clk} Tclk)为64MHz,那么定时器的实际频率( f T I M f_{TIM} fTIM)计算如下: f T I M = T c l k ( P r e s c a l e r + 1 ) × C K D = 64 M H z ( 64 + 1 ) × 1 = 1 M H z f_{TIM} = \frac{T_{clk}}{(Prescaler + 1) \times CKD} = \frac{64MHz}{(64 + 1) \times 1} = 1MHz fTIM=(Prescaler+1)×CKDTclk=(64+1)×164MHz=1MHz计数模式(Counter Mode)被设置为中心对齐模式 3(Center-aligned mode 3)。在这个模式下,计数器的周期(ARR)被设置为 1000。因此,定时器向上计数和向下计数的时间各为 1 ms。重复计数器(Repetition Counter)被设置为 0,表示不使用重复计数功能。

(2)Trigger Output(TRGO)Parameters

- Master/Slave Mode: 在主模式下,定时器控制其他从定时器的同步操作。主定时器可以发送触发信号给连接的从定时器,从而同步启动、停止或重新同步它们的操作。在从模式下,定时器接收来自主定时器的触发信号,并根据这些信号来同步其操作。

- Trigger Event Selection: 当定时器的定时时间到达的时候输出一个信号(如:定时器更新产生TRGO信号来触发ADC的同步转换)

这里我们选择Reset(复位事件)

(3)Break And Dead Time management - BRK Configuration

- BRK State(刹车状态): 用于启用或禁用刹车功能。当刹车功能被启用时,如果检测到刹车事件(如外部引脚的触发或软件触发),定时器的输出将被立即禁用,从而实现快速停止。

- BRK Polarity(刹车极性): 用于配置刹车输入信号的极性。根据硬件设计和应用需求,刹车输入可以配置为在高电平(High)或低电平(Low)触发。

这里我们按照默认的配置来

(4)Break And Dead Time management - Output Configuration

- Dead Time(死区时间): 指的是在互补 PWM 信号中,一个输出关闭和另一个输出打开之间的时间间隔。

这里我们把死区时间设置为100,结合前文计算出的定时器实际频率 f T I M = 1 M H z f_{TIM}=1MHz fTIM=1MHz,可知死区时间为0.1ms

(5)PWM Generation Channel 1 and 1N

- Mode :

- PWM mode1: 向上计数时,一旦TIMx_CNT<TIMx_CCR1时通道1为有效电平,否则为无效电平;在向下计数时,一旦TIMx_CNT>TIMx_CCR1时通道1为无效电平(OC1REF=0),否则为有效电平(OC1REF=1)。

- PWM mode2: 向上计数时,一旦TIMx_CNT<TIMx_CCR1时通道1为无效电平,否则为有效电平;在向下计数时,一旦TIMx_CNT>TIMx_CCR1时通道1为有效电平(OC1REF=0),否则为无效电平(OC1REF=1)。

- Pulse : 即寄存器CCR的值,可以控制PWM的占空比

- CH Polarity(通道极性):

- High: 高电平为有效电平

- Low: 低电平为有效电平

要结合PWM mode理解通道极性,可参考链接PWM输出极性高低的区别以及TIM_OCMode_PWM1和TIM_OCMode_PWM2的区别

- CHN idle State: 用于设置定时器的输出比较通道在定时器处于空闲状态时的输出状态。

- Set: 在定时器空闲时,输出通道输出高电平。

- Reset: 在定时器空闲时,输出通道输出低电平。

在定时器的 PWM 配置中,我们将比较捕获寄存器(CCR)的值设置为 500,而其他参数则保留为默认设置。结合之前为自动重载寄存器(ARR)设置的周期值为 1000 ,我们可以计算出 PWM 信号的占空比为 50%。

二 程序代码

完成CubeMx配置后,生成代码,在主函数中添加如下程序,以打开PWM输出通道和互补输出通道。

HAL_TIM_PWM_Start(&htim1,TIM_CHANNEL_1);

HAL_TIMEx_PWMN_Start(&htim1,TIM_CHANNEL_1);

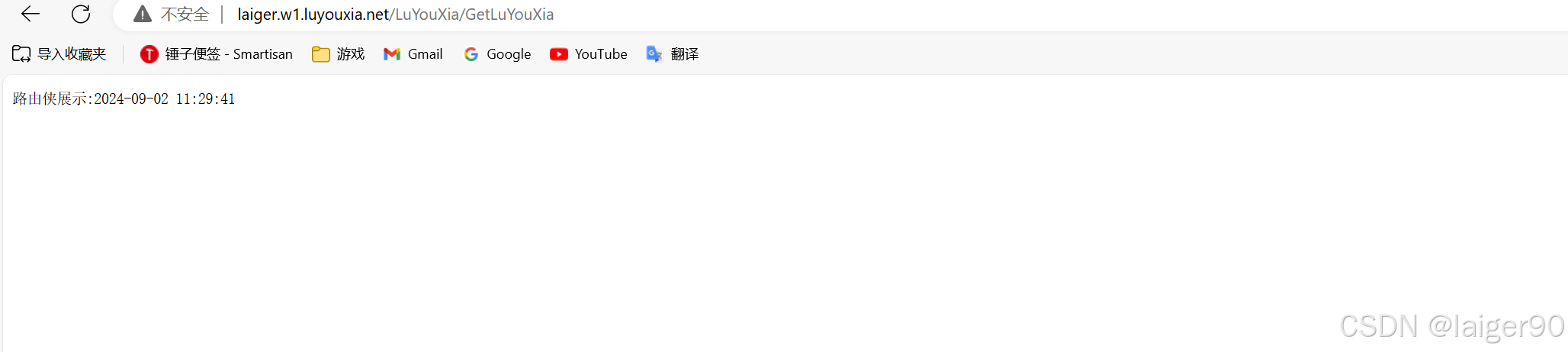

三 仿真分析

使用Keil Simulator,将互补PWM输出IO口添加到Logic Analyzer中,具体步骤可参考我之前的博客:Keil的debug模式下使用simulator,用逻辑分析仪观察IO口输出波形的变换

注:开始仿真前,要确保晶振频率设置正确

仿真波形如下:

- 在中心对齐模式下,定时器的自动重载寄存器(ARR)设置为1000,这使得PWM信号的周期为2毫秒,与仿真图所示一致。

- 在定时器配置中,若计数器周期(ARR)设为1000,且死区时间设为100个定时器时钟周期,则对于1MHz的定时器频率,死区时间实际为0.1毫秒,与仿真图结果一致。

- 在中心对齐模式下,定时器的自动重载寄存器(ARR)配置为1000,捕获比较寄存器(CCR)设置为500,产生50%的PWM占空比。若仿真图显示高电平持续时间与死区时间之和为1毫秒,则与设定的周期相符,结果验证一致。

总结

本文通过实例深入解析了STM32高级定时器产生互补PWM信号的机制,并提供了相应的代码实现。同时,利用Keil模拟器的逻辑分析仪对PWM信号进行了验证,确保了分析的准确性

![[C#学习笔记]注释](https://i-blog.csdnimg.cn/direct/50035df5ad1a429eb4a9650079b02afc.png)