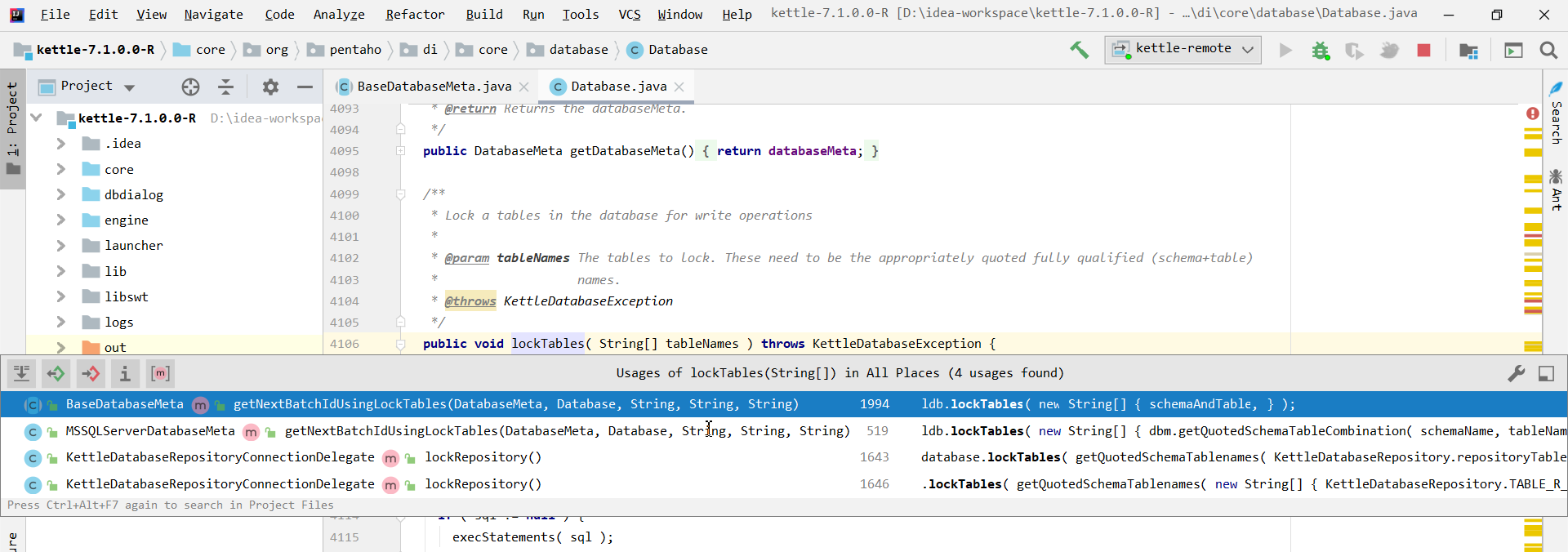

目录

- 1 时钟电路概述

- 2 时钟晶振电路

- 2.1 需求分析

- 2.2 晶振选型(Datasheet表5-7解读)

- 2.3 设计晶振电路(表4-1、图5-4)

1 时钟电路概述

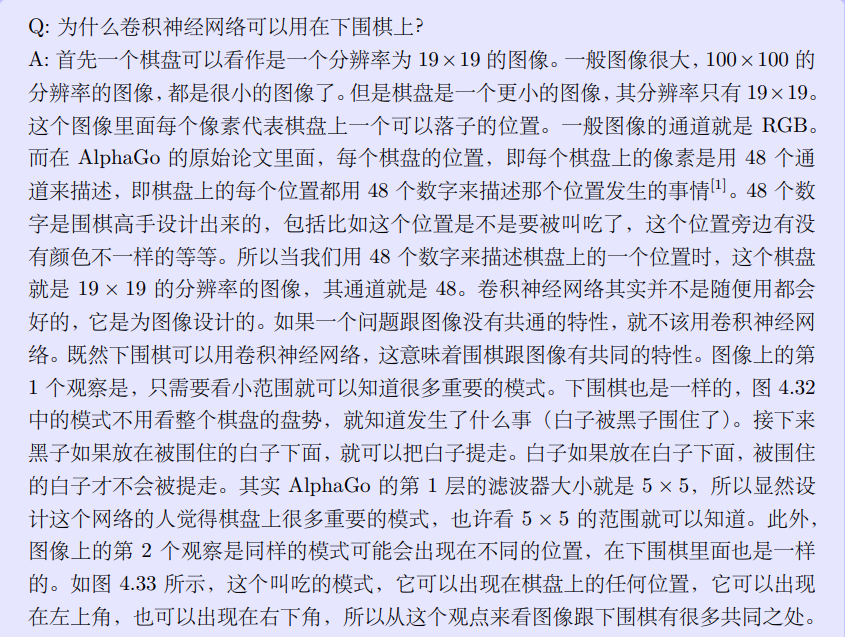

时钟电路是一种用于产生稳定、周期性脉冲信号的电子电路。它通常由晶体振荡器和相关逻辑电路组成。晶体振荡器负责产生高精度的振荡信号,而逻辑电路则负责对振荡信号进行分频、缓冲和分配,以满足不同部件的时序要求。

时钟信号可以看作是系统中的心跳,指示了系统的工作节奏和时间轴。它驱动各个部件按照特定的时间序列执行操作,确保数据的可靠传输和处理。

(1) 时钟信号生成

时钟电路通过晶体振荡器来生成稳定的时钟信号。晶体振荡器利用晶体的振荡特性,将输入电能转换成精确的周期性振荡信号。这个振荡信号的频率和稳定性对于系统的工作效果至关重要。

(2) 时钟信号分频

时钟电路中的逻辑电路通过分频器将高频振荡信号进行分频,以满足不同部件的时序需求。分频器可以将高频信号按照预设比例降低频率,生成相应的分频信号,并将其分配给各个部件。

(3) 时钟信号缓冲

时钟信号经过分频后,可能会变得较弱。为了保证信号传输的可靠性和稳定性,时钟电路使用缓冲器对信号进行放大和整形。缓冲器能够提供足够的驱动能力,确保时钟信号能够准确地传递给每个部件。

(4) 时钟信号分发

生成的时钟信号由时序控制器分发给系统中的各个部件。分发过程可以通过时钟分频、时钟缓冲和时钟树等方式进行。时序控制器确保时钟信号能够准确地传递到每个部件,以保持整个系统的同步性和稳定性。

(5) 时间顺序控制

时序控制器根据预设的时间顺序,控制各个操作的触发和执行。它使用计数器、触发器等元件来实现对操作的精确控制。时序控制器可以根据操作的需求设定触发条件、触发时机和持续时间,确保操作按照正确的时间顺序顺利执行。

(6) 时序同步和延迟控制

时序控制器负责同步各个部件之间的时钟信号和操作。它确保不同部件之间的时钟相位一致,并能够在合适的时间点触发操作。时序控制器还可以控制延迟时间,以满足不同操作之间的时序要求,确保数据的准确传输和处理。

2 时钟晶振电路

2.1 需求分析

(1) 理解应用场景:分析时钟电路在系统中的作用,包括工作频率、精度要求、温度范围、功耗等。

(2) 时钟源选择:根据需求选择适当的时钟源,如晶振(Crystal Oscillator)、陶瓷谐振器(Ceramic Resonator)、VCXO(压控晶体振荡器)、温补晶振(TCXO)等。

a) 晶振:由石英晶体构成,具有非常高的频率稳定性和精度。

频率稳定度高,通常在±20 ppm(百万分之二十)以内。

温度范围较宽,能在较宽的温度范围内保持稳定。

成本相对较高。

应用场景:适用于对频率精度要求较高的场合,如计时设备、通信设备、计算机等。

b) 陶瓷谐振器:由陶瓷材料制成,通常带有内置的振荡电路。

频率稳定性较差,通常在±0.5%左右。

成本较低,体积较小。

适合低成本、对频率精度要求不高的应用。

应用场景:适用于成本敏感、对频率精度要求不高的场合,如简单的微控制器应用、家用电器等。

c) 压控晶体振荡器:类似于晶振,但增加了一个电压控制接口,允许通过改变输入电压来调整输出频率。

频率可调,通过外部控制电压实现。

精度和稳定性略低于标准晶振。

应用场景:适用于需要频率调节的场合,如无线通信系统中的频率合成器、信号发生器等。

d) 温补晶振:在晶振的基础上增加了温度补偿电路,以减少温度变化对频率的影响。

频率稳定性非常高,即使在温度变化的环境下也能保持稳定。

成本高于普通晶振。

应用场景:适用于对频率稳定性要求极高,且工作环境温度变化较大的场合,如GPS系统、军事通信设备、航空航天设备等。

选择建议:

成本敏感且对频率精度要求不高:陶瓷谐振器。

标准应用,需要较高的频率精度:晶振。

需要频率可调节的应用:VCXO。

要求极高的频率稳定性和温度补偿:TCXO。

在选择时,还需考虑其他因素,如电源电压、输出类型、封装尺寸、工作温度范围等,以确保所选元件满足具体应用的需求。

(3) 电气特性:明确时钟电路的电气特性,如输出类型(CMOS、LVDS等)、驱动能力、占空比、时钟边沿特性等。

2.2 晶振选型(Datasheet表5-7解读)

(1) 频率: 芯片推荐使用25MHz的晶振,以确保与内部时钟频率匹配。

(2) 振荡模式: 选择基频振荡模式,以保证稳定性和可靠性。如基频表示晶体以最低谐振频率工作

PS:

基频震荡是晶体振荡器最常用的振荡模式。晶体以最低谐振频率(基频)振荡,提供最低的相位噪声和最高的频率稳定性。基频振荡器通常具有最高的Q因子(品质因数),意味着它们具有较窄的带宽和较好的频率选择性。

除此之外,震荡模式还有:三次谐波、五次谐波、泛音、扩展基频等。

三次谐波振荡器的振荡频率是晶体基频的三倍:相较于基频振荡器,三次谐波振荡器的体积可以更小,但可能具有稍高的相位噪声。

五次谐波振荡器的振荡频率是晶体基频的五倍。与三次谐波类似,五次谐波振荡器也具有较小的体积,但相位噪声性能可能不如基频振荡器。

泛音振荡模式指的是晶体振荡在基频的整数倍频率上。泛音振荡器可能具有不同的尺寸和性能特点,但通常相位噪声性能不如基频振荡器。

扩展基频是一种介于基频和泛音之间的振荡模式。扩展基频振荡器可能在某些应用中提供比基频更好的性能。

基频振荡器因其优异的频率稳定性和低相位噪声而广泛应用于需要高精度时钟的应用。泛音振荡器则可能因为体积小而在某些空间受限的应用中受到青睐。选择哪种振荡模式取决于具体的应用需求、尺寸限制、成本考虑以及性能要求。

(3) 校准负载电容: 为了达到正确的振荡频率,晶体振荡器需要特定的负载电容值。这里给出的推荐的电容值范围是12~32pF的负载电容。

(4) 校准容差: 晶体振荡器频率的允许偏差,表示在特定温度范围内的频率稳定性。在25℃±3℃时,校准容差为±50 ppm。

(5) 工作温度范围: 选择-20℃至+85℃的工作温度范围,以适应不同的应用环境。

(6) 频率稳定性: 指在工作温度范围内晶体振荡器的频率偏差,±50 ppm,参考25℃时的频率。

(7) 工作驱动电平: 晶体振荡器正常工作所需的最小驱动电平,选择>100 μW的驱动等级,以保证晶振正常工作。

(8) 最大驱动电平: 晶体振荡器能够承受的最大驱动电平,超过300 μW可能会损坏振荡器。

(9) 等效串联电阻: <30 Ohm。晶体振荡器内部电阻的等效值,太大会影响信号的传输质量。

(10) 并联电容: ❤️ pF。晶体振荡器内部的并联电容值,对振荡频率有影响。

(11) 老化: 晶体振荡器随时间老化导致的频率变化率,在25℃下,第一年内变化<±3 ppm。

(12) 存储温度: 40至+85℃。晶体振荡器在不使用时的推荐存储温度范围。

(13) 绝缘电阻: >500 Mohm。晶体振荡器的绝缘性能。

2.3 设计晶振电路(表4-1、图5-4)

供电引脚:通常标记为AVDD33_XTAL,这是为晶体振荡器提供3.3V电源的引脚。

输入引脚:通常标记为XTAL_IN,这是晶体振荡器的输入端,接收外部时钟信号。

输出引脚:通常标记为XTAL_OUT,这是晶体振荡器的输出端,提供时钟信号给AN7563PT的其余部分。

负载电容:电路图可能指示在XTAL_IN和XTAL_OUT之间需要连接的负载电容,这些电容与晶体振荡器一起工作,以确保振荡频率的稳定性。负载电容的大小会影响晶振的振荡频率。通常情况下,负载电容越大,晶振的振荡频率越低。

在晶振的两个引脚和 GND 之间各连接一个电容,用于滤波和稳定振荡。

2.4 注意事项

电源: 确保晶振电路的电源稳定,可以使用去耦电容进行滤波。

地线: 使用单点接地,并保证地线连接良好。

干扰: 避免晶振电路周围有强干扰源,例如电源、电机等。

布局: 晶振电路应尽量远离高速信号线,晶振和电容应尽量靠近芯片放置,并使用短而粗的走线连接,以减少干扰和损耗。

2.5 测试

功能测试: 确保晶振电路能够正常起振,并输出稳定的时钟信号。

性能测试: 测试晶振电路的频率稳定性和抗干扰能力。

2.6 参考电路

文档中提供了晶振电路的参考图,可以参考该图进行设计。