接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第7章 PCIe总线的数据链路层与物理层(3)

7.1 数据链路层的组成结构

7.1.1 数据链路层的状态

数据链路层需要通过物理层监控PCIe链路的状态,并维护数据链路层的“控制与管理状态机”(Data Link Control and Management State Machine,DLCMSM)。DLCMSM状态机可以从物理层获得以下与当前PCIe链路相关的状态。

- DL_Inactive状态

物理层通知数据链路层当前PCIe链路不可用。在当前PCIe链路的对端没有连接任何PCIe设备,或者没有检测到对端设备的存在时,数据链路层处于该状态。

- DL_Init状态

物理层通知数据链路层当前PCIe链路可用,且物理层正处于链路初始化状态。此时数据链路层不能接收或者发送TLP或DLLP。此时PCIe链路首先需要初始化VC0的流量控制机制,然后再对其它虚通路进行流量控制的初始化。

- DL_Active状态

当前PCIe链路处于正常工作模式。此时物理层已完成PCIe链路训练或者重训练。

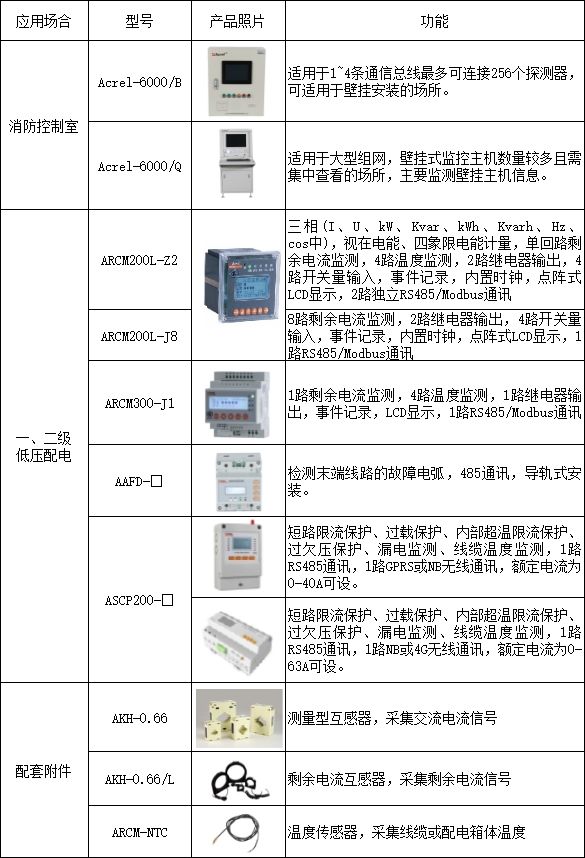

DLCMSM状态机的迁移模型如图7-3所示:

DLCMSM状态机除了可以使用上述状态位,从物理层获得当前PCIe链路状态外,还可以使用以下状态位,向事务层通知数据链路层所处的状态。事务层通过这些状态位获知数据链路层所处的工作状态。

- DL_Down

数据链路层处于该状态时,表示在PCIe链路的对端没有发现其它设备。当数据链路层处于DL_Inactive状态时,该状态位有效。值得注意的是,DL_Down有效时,并不意味着对端不存在物理设备。数据链路层仅是使用该状态位通知事务层,暂时没有从对端中发现PCIe设备,需要进一步检测。

- DL_Up

数据链路层处于该状态时,表示在PCIe链路的对端连接了其它设备。当数据链路层处于DL_Active状态时,该状态位有效。

更多内容请看下回。