SPI外设简介

STM32芯片内部集成了SPI片上外设,可由硬件自动执行时钟生成、数据收发等功能,减轻CPU负担。对于STM32F103C8T6,其SPI资源有SPI1、SPI2。

一些参数配置:

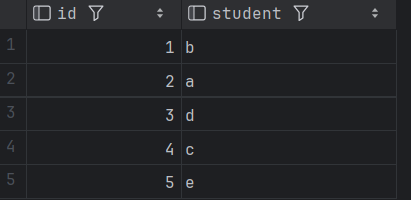

| 8位/16位数据帧 |

| 高位先行/低位先行 |

| 时钟频率:PCLK/(2,4,8,16,32,64,128,256) |

| 支持多主机模型、主或从操作 |

| 可精简为半双工/单工通信 |

| 支持DMA |

| 兼容I2S协议 |

【注意】SPI模块的时钟就是由外设时钟PCLK分频(分频系数如上表所示)而来的,APB1的PCLK是36MHz,APB2的PCLK是72MHz;其中SPI1挂在APB2总线上,SPI2挂在APB1总线上。

SPI内部框图

如图,左上角的移位寄存器,观察箭头发现,右边的MOSI数据一位一位地移出去,左边的MISO数据一位一位地移入左边的数据高位,显然上图的移位寄存器为右移状态(低位先行)。

移位寄存器的右下角处有一个LSBFIRST控制位,这一位用于控制是低位先行还是高位先行(给0,高位先行---MSB;给1,低位先行---LSB)。

再注意左边的方框,里面将MOSI和MISO做了个交叉,是用来进行主从模式引脚变换的。因为SPI外设既可以做主机,又可以做从机。做主机时,交叉就不使用;做从机时,MOSI为SI,作为从机输入、MISO为SO,作为从机输出(均走交叉的路线)。

对于接收缓冲区和发送缓冲区,实际上就是接收数据寄存器RDR和发送数据寄存器TDR,用于实现连续发送。

对于右下角CR1寄存器:

| SPE | SPI使能 |

| BR2 | 用来控制分频系数 000~111分别代表2~256 |

| BR1 | |

| BR0 | |

| MSTR | 配置主从模式:1主、0从 |

| CPOL | 用来选择SPI的4种模式 |

| CPHA |

对于SR状态寄存器,主要关注TXE位(发送空)和RXNE位(接收非空);对于CR2寄存器,主要是配置一些使能,例如中断使能、DMA使能。

对于NSS引脚,在一主多从模式下,用GPIO来模拟是最佳选择。

【注意】当写入DR时,TXE标志位自动置位;读取SPI数据寄存器也可以自动清除RXEN;

附主模式全双工连续传输时序图:

附非连续传输发送时序图: