一、绪论

网上很多文章都讲述了Xilinx FPGA在线升级即回退的优势,在这里仅简述一遍。优势在于可不拆机的情况下改变FPGA的功能,可进行产品迭代。回退的优势是避免升级过程中一些突发情况导致板卡成为废板。至少Golden里面包含了可进行升级的部分代码。

二、通信架构

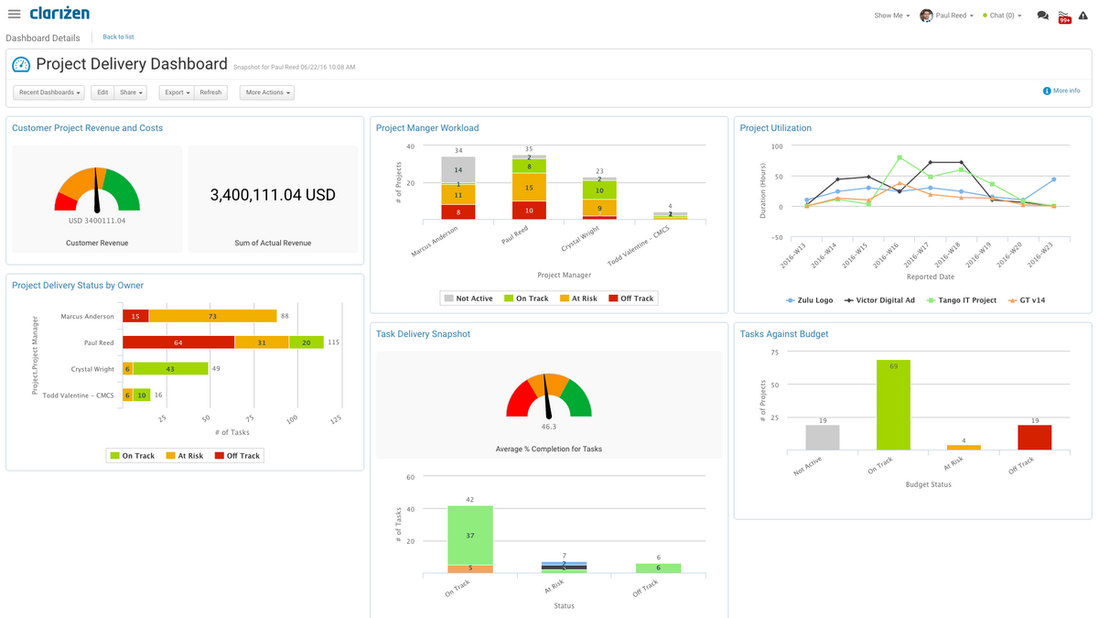

FPGA上电后,会从FLASH的0地址中根据模式进行读取配置数据,进而实现FPGA的加载启动。因此实现FPGA在线升级的本质就是FLASH的控制,为此有上图所示的通信架构。

PC为上位机,用来监控整个整机流程。FPGA内部的decode模块实现了对上位机的解码,并将控制命令传输到falsh_ctrl模块,falsh_ctrl模块则是实现了flash的所用控制功能。encode模块则是实现了升级状态的上传,用于上位机检测是否升级完成。

三、升级思路

1.整体思路

在线升级就是更改flash的内容,在对flash内容改写前需要对falsh进行擦除,因为falsh只能同1变成0,在擦除时是讲内存数据全部变成1。

然后就需要将升级数据从上位机写入到flash中,这部分是由你的通信方式决定,大部分时间会在这个阶段被浪费掉,因此通信速率决定了升级时间。我测试过使用UART进行升级,一个3M的升级文件大概需要仅半个小时。

为了验证数据正确被写入,还需要把写入的升级数据回读回来,与升级文件进行对比,只有回读的数据与写入的相同才认为升级成功。

综上,升级整体思路如下:

- 擦除flash

- 写入升级数据

- 回读升级数据,并与升级文件做对比

2. 传统的升级思路

该部分升级思路是按照整体升级思路进行升级。首先进行擦除,其次将升级数据写入到flash中,紧接着就是将升级数据在回读到上位机上,通过上位机与升级文件进行对比,从而判断升级是否成功。

3.改良版升级思路

该部分主要是为了降低升级的时间。传统的升级思路消耗的时间主要是在擦除过程、通信过程,还有就是文件对比过程。FPGA的速度肯定是比PC快的。把大部分时间用FPGA做可节省大量的时间。

-

从擦除过程中节省

擦除分全擦除、block擦除等。可根据文件大小,只擦除指定的block块。 -

从通信速度上节省

选择一个比较块的通信方式,如PCIE、GTX等。作者实测过使用UART升级一个3M多的文件大约需要半个小时。 -

校验方式进行改进

传统的是将所有写入的数据再回读到上位机,并于升级文件做对比,这将消耗大量的通信时间以及对比时间。可在软件下发升级文件时先对升级文件做CRC校验(soft_crc),FPGA接收到升级文件后再对升级数据进行一次CRC校验(fpga_crc),在回读flash时再对flash数据进行CRC校验(flash_crc)。最后对比这三个数据是否相等,仅有三个同时相等才认为升级成功。并且通过这种方式还可以判断升级过程中是哪些原因导致的升级失败。