(1)顶层代码:

module IIC_EEPROM(

input wire clk ,

input wire reset_n ,

input wire key_r ,

input wire key_w ,

output wire IIC_SCL ,

inout wire IIC_SDA

);

wire key_rd ;

wire key_wr ;

wire [7:0] fifo_rd_data;

wire IIC_start ;

wire wr_en ;

wire rd_en ;

wire [15:0] byte_addr ;

wire [7:0] wr_data ;

wire IIC_clk ;

wire IIC_end ;

wire [7:0] rd_data ;

key_filter key_w_filter(

.clk ( clk ),

.reset_n ( reset_n ),

.key_in ( key_w ),

.key_p_flag ( key_wr ),

.key_r_flag ( ),

.key_state ( )

);

key_filter key_r_filter(

.clk ( clk ),

.reset_n ( reset_n ),

.key_in ( key_r ),

.key_p_flag ( key_rd ),

.key_r_flag ( ),

.key_state ( )

);

IIC_rw_data IIC_rw_data_inst(

.clk (clk ),

.reset_n (reset_n ),

.key_rd (key_rd ),

.key_wr (key_wr ),

.IIC_clk (IIC_clk ),

.IIC_end (IIC_end ),

.rd_data (rd_data ),

.fifo_rd_data (fifo_rd_data ),

.IIC_start (IIC_start ),

.wr_en (wr_en ),

.rd_en (rd_en ),

.byte_addr (byte_addr ),

.wr_data (wr_data )

);

IIC_ctrl IIC_ctrl_inst(

.clk (clk ),

.reset_n (reset_n ),

.IIC_start (IIC_start ),

.wr_en (wr_en ),

.rd_en (rd_en ),

.byte_addr (byte_addr ),

.wr_data (wr_data ),

.addr_num (1'd1 ),

.IIC_SCL (IIC_SCL ),

.IIC_SDA (IIC_SDA ),

.IIC_clk (IIC_clk ),

.IIC_end (IIC_end ),

.rd_data (rd_data )

);

endmodule

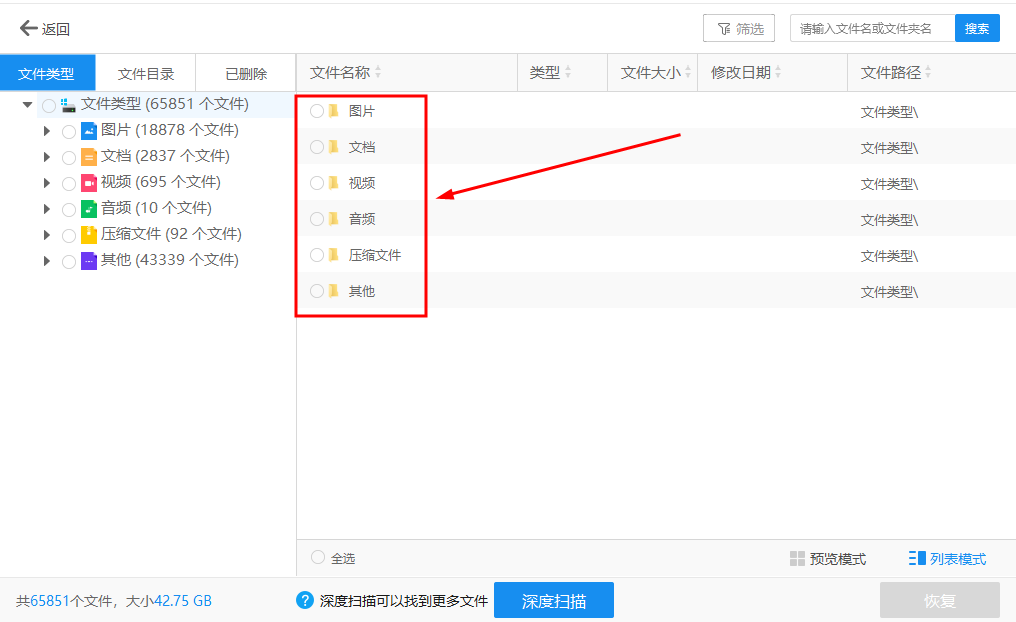

(2)顶层RTL视图:

(3)仿真代码:

`timescale 1ns / 1ps

module IIC_EEPROM_tb;

reg clk ;

reg reset_n ;

reg key_r ;

reg key_w ;

wire IIC_SCL ;

wire IIC_SDA ;

initial clk = 1'd1;

always #10 clk = ~ clk;

defparam IIC_EEPROM_inst.key_w_filter.CNT_MAX = 5;

defparam IIC_EEPROM_inst.key_r_filter.CNT_MAX = 5;

defparam IIC_EEPROM_inst.IIC_rw_data_inst.CNT_WAIT_MAX = 10_000;

initial begin

reset_n <= 1'd0;

key_r <= 1'd1;

key_w <= 1'd1;

#21;

reset_n <= 1'd1;

#1000;

key_r <= 1'd1;

key_w <= 1'd0;

#400;

key_r <= 1'd1;

key_w <= 1'd1;

#200_000_000;

key_r <= 1'd0;

key_w <= 1'd1;

#400;

key_r <= 1'd1;

key_w <= 1'd1;

#400_000_000;

$stop;

end

IIC_EEPROM IIC_EEPROM_inst(

.clk ( clk ),

.reset_n ( reset_n ),

.key_r ( key_r ),

.key_w ( key_w ),

.IIC_SCL (IIC_SCL ),

.IIC_SDA (IIC_SDA )

);

M24LC64 M24LC64_inst(

.A0 (1'd1 ),

.A1 (1'd1 ),

.A2 (1'd0 ),

.WP (1'd0 ),

.SDA (IIC_SDA ),

.SCL (IIC_SCL ),

.RESET (~reset_n )

);

endmodule

(4)仿真波形(官网提供的仿真模型不太理想,没有读取理想的数据):

(5)顶层加入ILA ip核进行在线逻辑分析: